NSC 5962-9165401VYA, 5962-9165401VXA, 5962-9165401MYA, 5962-9165401MXA Datasheet

August 1998

100355

Low Power Quad Multiplexer/Latch

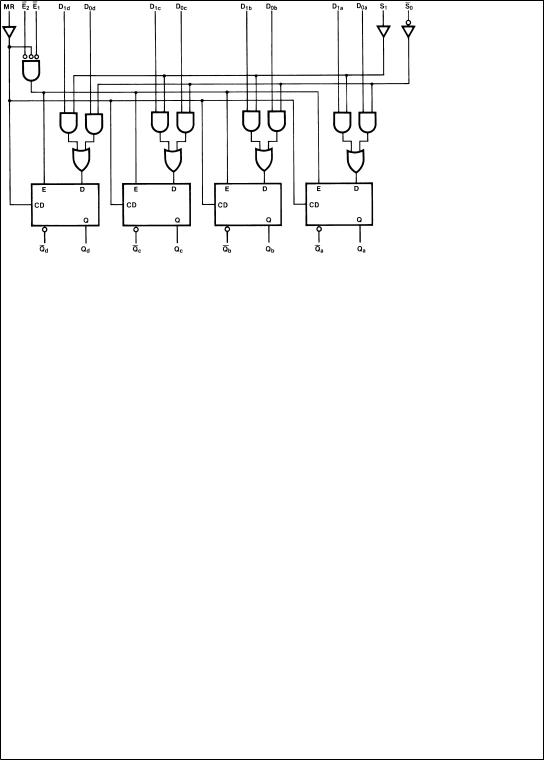

General Description

The 100355 contains four transparent latches, each of which can accept and store data from two sources. When both Enable (En) inputs are LOW, the data that appears at an output is controlled by the Select (Sn) inputs, as shown in the Operating Mode table. In addition to routing data from either D0 or D1, the Select inputs can force the outputs LOW for the case where the latch is transparent (both Enables are LOW) and can steer a HIGH signal from either D0 or D1 to an output. The Select inputs can be tied together for applications requiring only that data be steered from either D0 or D1. A positive-going signal on either Enable input latches the out-

puts. A HIGH signal on the Master Reset (MR) input overrides all the other inputs and forces the Q outputs LOW. All inputs have 50 kΩ pulldown resistors.

Features

nGreater than 40% power reduction of the 100155

n2000V ESD protection

nPin/function compatible with 100155

nVoltage compensated operating range = −4.2V to −5.7V

nStandard Microcircuit Drawing (SMD) 5962-9165401

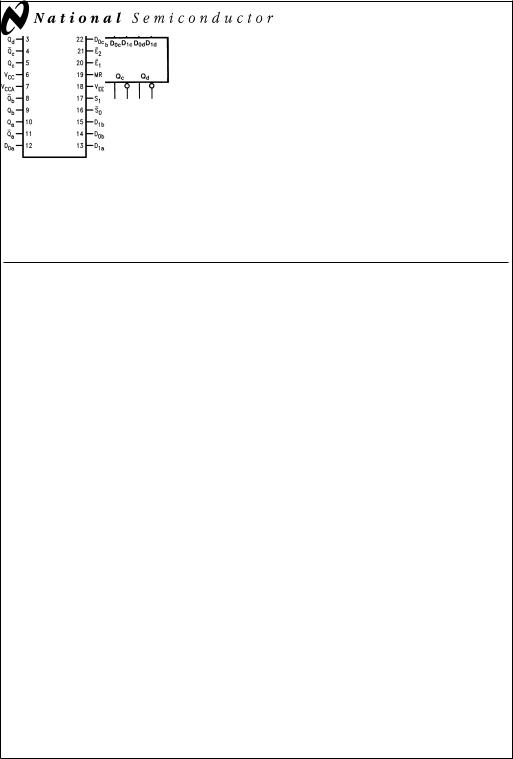

Logic Symbol

|

|

|

|

|

|

|

|

|

|

DS100294-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin Names |

Description |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

Enable Inputs (Active LOW) |

|||

|

|

E |

1, |

E |

||||||

|

|

|

|

|

Select Inputs |

|||||

|

S |

0, S1 |

||||||||

|

MR |

Master Reset |

||||||||

|

Dna±Dnd |

Data Inputs |

||||||||

|

Qa±Qd |

Data Outputs |

||||||||

|

|

|

|

d |

Complementary Data Outputs |

|||||

|

Q |

a±Q |

||||||||

Connection Diagrams

24-Pin DIP |

24-Pin Quad Cerpak |

DS100294-3

DS100294-2

Multiplexer/Latch Quad Power Low 100355

© 1998 National Semiconductor Corporation |

DS100294 |

www.national.com |

Logic Diagram

DS100294-5

www.national.com |

2 |

Operating Mode Table

|

|

|

Controls |

|

|

|

Outputs |

|||

|

|

|

|

|

|

|

|

|

|

|

|

E |

1 |

|

E |

2 |

S1 |

|

S |

0 |

Qn |

|

H |

|

X |

X |

|

X |

Latched (Note 1) |

|||

|

X |

|

H |

X |

|

X |

Latched (Note 1) |

|||

|

L |

|

L |

L |

|

L |

D0x |

|||

|

L |

|

L |

H |

|

L |

D0x + D1x |

|||

|

L |

|

L |

L |

|

H |

L |

|||

|

L |

|

L |

H |

|

H |

D1x |

|||

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

Note 1: Stores data present before E went HIGH

Truth Table

|

|

|

|

|

|

Inputs |

|

|

|

|

|

|

|

Outputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

|

E |

1 |

E |

2 |

S1 |

S |

0 |

D1x |

D0x |

|

Q |

x |

Qx |

H |

|

X |

X |

X |

X |

X |

X |

|

H |

L |

||||

L |

|

L |

L |

H |

H |

H |

X |

|

L |

H |

||||

L |

|

L |

L |

H |

H |

L |

X |

|

H |

L |

||||

L |

|

L |

L |

L |

L |

X |

H |

|

L |

H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

L |

L |

L |

X |

L |

|

H |

L |

||||

L |

|

L |

L |

L |

H |

X |

X |

|

H |

L |

||||

L |

|

L |

L |

H |

L |

H |

X |

|

L |

H |

||||

L |

|

L |

L |

H |

L |

X |

H |

|

L |

H |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

L |

H |

L |

L |

L |

|

H |

L |

||||

L |

|

H |

X |

X |

X |

X |

X |

Latched (Note 1) |

||||||

L |

|

X |

H |

X |

X |

X |

X |

Latched (Note 1) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

www.national.com |

Loading...

Loading...