NSC 5962R8960101SSA, 5962R8960101SRA, 5962R8960101S2A, 5962R8960101BSA, 5962R8960101BRA Datasheet

...

September 1998

54AC574 · 54ACT574

Octal D-Type Flip-Flop with TRI-STATE® Outputs

General Description

The 'AC/'ACT574 is a high-speed, low power octal flip-flop with a buffered common Clock (CP) and a buffered common Output Enable (OE). The information presented to the D inputs is stored in the flip-flops on the LOW-to-HIGH Clock (CP) transition.

The 'AC/'ACT574 is functionally identical to the 'AC/'ACT374 except for the pinouts.

Features

nICC and IOZ reduced by 50%

nInputs and outputs on opposite sides of package allowing easy interface with microprocessors

nUseful as input or output port for microprocessors

nFunctionally identical to 'AC/'ACT374

nTRI-STATE outputs for bus-oriented applications

nOutputs source/sink 24 mA

n'ACT574 has TTL-compatible inputs

nStandard Microcircuit Drawing (SMD) Ð 'ACT574: 5962-89601

Logic Symbols

IEEE/IEC

DS100256-1

DS100256-4

|

Pin Names |

Description |

|

|

|

|

|

|

D0±D7 |

Data Inputs |

|

|

CP |

Clock Pulse Input |

|

|

|

TRI-STATE Output Enable Input |

|

|

OE |

|

|

|

O0±O7 |

TRI-STATE Outputs |

|

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

FACT™ is a trademark of Fairchild Semiconductor Corporation.

Outputs STATE-TRI with Flop-Flip Type-D Octal 54ACT574 · 54AC574

© 1998 National Semiconductor Corporation |

DS100256 |

www.national.com |

Connection Diagrams

Pin Assignment for DIP, |

Pin Assignment |

and Flatpak |

for LCC |

DS100256-2 |

DS100256-3 |

Functional Description

The 'AC/'ACT574 consists of eight edge-triggered flip-flops with individual D-type inputs and TRI-STATE true outputs. The buffered clock and buffered Output Enable are common to all flip-flops. The eight flip-flops will store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH Clock (CP) transition. With the Output Enable (OE) LOW, the contents of the eight flip-flops are available at the outputs. When OE is HIGH, the outputs go to the high impedance state. Operation of the OE input does not affect the state of the flip-flops.

Function Table

|

Inputs |

|

Internal |

Outputs |

Function |

|

|

|

|

|

|

|

|

|

|

CP |

D |

Q |

ON |

|

OE |

|

|||||

|

H |

H |

L |

NC |

Z |

Hold |

|

H |

H |

H |

NC |

Z |

Hold |

|

H |

N |

L |

L |

Z |

Load |

|

H |

N |

H |

H |

Z |

Load |

|

L |

N |

L |

L |

L |

Data Available |

|

L |

N |

H |

H |

H |

Data Available |

|

L |

H |

L |

NC |

NC |

No Change in Data |

|

L |

H |

H |

NC |

NC |

No Change in Data |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

N = LOW-to-HIGH Transition

NC = No Change

www.national.com |

2 |

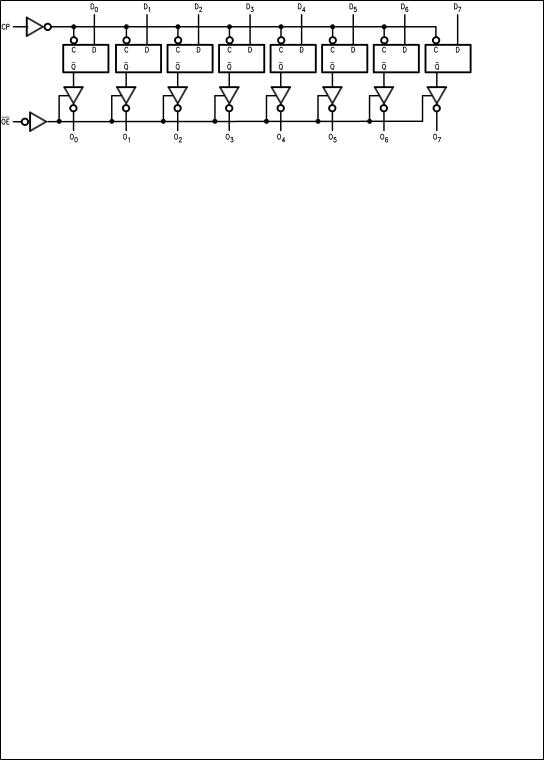

Logic Diagram

DS100256-5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

3 |

www.national.com |

Loading...

Loading...