Motorola MC10H186P, MC10H186FNR2, MC10H186FN, MC10H186L Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Hex D Master-Slave Flip-Flop with Reset

The MC10H186 is a hex D type flip±flop with common reset and clock lines. This MECL 10H part is a functional/pinout duplication of the standard MECL 10K family part, with 100% improvement in clock toggle frequency and propagation delay and no increase in power±supply current.

•Propagation Delay, 1.7 ns Typical

•Power Dissipation, 460 mW Typical

•Improved Noise Margin 150 mV (Over Operating Voltage and Temperature Range)

•Voltage Compensated

•MECL 10K±Compatible

MAXIMUM RATINGS

Characteristic |

Symbol |

Rating |

Unit |

|

|

|

|

Power Supply (VCC = 0) |

VEE |

±8.0 to 0 |

Vdc |

Input Voltage (VCC = 0) |

VI |

0 to VEE |

Vdc |

Output Current Ð Continuous |

Iout |

50 |

mA |

Ð Surge |

|

100 |

|

|

|

|

|

Operating Temperature Range |

TA |

0 to +75 |

°C |

Storage Temperature Range Ð Plastic |

Tstg |

±55 to +150 |

°C |

Ð Ceramic |

|

±55 to +165 |

°C |

|

|

|

|

ELECTRICAL CHARACTERISTICS (VEE = ±5.2 V ±5%) (See Note)

|

|

|

0° |

25° |

|

75° |

|

|||

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Min |

|

Max |

Min |

Max |

Min |

|

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

Power Supply Current |

IE |

Ð |

|

121 |

Ð |

110 |

Ð |

|

121 |

mA |

Input Current High |

IinH |

|

|

|

|

|

|

|

|

μA |

Pins 5,6,7,10,11,12 |

|

Ð |

|

430 |

Ð |

265 |

Ð |

|

265 |

|

Pin 9 |

|

Ð |

|

670 |

Ð |

420 |

Ð |

|

420 |

|

Pin 1 |

|

Ð |

|

1250 |

Ð |

765 |

Ð |

|

765 |

|

|

|

|

|

|

|

|

|

|

|

|

Input Current Low |

IinL |

0.5 |

|

Ð |

0.5 |

Ð |

0.3 |

|

Ð |

μA |

High Output Voltage |

VOH |

±1.02 |

|

±0.84 |

±0.98 |

±0.81 |

±0.92 |

|

±0.735 |

Vdc |

Low Output Voltage |

VOL |

±1.95 |

|

±1.63 |

±1.95 |

±1.63 |

±1.95 |

|

±1.60 |

Vdc |

High Input Voltage |

VIH |

±1.17 |

|

±0.84 |

±1.13 |

±0.81 |

±1.07 |

|

±0.735 |

Vdc |

Low Input Voltage |

VIL |

±1.95 |

|

±1.48 |

±1.95 |

±1.48 |

±1.95 |

|

±1.45 |

Vdc |

AC PARAMETERS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Propagation Delay |

tpd |

0.7 |

|

3.0 |

0.7 |

3.0 |

0.7 |

|

3.0 |

ns |

Set±up Time |

tset |

1.5 |

|

Ð |

1.5 |

Ð |

1.5 |

|

Ð |

ns |

Hold Time |

thold |

1.0 |

|

Ð |

1.0 |

Ð |

1.0 |

|

Ð |

ns |

Rise Time |

tr |

0.7 |

|

2.6 |

0.7 |

2.6 |

0.7 |

|

2.6 |

ns |

Fall Time |

tf |

0.7 |

|

2.6 |

0.7 |

2.6 |

0.7 |

|

2.6 |

ns |

Toggle Frequency |

ftog |

250 |

|

Ð |

250 |

Ð |

250 |

|

Ð |

MHz |

Reset Recovery Time |

trr |

3.0 |

|

Ð |

3.0 |

Ð |

3.0 |

|

Ð |

ns |

(t1±9+) |

|

|

|

|

|

|

|

|

|

|

NOTE:

Each MECL 10H series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50±ohm resistor to ±2.0 volts.

MC10H186

L SUFFIX

CERAMIC PACKAGE

CASE 620±10

P SUFFIX

PLASTIC PACKAGE

CASE 648±08

FN SUFFIX

PLCC

CASE 775±02

CLOCKED TRUTH TABLE

R |

C |

D |

Qn+1 |

|

|

|

|

L |

L |

X |

Qn |

|

|

|

|

L |

H * |

L |

L |

L |

H * |

H |

H |

H |

L |

X |

L |

*A clock H is a clock transition from a low to a high state.

DIP

PIN ASSIGNMENT

RESET |

|

1 |

|

16 |

|

VCC |

|

|

|

||||

Q0 |

|

2 |

|

15 |

|

Q5 |

|

|

|

||||

Q1 |

|

3 |

|

14 |

|

Q4 |

|

|

|

||||

Q2 |

|

4 |

|

13 |

|

Q3 |

|

|

|

||||

D0 |

|

5 |

|

12 |

|

D5 |

|

|

|

||||

D1 |

|

6 |

|

11 |

|

D4 |

|

|

|

||||

D2 |

|

7 |

|

10 |

|

D3 |

|

|

|

||||

VEE |

|

8 |

|

9 |

|

CLOCK |

|

|

|

||||

|

|

|

|

|

|

|

Pin assignment is for Dual±in±Line Package. For PLCC pin assignment, see the Pin Conversion Tables on page 6±11 of the Motorola MECL Data Book (DL122/D).

3/93

Motorola, Inc. 1996 |

2±280 |

REV 5 |

MC10H186

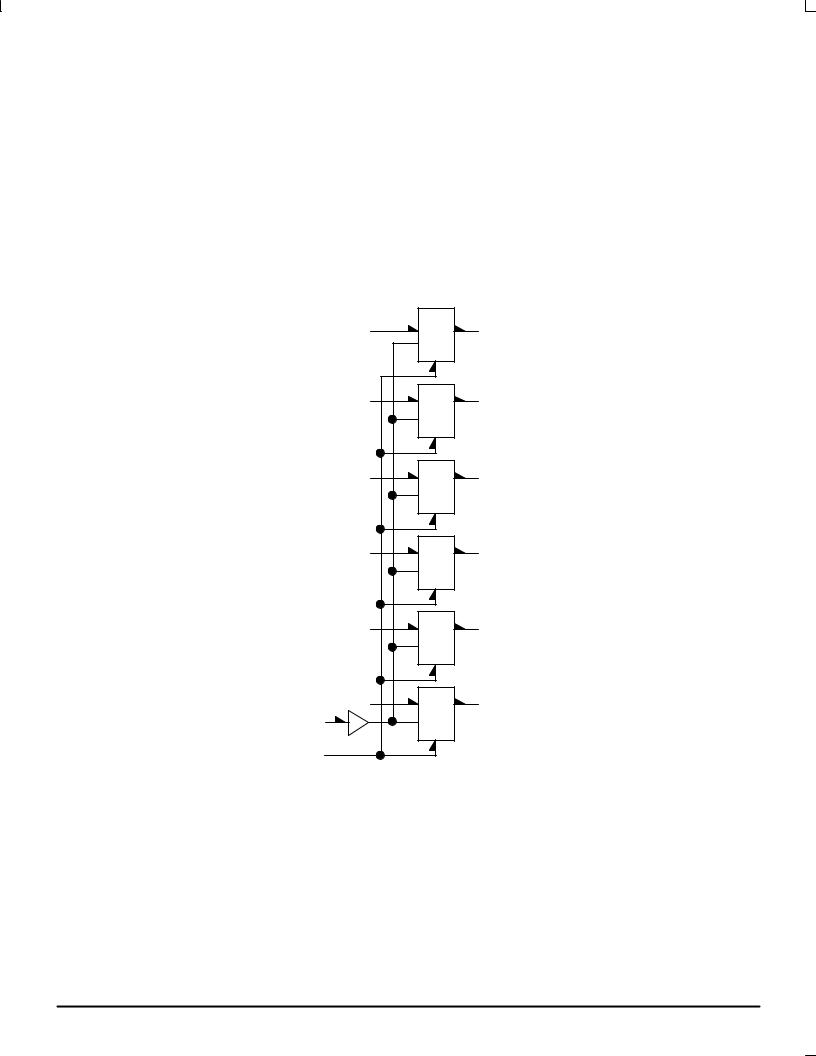

APPLICATION INFORMATION

The MC10H186 contains six high±speed, master slave type ªDº flip±flops. Data is entered into the master when the clock is low. Master±to±slave data transfer takes place on the positive±going Clock transition. Thus outputs may change only on a positive±going Clock

transition. A change in the information present at the data

(D) input will not affect the output information any other time due to the master±slave construction of this device. A common Reset is included in this circuit. THE RESET

ONLY FUNCTIONS WHEN THE CLOCK IS LOW.

LOGIC DIAGRAM

|

D0 |

5 |

|

2 |

Q0 |

|

D1 |

6 |

|

3 |

Q1 |

|

D2 |

7 |

|

4 |

Q2 |

|

D3 |

10 |

|

13 |

Q3 |

|

D4 |

11 |

|

14 |

Q4 |

|

D5 |

12 |

|

15 |

Q5 |

CLOCK |

9 |

|

|

|

|

RESET |

1 |

|

|

|

|

|

|

VCC = |

PIN 16 |

|

|

|

|

VEE |

= |

PIN 8 |

|

MECL Data |

2±281 |

MOTOROLA |

DL122 Ð Rev 6

Loading...

Loading...