IDT IDT54FCT16652T, IDT54FCT16652AT, IDT54FCT16652CT, IDT54FCT16652ET, IDT54FCT162652T User Manual

...

IDT54FCT162652ATEB

FAST CMOS 16-BIT BUS IDT54/74FCT16652T/AT/CT/ET |

|

TRANSCEIVER/ |

IDT54/74FCT162652T/AT/CT/ET |

|

|

REGISTERS |

|

Integrated Device Technology, Inc.

FEATURES:

•Common features:

–0.5 MICRON CMOS Technology

–High-speed, low-power CMOS replacement for ABT functions

–Typical tSK(o) (Output Skew) < 250ps

–Low input and output leakage ≤1μA (max.)

–ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R = 0)

–Packages include 25 mil pitch SSOP, 19.6 mil pitch TSSOP,15.7 mil pitch TVSOP and 25 mil pitch Cerpack

–Extended commercial range of -40°C to +85°C

–VCC = 5V ±10%

•Features for FCT16652T/AT/CT/ET:

–High drive outputs (-32mA IOH, 64mA IOL)

–Power off disable outputs permit “live insertion”

–Typical VOLP (Output Ground Bounce) < 1.0V at VCC = 5V, TA = 25°C

•Features for FCT162652T/AT/CT/ET:

–Balanced Output Drivers: ±24mA (commercial),

±16mA (military)

–Reduced system switching noise

–Typical VOLP (Output Ground Bounce) < 0.6V at VCC = 5V,TA = 25°C

DESCRIPTION:

The FCT16652T/AT/CT/ET and FCT162652T/AT/CT/ET 16-bit registered transceivers are built using advanced dual metal CMOS technology. These high-speed, low-power de-

vices are organized as two independent 8-bit bus transceivers with 3-state D-type registers. For example, the xOEAB and xOEBA signals control the transceiver functions.

The xSAB and xSBA control pins are provided to select either real time or stored data transfer. The circuitry used for select control will eliminate the typical decoding glitch that occurs in a multiplexer during the transition between stored and real time data. A LOW input level selects real-time data and a HIGH level selects stored data.

Data on the A or B data bus, or both, can be stored in the internal D-flip-flops by LOW-to-HIGH transitions at the appropriate clock pins (xCLKAB or xCLKBA), regardless of the select or enable control pins. Flow-through organization of signal pins simplifies layout. All inputs are designed with hysteresis for improved noise margin.

The FCT16652T/AT/CT/ET are ideally suited for driving high capacitance loads and low-impedance backplanes. The output buffers are designed with power off disable capability to allow "live insertion" of boards when used as backplane drivers.

The FCT162652T/AT/CT/ET have balanced output drive with current limiting resistors. This offers low ground bounce, minimal undershoot, and controlled output fall times–reducing the need for external series terminating resistors. The FCT162652T/AT/CT/ET are plug-in replacements for the FCT16652T/AT/CT/ET and ABT16652 for on-board bus interface applications.

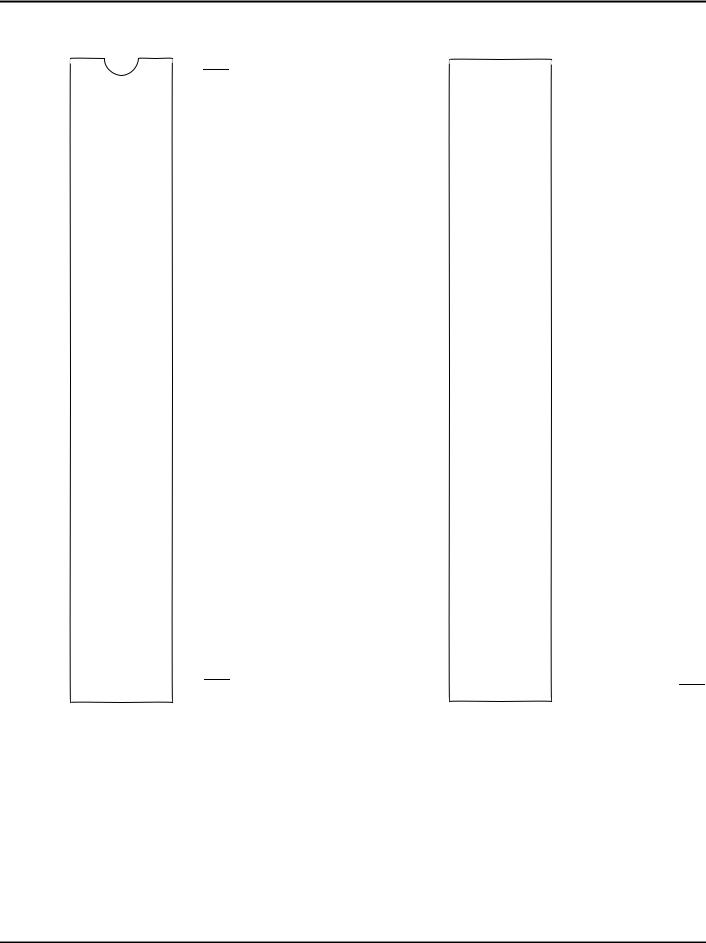

FUNCTIONAL BLOCK DIAGRAM

1OEAB |

|

|

2OEAB |

|

|

|

1OEBA |

|

|

2OEBA |

|

|

|

1CLKBA |

|

|

2CLKBA |

|

|

|

1SBA |

|

|

2SBA |

|

|

|

1CLKAB |

|

|

2CLKAB |

|

|

|

1SAB |

|

|

2SAB |

|

|

|

|

B REG |

|

|

|

|

B REG |

|

D |

|

|

|

|

D |

|

C |

|

|

|

|

C |

1A1 |

A REG |

1B1 |

2A1 |

A REG |

|

2B1 |

|

|

|||||

|

D |

|

|

D |

|

|

|

C |

|

|

C |

|

|

|

TO 7 OTHER CHANNELS |

2549 drw 01 |

|

|

TO 7 OTHER CHANNELS |

2549 drw 02 |

|

|

|

|

|

||

The IDT logo is a registered trademark of Integrated Device Technology, Inc. |

|

|

|

|

|

|

MILITARY AND COMMERCIAL TEMPERATURE RANGE |

|

|

|

AUGUST 1996 |

||

©1996 Integrated Device Technology, Inc. |

|

|

|

|

DSC-2549/8 |

|

1

IDT54/74FCT16652T/AT/CT/ET, FCT162652T/AT/CT/ET |

|

FAST CMOS 16-BIT BUS TRANSCEIVER/REGISTER |

MILITARY AND COMMERCIAL TEMPERATURE RANGES |

PIN CONFIGURATIONS

1OEAB |

|

1 |

|

56 |

|

1OEBA |

1CLKAB |

|

2 |

|

55 |

|

1CLKBA |

|

|

|

||||

1SAB |

|

3 |

|

54 |

|

1SBA |

|

|

|

||||

GND |

|

4 |

|

53 |

|

GND |

|

|

|

||||

1A1 |

|

5 |

|

52 |

|

1B1 |

|

|

|

||||

1A2 |

|

6 |

|

51 |

|

1B2 |

|

|

|

||||

VCC |

|

7 |

|

50 |

|

VCC |

|

|

|

||||

1A3 |

|

8 |

|

49 |

|

1B3 |

|

|

|

||||

1A4 |

|

9 |

|

48 |

|

1B4 |

|

|

|

||||

1A5 |

|

10 |

|

47 |

|

1B5 |

|

|

|

||||

GND |

|

11 |

|

46 |

|

GND |

|

|

|

||||

1A6 |

|

12 |

|

45 |

|

1B6 |

|

|

|

||||

1A7 |

|

13 |

|

44 |

|

1B7 |

|

|

|

||||

1A8 |

|

14 |

SO56-1 |

43 |

|

1B8 |

|

|

|||||

2A1 |

|

15 |

SO56-2 |

42 |

|

2B1 |

|

SO56-3 |

|

||||

2A2 |

|

16 |

|

41 |

|

2B2 |

|

|

|

||||

2A3 |

|

17 |

|

40 |

|

2B3 |

|

|

|

||||

GND |

|

18 |

|

39 |

|

GND |

|

|

|

||||

2A4 |

|

19 |

|

38 |

|

2B4 |

|

|

|

||||

2A5 |

|

20 |

|

37 |

|

2B5 |

|

|

|

||||

2A6 |

|

21 |

|

36 |

|

2B6 |

|

|

|

||||

VCC |

|

22 |

|

35 |

|

VCC |

|

|

|

||||

2A7 |

|

23 |

|

34 |

|

2B7 |

|

|

|

||||

2A8 |

|

24 |

|

33 |

|

2B8 |

|

|

|

||||

GND |

|

25 |

|

32 |

|

GND |

|

|

|

||||

2SAB |

|

26 |

|

31 |

|

2SBA |

|

|

|

||||

2CLKAB |

|

27 |

|

30 |

|

2CLKBA |

|

|

|

||||

2OEAB |

|

28 |

|

29 |

|

2OEBA |

|

|

|

SSOP/ |

2549 drw 03 |

TSSOP/TVSOP

TOP VIEW

1OEAB |

|

1 |

56 |

|

1OEBA |

|

|

||||

1CLKAB |

|

2 |

55 |

|

1CLKBA |

|

|

||||

|

|

||||

1SAB |

|

3 |

54 |

|

1SBA |

|

|

||||

|

|

||||

GND |

|

4 |

53 |

|

GND |

|

|

||||

|

|

||||

1A1 |

|

5 |

52 |

|

1B1 |

|

|

||||

1A2 |

|

6 |

51 |

|

1B2 |

|

|

||||

|

|

||||

VCC |

|

7 |

50 |

|

VCC |

|

|

||||

|

|

||||

1A3 |

|

8 |

49 |

|

1B3 |

|

|

||||

|

|

||||

1A4 |

|

9 |

48 |

|

1B4 |

|

|

||||

|

|

||||

1A5 |

|

10 |

47 |

|

1B5 |

|

|

||||

|

|

||||

GND |

|

11 |

46 |

|

GND |

|

|

||||

|

|

||||

1A6 |

|

12 |

45 |

|

1B6 |

|

|

||||

|

|

||||

1A7 |

|

13 |

44 |

|

1B7 |

|

|

||||

|

|

||||

1A8 |

|

14 |

E56-1 43 |

|

1B8 |

|

|

||||

|

|

||||

2A1 |

|

15 |

42 |

|

2B1 |

|

|

||||

|

|

||||

2A2 |

|

16 |

41 |

|

2B2 |

|

|

||||

|

|

||||

2A3 |

|

17 |

40 |

|

2B3 |

|

|

||||

|

|

||||

GND |

|

18 |

39 |

|

GND |

|

|

||||

|

|

||||

2A4 |

|

19 |

38 |

|

2B4 |

|

|

||||

|

|

||||

2A5 |

|

20 |

37 |

|

2B5 |

|

|

||||

|

|

||||

2A6 |

|

21 |

36 |

|

2B6 |

|

|

||||

|

|

||||

VCC |

|

22 |

35 |

|

VCC |

|

|

||||

|

|

||||

2A7 |

|

23 |

34 |

|

2B7 |

|

|

||||

|

|

||||

2A8 |

|

24 |

33 |

|

2B8 |

|

|

||||

|

|

||||

GND |

|

25 |

32 |

|

GND |

|

|

||||

|

|

||||

2SAB |

|

26 |

31 |

|

2SBA |

|

|

||||

|

|

||||

2CLKAB |

|

27 |

30 |

|

2CLKBA |

|

|

||||

|

|

||||

2OEAB |

|

28 |

29 |

|

2OEBA |

|

|

||||

|

|

||||

|

|

|

|

2549 drw 04 |

|

CERPACK

TOP VIEW

2

IDT54/74FCT16652T/AT/CT/ET, FCT162652T/AT/CT/ET |

|

FAST CMOS 16-BIT BUS TRANSCEIVER/REGISTER |

MILITARY AND COMMERCIAL TEMPERATURE RANGES |

PIN DESCRIPTION

Pin Names |

Description |

xAx |

Data Register A Inputs |

|

Data Register B Outputs |

xBx |

Data Register B Inputs |

|

Data Register A Outputs |

xCLKAB, xCLKBA |

Clock Pulse Inputs |

xSAB, xSBA |

Output Data Source Select Inputs |

xOEAB, xOEBA |

Output Enable Inputs |

2549 tbl 01

FUNCTION TABLE(2)

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol |

Parameter(1) |

Conditions |

Typ. |

Max. |

Unit |

CIN |

Input |

VIN = 0V |

4.5 |

6.0 |

pF |

|

Capacitance |

|

|

|

|

CI/O |

I/O |

VOUT = 0V |

5.5 |

8.0 |

pF |

|

Capacitance |

|

|

|

|

NOTE: |

|

|

|

2549 lnk 02 |

|

1. This parameter is measured at characterization but not tested.

|

|

Inputs |

|

|

Data I/O(1) |

Operation or Function |

||

xOEAB |

xOEBA |

xCLKAB |

xCLKBA |

xSAB |

xSBA |

xAx |

xBx |

|

L |

H |

H or L |

H or L |

X |

X |

Input |

Input |

Isolation |

L |

H |

− |

− |

X |

X |

|

|

Store A and B Data |

X |

H |

− |

H or L |

X |

X |

Input |

Unspecified(1) |

Store A, Hold B |

H |

H |

− |

− |

X(2) |

X |

Input |

Output |

Store A in Both Registers |

L |

X |

H or L |

− |

X |

X |

Unspecified(1) |

Input |

Hold A, Store B |

L |

L |

− |

− |

X |

X(2) |

Output |

Input |

Store B in both Registers |

L |

L |

X |

X |

X |

L |

Output |

Input |

Real Time B Data to A Bus |

L |

L |

X |

H or L |

X |

H |

|

|

Stored B Data to A Bus |

H |

H |

X |

X |

L |

X |

Input |

Output |

Real Time A Data to B Bus |

H |

H |

H or L |

X |

H |

X |

|

|

Stored A Data to B Bus |

H |

L |

H or L |

H or L |

H |

H |

Output |

Output |

Stored A Data to B Bus and |

|

|

|

|

|

|

|

|

Stored B Data to A Bus |

NOTES:

1. |

The data output functions may be enabled or disabled by various signals at the xOEAB or xOEBA inputs. |

|

||

|

Data input functions are always enabled, i.e. data at the bus pins will be stored on every LOW-to-HIGH |

|

||

|

transition on the clocks inputs. |

|

|

|

2. |

Select control = L: clocks can occur simultaneously. |

|

|

|

|

Select control = H: clocks must be staggered to load both registers. |

|

|

|

3. |

H = HIGH Voltage Level |

ABSOLUTE MAXIMUM RATINGS(1) |

|

|

|

L = LOW Voltage Level |

|

||

|

X = Don't care |

Symbol |

Description |

Max. |

|

− = LOW-to-HIGH Transition |

|||

VTERM(2)

VTERM(2) Terminal Voltage with Respect to

Terminal Voltage with Respect to  –0.5 to +7.0

–0.5 to +7.0

GND

VTERM(3) Terminal Voltage with Respect to

GND

2549 tbl 03

Unit

Unit

V

V

TSTG |

Storage Temperature |

–65 to +150 |

°C |

IOUT |

DC Output Current |

–60 to +120 |

mA |

NOTES: |

|

|

2549 lnk 04 |

1.Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2.All device terminals except FCT162XXXT Output and I/O terminals.

3.Output and I/O terminals for FCT162XXXT.

3

Loading...

Loading...