Integrated Device Technology Inc IDT74FCT646CTPY, IDT74FCT646CTPGB, IDT74FCT646CTPG, IDT74FCT646CTPB, IDT74FCT646CTP Datasheet

...

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FAST CMOS OCTAL |

IDT54/74FCT646T/AT/CT/DT - 2646T/AT/CT |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TRANSCEIVER/ |

|

|

IDT54/74FCT648T/AT/CT |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IDT54/74FCT652T/AT/CT/DT - 2652T/AT/CT |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REGISTERS (3-STATE) |

|

|||||||

Integrated Device Technology, Inc. |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

FEATURES: |

|

|

|

|

DESCRIPTION: |

|

||||||||||||||||

• Common features: |

|

|

|

|

The FCT646T/FCT2646T/FCT648T/FCT652T/2652T con- |

|||||||||||||||||

– Low input and output leakage ≤1μA (max.) |

|

sist of a bus transceiver with 3-state D-type flip-flops and |

||||||||||||||||||||

– Extended commercial range of –40°C to +85°C |

|

control circuitry arranged for multiplexed transmission of data |

||||||||||||||||||||

– |

CMOS power levels |

|

|

|

|

directly from the data bus or from the internal storage regis- |

||||||||||||||||

– True TTL input and output compatibility |

|

ters. |

|

|

|

|

||||||||||||||||

|

– VOH = 3.3V (typ.) |

|

|

|

|

The FCT652T/FCT2652T utilize GAB and GBA signals to |

||||||||||||||||

|

– VOL = 0.3V (typ.) |

|

|

|

|

control the transceiver functions. The FCT646T/FCT2646T/ |

||||||||||||||||

– Meets or exceeds JEDEC standard 18 specifications |

FCT648T utilize the enable control (G) and direction (DIR) |

|||||||||||||||||||||

– Product available in Radiation Tolerant and Radiation |

pins to control the transceiver functions. |

|

||||||||||||||||||||

|

Enhanced versions |

|

|

|

|

SAB and SBA control pins are provided to select either real- |

||||||||||||||||

– Military product compliant to MIL-STD-883, Class B |

time or stored data transfer. The circuitry used for select |

|||||||||||||||||||||

|

and DESC listed (dual marked) |

|

|

|

|

control will eliminate the typical decoding glitch that occurs in |

||||||||||||||||

– Available in DIP, SOIC, SSOP, QSOP, TSSOP, |

a multiplexer during the transition between stored and real- |

|||||||||||||||||||||

|

CERPACK and LCC packages |

|

|

|

|

time data. A LOW input level selects real-time data and a |

||||||||||||||||

• Features for FCT646T/648T/652T: |

|

|

|

|

HIGH selects stored data. |

|

||||||||||||||||

– Std., A, C and D speed grades |

|

|

|

|

Data on the A or B data bus, or both, can be stored in the |

|||||||||||||||||

– High drive outputs (-15mA IOH, 64mA IOL) |

|

internal D flip-flops by LOW-to-HIGH transitions at the appro- |

||||||||||||||||||||

– Power off disable outputs permit “live insertion” |

priate clock pins (CPAB or CPBA), regardless of the select or |

|||||||||||||||||||||

• Features for FCT2646T/2652T: |

|

|

|

|

enable control pins. |

|

||||||||||||||||

– Std., A, and C speed grades |

|

|

|

|

The FCT26xxT have balanced drive outputs with current |

|||||||||||||||||

– |

Resistor outputs (-15mA IOH, 12mA IOL Com.) |

limiting resistors. This offers low ground bounce, minimal |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

(-12mA IOH, 12mA IOL Mil.) |

|

undershoot and controlled output fall times-reducing the need |

|||||||||

– Reduced system switching noise |

|

|

|

|

for external series terminating resistors. FCT2xxxT parts are |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

plug-in replacements for FCTxxxT parts. |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

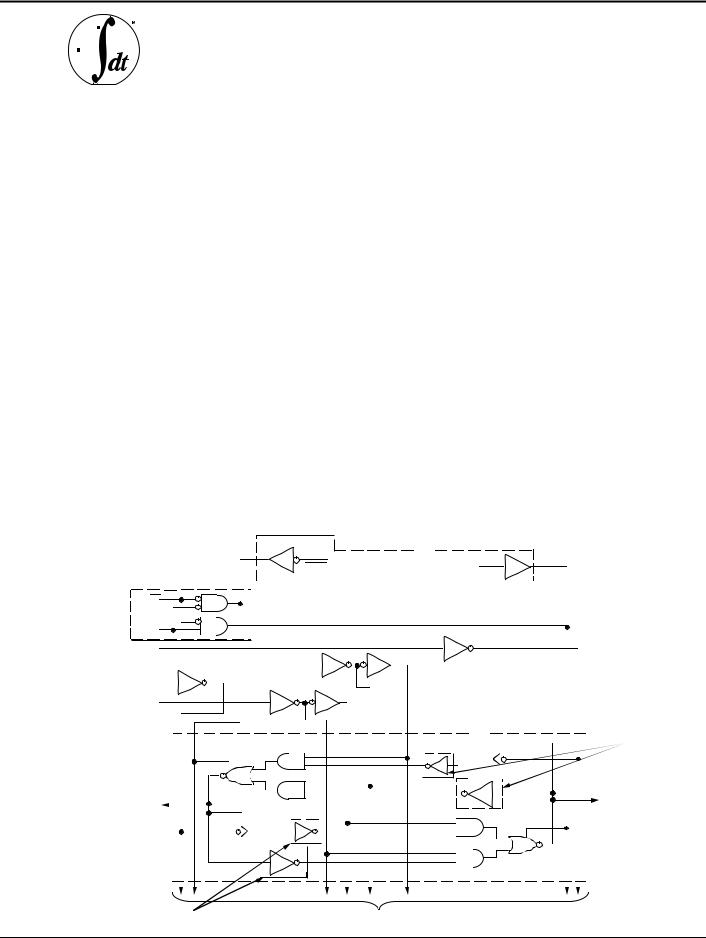

FUNCTIONAL BLOCK DIAGRAM |

|

IDT54/74FCT652/2652 |

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ONLY |

|

||

|

|

|

|

|

|

IDT54/74FCT646/2646/648 |

|

|

|

GBA |

|

GAB |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

ONLY |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

G |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

DIR |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

CPBA |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

SBA |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

CPAB |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

SAB |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B REG |

646/2646/652/2652 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 OF 8 CHANNELS |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1D |

|

ONLY |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

|

A REG |

|

|

|

|

|

B1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

1D |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

646/2646/652/2652 |

2634 drw 01 |

|

TO 7 OTHER CHANNELS |

||

ONLY |

||

|

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES |

SEPTEMBER 1996 |

|

©1996 Integrated Device Technology, Inc. |

6.20 |

DSC-2634/9 |

|

|

1 |

IDT54/74FCT646/2646/652/2652T/AT/CT/DT, 648T/AT/CT |

|

FAST CMOS OCTAL TRANSCEIVER/REGISTER |

MILITARY AND COMMERCIAL TEMPERATURE RANGES |

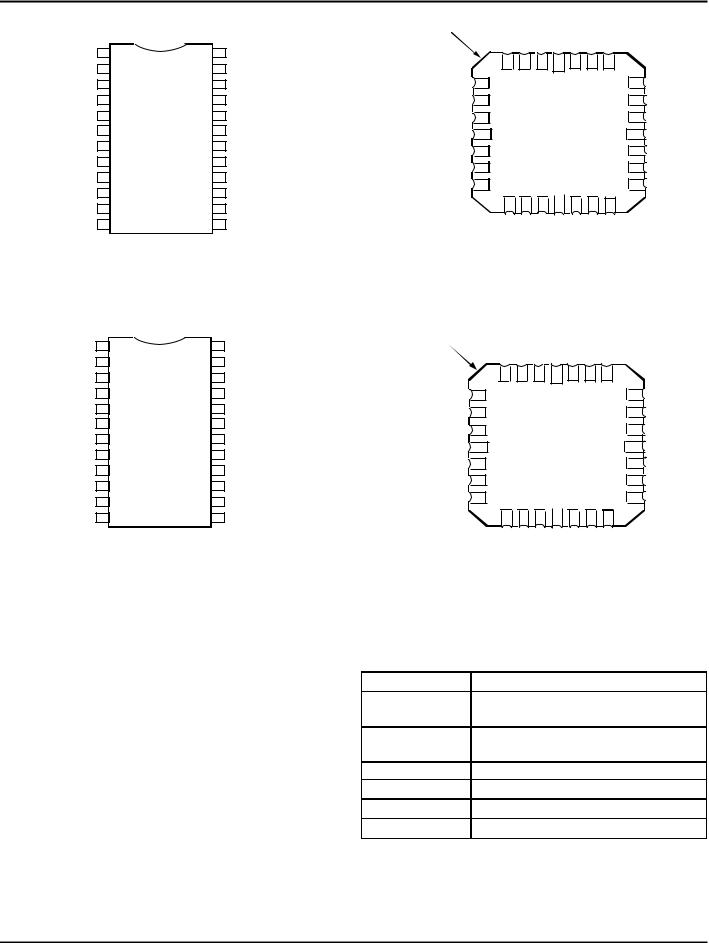

PIN CONFIGURATIONS |

|

|

|

INDEX |

|||

CPAB |

|

1 |

|

24 |

|

VCC |

|

|

|

|

|

||||

SAB |

|

2 |

|

23 |

|

CPBA |

FCT646/FCT2646T |

|

|

|

|||||

DIR |

|

3 |

P24-1 |

22 |

|

SBA |

|

|

|

||||||

|

|

FCT648 |

|||||

A1 |

|

4 |

21 |

|

G |

||

|

|

||||||

|

D24-1 |

|

|

||||

A2 |

|

5 |

20 |

|

B1 |

|

|

|

SO24-2 |

|

|

||||

A3 |

|

6 |

19 |

|

B2 |

|

|

|

SO24-7* |

|

|

||||

|

|

18 |

|

|

|||

A4 |

|

7 |

SO24-8 |

|

B3 |

|

|

|

|

|

|||||

A5 |

|

8 |

17 |

|

B4 |

|

|

|

SO24-9* |

|

|

||||

|

|

|

|||||

A6 |

|

9 |

& |

16 |

|

B5 |

|

|

|

|

|||||

A7 |

|

10 |

E24-1 |

15 |

|

B6 |

|

|

|

|

|||||

A8 |

|

11 |

|

14 |

|

B7 |

|

|

|

|

|

||||

GND |

|

12 |

|

13 |

|

B8 |

|

|

|

|

|

||||

2634 drw 02

DIP/SOIC/SSOP/

QSOP/TSSOP/CERPACK

TOP VIEW

|

|

DIR |

SAB |

CPAB |

NC |

VCC |

CPBA |

SBA |

|

A1 |

5 |

4 |

3 |

2 |

1 |

28 27 26 |

G |

||

|

|

|

|

|

|

25 |

|||

A2 |

6 |

|

|

|

|

|

|

24 |

B1 |

A3 |

7 |

|

|

|

|

|

|

23 |

B2 |

NC |

8 |

|

|

L28-1 |

|

22 |

NC |

||

A4 |

9 |

|

|

|

|

|

|

21 |

B3 |

A5 |

10 |

|

|

|

|

|

20 |

B4 |

|

A6 |

1112 13 14 15 16 17 1819 |

B5 |

|||||||

|

|

A7 |

A8 |

GND |

NC |

B8 |

B7 |

B6 |

2634 drw 03 |

|

|

|

|

LCC |

|

|

|

|

|

|

|

|

TOP VIEW |

|

|

|

|||

|

* FCT646/2646T/AT/CT/DT only |

|||||

CPAB |

|

1 |

|

24 |

|

VCC |

|

|

|

||||

SAB |

|

2 |

|

23 |

|

CPBA |

|

|

|

||||

GAB |

|

3 |

P24-1 |

22 |

|

SBA |

|

|

|||||

A1 |

|

4 |

21 |

|

GBA |

|

|

D24-1 |

|

||||

A2 |

|

5 |

20 |

|

B1 |

|

|

SO24-2 |

|

||||

|

|

|||||

A3 |

|

6 |

19 |

|

B2 |

|

|

SO24-7* |

|

||||

|

|

18 |

|

|||

A4 |

|

7 |

SO24-8 |

|

B3 |

|

|

|

|||||

A5 |

|

8 |

& |

17 |

|

B4 |

|

|

|||||

A6 |

|

9 |

E24-1 |

16 |

|

B5 |

|

|

|||||

A7 |

|

10 |

|

15 |

|

B6 |

|

|

|

||||

A8 |

|

11 |

|

14 |

|

B7 |

|

|

|

||||

GND |

|

12 |

|

13 |

|

B8 |

|

|

|

||||

2634 drw 04

DIP/SOIC/SSOP/

QSOP/CERPACK

TOP VIEW

* FCT652/2652T/AT/CT/DT only

INDEX |

GAB |

SAB |

CPAB |

NC VCC |

CPBA |

SBA |

|

|

|

|

|

|

FCT652/FCT2652T |

|

|

|

|

|

|

|

|

|

A1 |

5 |

4 |

3 |

2 |

1 |

28 27 26 |

GBA |

||

|

|

|

|

|

|

25 |

|||

A2 |

6 |

|

|

|

|

|

|

24 |

B1 |

A3 |

7 |

|

|

|

|

|

|

23 |

B2 |

NC |

8 |

|

|

L28-1 |

|

22 |

NC |

||

A4 |

9 |

|

|

|

|

|

|

21 |

B3 |

A5 |

10 |

|

|

|

|

|

20 |

B4 |

|

A6 |

1112 13 14 15 16 17 1819 |

B5 |

|||||||

|

|

A7 |

A8 |

GND |

NC |

B8 |

B7 |

B6 |

2634 drw 05 |

|

|

|

|||||||

LCC

TOP VIEW

PIN DESCRIPTION

Pin Names |

Description |

A1 - A8 |

Data Register A Inputs |

|

Data Register B Outputs |

B1 - B8 |

Data Register B Inputs |

|

Data Register A Outputs |

CPAB, CPBA |

Clock Pulse Inputs |

SAB, SBA |

Output Data Source Select Inputs |

DIR, G |

Output Enable Inputs (646/648) |

GAB, GBA |

Output Enable Inputs (652) |

2634 tbl 01

6.20 |

2 |

IDT54/74FCT646/2646/652/2652T/AT/CT/DT, 648T/AT/CT |

|

FAST CMOS OCTAL TRANSCEIVER/REGISTER |

MILITARY AND COMMERCIAL TEMPERATURE RANGES |

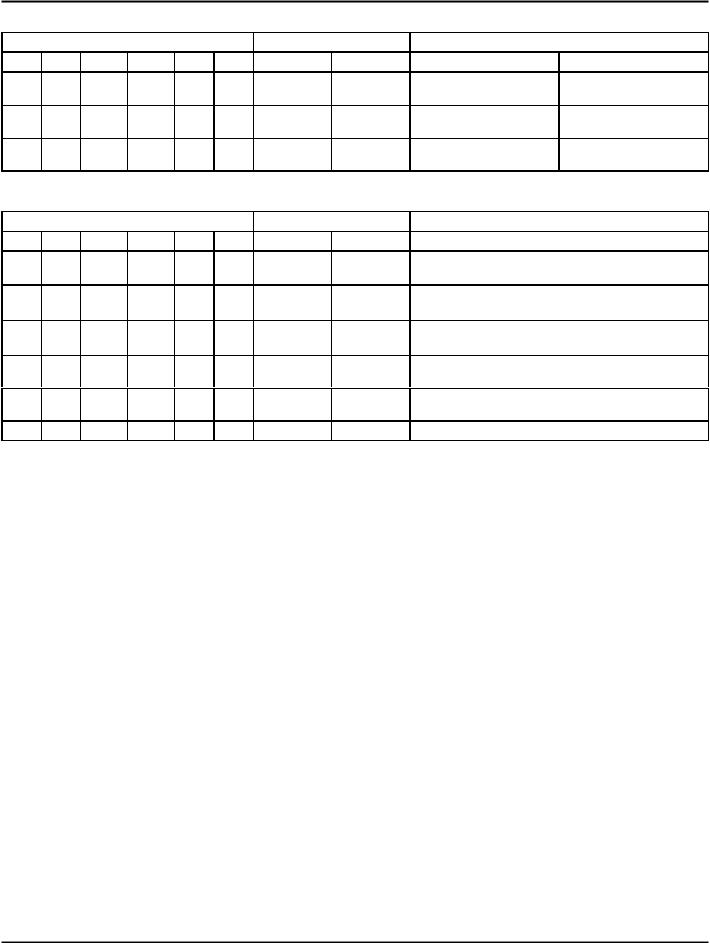

FUNCTION TABLE (646/648)

|

|

Inputs |

|

|

Data I/O(1) |

Operation or Function |

|||

G |

DIR |

CPAB |

CPBA |

SAB |

SBA |

A1 - A8 |

B1 - B8 |

FCT646T/FCT2646T |

FCT648T |

H |

X |

H or L |

H or L |

X |

X |

Input |

Input |

Isolation |

Isolation |

H |

X |

− |

− |

X |

X |

|

|

Store A and B Data |

Store A and B Data |

L |

L |

X |

X |

X |

L |

Output |

Input |

Real-Time B Data to A Bus |

Real-Time B Data to A Bus |

L |

L |

X |

H or L |

X |

H |

|

|

Stored B Data to A Bus |

Stored B Data to A Bus |

L |

H |

X |

X |

L |

X |

Input |

Output |

Real-Time A Data to B Bus |

Real-Time A Data to B Bus |

L |

H |

H or L |

X |

H |

X |

|

|

Stored A Data to B Bus |

Stored A Data to B Bus |

|

|

|

|

|

|

|

|

|

2634 tbl 02 |

FUNCTION TABLE (652)

|

|

Inputs |

|

|

Data I/O |

Operation or Function |

||

GAB |

GBA |

CPAB |

CPBA |

SAB |

SBA |

A1 - A8 |

B1 - B8 |

FCT652T/FCT2652T |

L |

H |

H or L |

H or L |

X |

X |

Input |

Input |

Isolation |

L |

H |

− |

− |

X |

X |

|

|

Store A and B Data |

X |

H |

− |

H or L |

X |

X |

Input |

Unspecified(1) |

Store A, Hold B |

H |

H |

− |

− |

X(2) |

X |

Input |

Output |

Store A in Both Registers |

L |

X |

H or L |

− |

X |

X |

Unspecified(1) |

Input |

Hold A, Store B |

L |

L |

− |

− |

X |

X(2) |

Output |

Input |

Store B in Both Registers |

L |

L |

X |

X |

X |

L |

Output |

Input |

Real-Time B Data to A Bus |

L |

L |

X |

H or L |

X |

H |

|

|

Stored B Data to A Bus |

H |

H |

X |

X |

L |

X |

Input |

Output |

Real-Time A Data to B Bus |

H |

H |

H or L |

X |

H |

X |

|

|

Stored A Data to B Bus |

H |

L |

H or L |

H or L |

H |

H |

Output |

Output |

Stored A Data to B Bus and Stored B Data to A Bus |

NOTES: |

|

|

|

|

|

|

|

2634 tbl 03 |

1.The data output functions may be enabled or disabled by various signals at the GAB or GBA inputs. Data input functions are always enabled, i.e. data at the bus pins will be stored on every LOW-to-HIGH transition on the clock inputs.

2.Select control = L: clocks can occur simultaneously.

Select control = H: clocks must be staggered in order to load both registers. H = HIGH, L = LOW, X = Don't Care, ¹ = LOW-to-HIGH transition.

3.A in B Register.

4.B in A Register.

6.20 |

3 |

Loading...

Loading...