Integrated Device Technology Inc IDT7210L55C, IDT7210L55CB, IDT7210L55F, IDT7210L55FB, IDT7210L55G Datasheet

...

16 x 16 PARALLEL CMOS |

IDT7210L |

MULTIPLIER-ACCUMULATOR |

|

Integrated Device Technology, Inc.

FEATURES:

•16 x 16 parallel multiplier-accumulator with selectable accumulation and subtraction

•High-speed: 20ns multiply-accumulate time

•IDT7210 features selectable accumulation, subtraction, rounding and preloading with 35-bit result

•IDT7210 is pin and function compatible with the TRW TDC1010J, TMC2210, Cypress CY7C510, and AMD AM29510

•Performs subtraction and double precision addition and multiplication

•Produced using advanced CMOS high-performance technology

•TTL-compatible

•Available in topbraze DIP, PLCC, Flatpack and Pin Grid Array

•Military product compliant to MIL-STD-883, Class B

•Standard Military Drawing #5962-88733 is listed on this function

•Speeds available:

Commercial: L20/25/35/45/55/65 Military: L25/30/40/55/65/75

DESCRIPTION:

The IDT7210 is a high-speed, low-power 16 x 16-bit parallel multiplier-accumulator that is ideally suited for real-time digital signal processing applications. Fabricated using CMOS silicon gate technology, this device offers a very low-power alternative to existing bipolar and NMOS counterparts, with only 1/7 to 1/10 the power dissipation and exceptional speed (25ns maximum) performance.

A pin and functional replacement for TRW’s TDC1010J the IDT7210 operates from a single 5 volt supply and is compatible with standard TTL logic levels. The architecture of the IDT7210 is fairly straightforward, featuring individual input and output registers with clocked D-type flip-flop, a preload capability which enables input data to be preloaded into the output registers, individual three-state output ports for the Extended Product (XTP) and Most Significant Product (MSP) and a Least Significant Product output (LSP) which is multiplexed with the Y input.

The XIN and YIN data input registers may be specified through the use of the Two’s Complement input (TC) as either a two’s complement or an unsigned magnitude, yielding a fullprecision 32-bit result that may be accumulated to a full 35-bit result. The three output registers – Extended Product (XTP), Most Most Significant Product (MSP) and Least Significant Product (LSP) – are controlled by the respective TSX, TSM and TSL input lines. The LSP output can be routed through YIN ports.

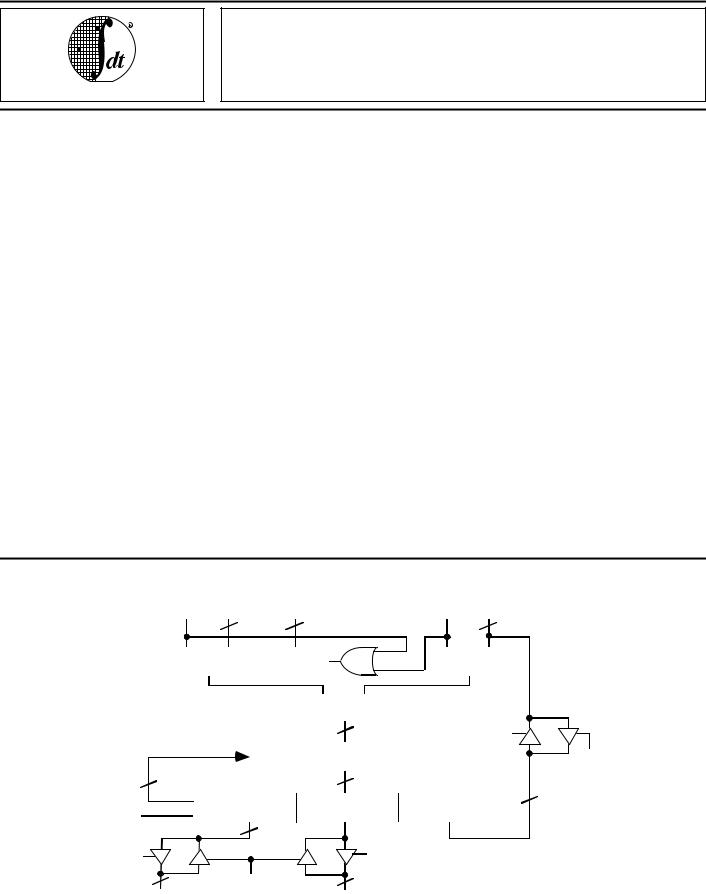

FUNCTIONAL BLOCK DIAGRAM

|

|

|

XIN |

|

|

ACC, SUB, |

|

|

YIN |

|

|||||

CLKX (X15-X0) |

|

|

RND, TC |

CLKY (Y15-Y0/P15-P0) |

|||||||||||

|

|

16 |

|

|

|

|

4 |

|

16 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XREGISTER |

|

|

|

CONTROL |

|

|

YREGISTER |

|

|

||||

|

|

|

|

REGISTER |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MULTIPLIER ARRAY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+/– |

|

|

|

32 + |

|

|

TSL |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

ACCUMULATOR |

|

|

|

|

|

PREL |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

|

|

|

|

|

|

35 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLKP |

|

XTP REGISTER MSP REGISTER |

LSP REGISTER |

|

|

16 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

TSX |

|

|

|

|

|

|

|

TSM |

|

|

|

|

|

|

|

3 |

|

PREL |

16 |

|

|

|

|

|

|

||||||

XTPOUT |

|

|

|

MSPOUT |

|

|

|

|

|

|

|||||

(P34-P32) |

|

|

(P31-P16) |

|

|

|

|

|

2577 drw 01 |

||||||

|

|

|

|

|

|

|

|

|

IDT7210 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

MILITARY AND COMMERCIAL TEMPERATURE RANGES |

|

|

|

|

|

AUGUST 1995 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

©1995 Integrated Device Technology, Inc. |

|

|

|

|

|

|

11.2 |

|

|

|

|

|

DSC-2018/7 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

IDT7210L |

|

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR |

MILITARY AND COMMERCIAL TEMPERATURE RANGES |

DESCRIPTION (Continued)

The Accumulate input (ACC) enables the device to perform either a multiply or a multiply-accumulate function. In the multiply-accumulate mode, output data can be added to or subtracted from previous results. When the Subtraction (SUB) input is active simultaneously with an active ACC, a subtraction can be performed. The double precision accumulated result is rounded down to either a single precision or single precision plus 3-bit extended result. In the multiply mode, the Extended

Product output (XTP) is sign extended in the two’s complement mode or set to zero in the unsigned mode. The Round (RND) control rounds up the Most Significant Product (MSP) and the 3-bit Extended Product (XTP) outputs. When Preload input (PREL) is active, all the output buffers are forced into a highimpedance state (see Preload truth table) and external data can be loaded into the output register by using the TSX, TSL and TSM signals as input controls.

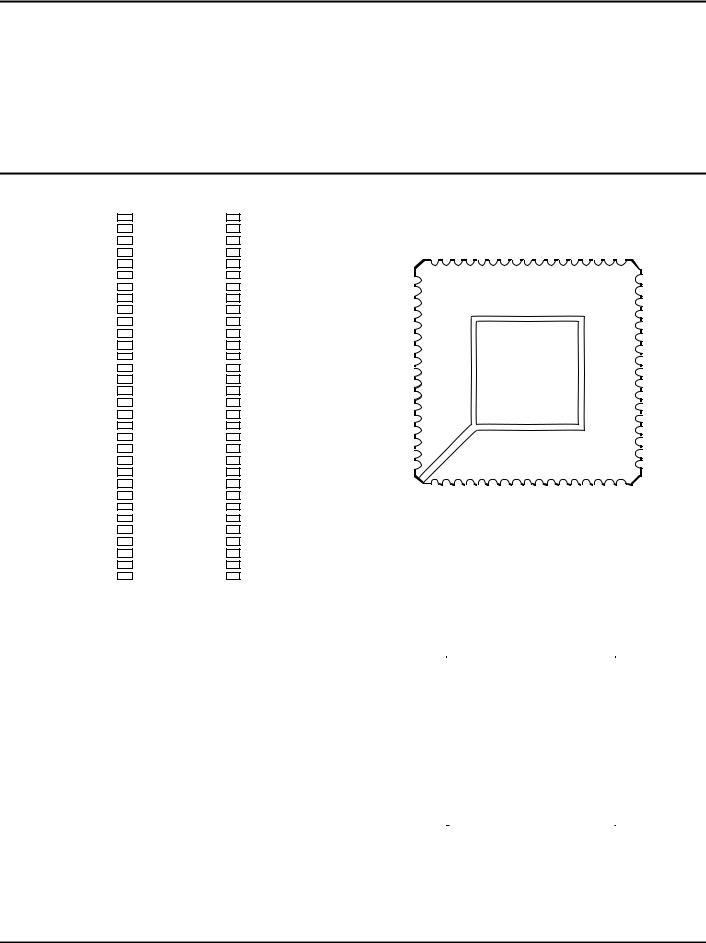

PIN CONFIGURATIONS

X6 |

|

1 |

|

64 |

|

X7 |

|

|

|

||||

X5 |

|

2 |

|

63 |

|

X8 |

X4 |

|

3 |

|

62 |

|

X9 |

X3 |

|

4 |

|

61 |

|

X10 |

X2 |

|

5 |

|

60 |

|

X11 |

X1 |

|

6 |

|

59 |

|

X12 |

X0 |

|

7 |

|

58 |

|

X13 |

P0, |

|

8 |

|

57 |

|

X14 |

P1, |

|

9 |

|

56 |

|

X15 |

P2, |

|

10 |

|

55 |

|

TSL |

P3, |

|

11 |

|

54 |

|

RND |

P4, |

|

12 |

|

53 |

|

SUB |

P5, |

|

13 |

|

52 |

|

ACC |

P6, |

|

14 |

|

51 |

|

CLKX |

|

|

|

||||

P7, |

|

15 |

|

50 |

|

CLKY |

GND |

|

16 |

C64-2 |

49 |

|

VCC |

P8, |

|

17 |

|

48 |

|

TC |

P9, |

|

18 |

|

47 |

|

TSX |

P10, |

|

19 |

|

46 |

|

PREL |

P11, |

|

20 |

|

45 |

|

TSM |

P12, |

|

21 |

|

44 |

|

CLKP |

P13, |

|

22 |

|

43 |

|

P34 |

P14, |

|

23 |

|

42 |

|

P33 |

P15, |

|

24 |

|

41 |

|

P32 |

P16 |

|

25 |

|

40 |

|

P31 |

P17 |

|

26 |

|

39 |

|

P30 |

P18 |

|

27 |

|

38 |

|

P29 |

|

|

|

||||

P19 |

|

28 |

|

37 |

|

P28 |

P20 |

|

29 |

|

36 |

|

P27 |

P21 |

|

30 |

|

35 |

|

P26 |

P22 |

|

31 |

|

34 |

|

P25 |

P23 |

|

32 |

|

33 |

|

P24 |

|

|

|

|

|

|

|

|

|

|

|

2577 drw 02 |

||

DIP

TOP VIEW

|

|

|

|

P2, Y2 |

P3, Y3 |

P4, Y4 P5, Y5 |

P6, Y6 |

P7, Y7 GND GND P8, Y8 P9, Y9 P10, Y10 P11, Y11 P12, Y12 |

P13, Y13 P14, Y14 |

P15, Y15 P16 |

|

|

|

|

||||||||||||||||||||||||||||||||

|

60 59 58 5756 55 54 53 5251 50 4948 47 46 45 44 |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

P1, Y1 61 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

P17 |

|||||||

P0, Y0 62 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

P18 |

|||||||

X0 63 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

P19 |

|||||||

X1 64 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

P20 |

|||||||

X2 65 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

P21 |

|||||||

X3 66 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

P22 |

|||||||

X4 67 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

P23 |

|||||||

X5 68 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

P24 |

|||||||

X6 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J68-1, L68-1 |

|

|

|

|

|

|

|

|

|

|

|

35 |

P25 |

|||||||||||||||

X7 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J68-1 |

|

|

|

|

|

|

|

|

|

|

|

34 |

P26 |

||||||||||||

X8 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

P27 |

||

X9 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

P28 |

||

X10 |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

P29 |

||

X11 |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

P30 |

||

X12 |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

P31 |

||

X13 |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

28 |

P32 |

||

X14 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

27 |

P33 |

||

|

10 11 1213 14 1516 17 18 19 20 2122 23 24 25 26 |

|

|

|

2577 drw 03 |

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

X15 |

TSL |

RND SUB ACC |

CLKX CLKY VCC VCC VCC VCC TC TSX |

PREL TSM CLKP P34 |

|

|

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PLCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TOP VIEW |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

P1, Y1 ,P2 Y2 3P, Y3 |

4P, Y4 |

P5, Y5 P6, Y6 P7, Y7 GND P8, Y8 P9, Y9 P10, Y10 P11, Y11 12P, Y12 |

|

Y13 Y14 |

P15, Y15 |

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

P P14 |

|

|

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

, |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13, |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64636261 605958575655 545352 515049 |

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

P0, Y0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P16 |

||

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

X0 |

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

|

P17 |

|

X1 |

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

|

P18 |

|

X2 |

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

|

P19 |

|

X3 |

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

|

P20 |

|

X4 |

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

|

P21 |

|

X5 |

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

|

|

P22 |

|

X6 |

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

|

|

P23 |

|

X7 |

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F64-1 |

|

|

|

|

|

|

|

|

|

40 |

|

|

P24 |

||||||||||||

X8 |

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

|

P25 |

|

X9 |

|

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

|

P26 |

|

X10 |

|

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

P27 |

|

X11 |

|

|

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

|

P28 |

|

X12 |

|

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

|

P29 |

|

X13 |

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

|

P30 |

|

X14 |

|

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

P31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17181920 212223242526 272829 303132 |

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2577 drw 04 |

||||

|

|

|

|

|

|

X15 |

TSL RND |

SUB |

ACC CLKX CLKY VCC TC TSX PREL TSM CLKP |

P34 P33 |

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

P32 |

|

|

|

|

||||||||||||||||||||||||||||||||||||

FLATPACK

TOP VIEW

11.2 |

2 |

IDT7210L |

|

16 x 16 PARALLEL CMOS MULTIPLIER-ACCUMULATOR |

MILITARY AND COMMERCIAL TEMPERATURE RANGES |

11 |

|

NC |

X15 |

RND |

ACC CLKY |

TC |

PREL CLKP |

P33 |

|

|||

10 |

X13 |

X14 |

TSL |

SUB CLKX |

VCC |

TSX |

TSM |

P34 |

P32 |

NC |

||

09 |

X11 |

X12 |

|

|

|

|

|

|

|

P30 |

P31 |

|

08 |

X9 |

X10 |

|

|

|

|

|

|

|

P28 |

P29 |

|

07 |

X7 |

X8 |

|

|

|

|

|

|

|

P26 |

P27 |

|

06 |

X5 |

X6 |

|

|

|

G68-2 |

|

|

|

P24 |

P25 |

|

05 |

X3 |

X4 |

|

|

|

|

|

|

|

P22 |

P23 |

|

04 |

X1 |

X2 |

|

|

|

|

|

|

|

P20 |

P21 |

|

03 |

Y0, |

X0 |

|

|

|

|

|

|

|

P18 |

P19 |

|

P0 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

02 |

NC |

Y1, |

Y3, |

Y5, |

Y7, |

Y8, |

Y10, |

Y12, |

Y14, |

P16 |

P17 |

|

P1 |

P3 |

P5 |

P7 |

P8 |

P10 |

P12 |

P14 |

|||||

|

|

|

|

|||||||||

01 |

|

Y2, |

Y4, |

Y6, |

GND |

Y9, |

Y11, |

Y13, |

Y15, |

NC |

|

|

|

P2 |

P4 |

P6 |

P9 |

P11 |

P13 |

P15 |

|

||||

|

|

|

|

|

||||||||

Pin 1 |

A |

B |

C |

D |

E |

F |

G |

H |

J |

K |

L |

|

Designator |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||

PGA

2577 drw 05

TOP VIEW

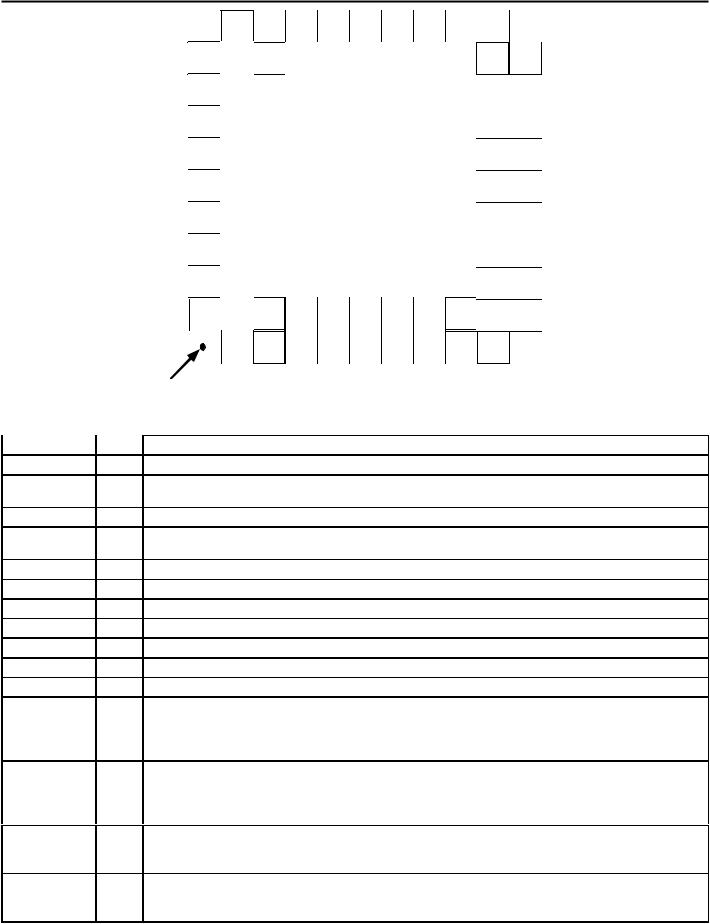

PIN DESCRIPTIONS

Pin Name |

I/O |

Description |

|

X0 - 15 |

I |

Data Inputs |

|

Y0 - 15/ P0 - 15 |

I/O |

Multiplexed I/O port. Y0 - 15 are data inputs and can be used to preload LSP register on PREL = 1. P0 - 15 |

|

|

|

are LSP register outputs - enabled by TSL. |

|

P16 - 31 |

I/O |

MSP register outputs - enabled by TSM. MSP register can be preloaded when PREL = 1. |

|

P32 - 34 |

I/O |

XTP register outputs - enabled by TSX. XTP register can be preloaded through these inputs when |

|

|

|

PREL = 1. |

|

CLKX |

I |

Input data X0 - 15 loaded in X input register on CLKX rising edge. |

|

CLKY |

I |

Input data Y0 - 15 loaded in Y input register on CLKY rising edge. |

|

CLKP |

I |

Output data loaded into output register on rising edge of CLKP. |

|

TSX |

I |

TSX = 0 enables XTP outputs, TSX = 1 tristates P32 - 34 lines. |

|

TSM |

I |

TSM = 0 enables MSP outputs, TSM = 1 tristates P16 - 31 lines. |

|

TSL |

I |

TSL = 0 enables LSP outputs, TSL = 1 tristates P0 - 15 lines. |

|

PREL |

I |

When PREL= 1 data is input on P0 - 15 lines. When PREL = 0, inputs on these lines are ignored. |

|

ACC |

I |

This input is loaded into the control register on the rising edge of (CLKX + CLKY). |

|

|

|

When ACC = 1 and SUB = 0 an accumulate operation is performed. When ACC = 1 and SUB = 1, a |

|

|

|

subtract operation is performed. When ACC = 0, the SUB input is a don't care and the device acts as a |

|

|

|

simple multipler with no accumulation |

|

SUB |

I |

This input is loaded into the control register on the rising edge of (CLKX + CLKY). |

|

|

|

This input is active only when ACC = 1. When SUB = 1 the contents of the output register are subtracted |

|

|

|

from the result and stored back in the output register. When SUB = 0 the contents of the output register |

|

|

|

are added to the result and stored back in the output register |

|

TC |

I |

This input is loaded into the control register on the rising edge of (CLKX + CLKY). |

|

|

|

When TC = 1, the X and Y input are assumed to be in two's complement form. When TC = 0, X and Y |

|

|

|

inputs are assumed to be in unsigned magnitude form |

|

RND |

I |

This input is loaded into the control register on the rising edge of (CLKX + CLKY). |

|

|

|

RND is inactive when low. RND = 1, adds a "1" to the most significant bit of the LSP, to round MSP and |

|

|

|

XTP data |

|

|

|

2577 tbl 01 |

|

|

|

|

|

11.2 |

3 |

Loading...

Loading...