Fairchild Semiconductor CD4024BCN, CD4024BCMX, CD4024BCM Datasheet

October 1987

Revised January 1999

CD4024BC

7-Stage Ripple Carry Binary Counter

General Description

The CD4024BC is a 7-stage ripple-carry binary counter. Buffered outputs are externally available from stages 1 through 7. The counter is reset to its logical “0” stage by a logical “1” on the reset input. The counter is advanced one count on the negative transition of each clock pulse.

Features

■Wide supply voltage range: 3.0V to 15V

■High noise immunity: 0.45 VDD (typ.)

■Low power TTL compatibility: Fan out of 2 driving 74L or 1 driving 74LS

■High speed: 12 MHz (typ.)

input pulse rate VDD − VSS = 10V

■ Fully static operation

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

CD4024BCM |

M14A |

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow Body |

|

|

|

CD4024BCN |

N14A |

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram

Pin Assignments for DIP and SOIC

Top View

Counter Binary Carry Ripple Stage-7 CD4024BC

© 1999 Fairchild Semiconductor Corporation |

DS005957.prf |

www.fairchildsemi.com |

CD4024BC

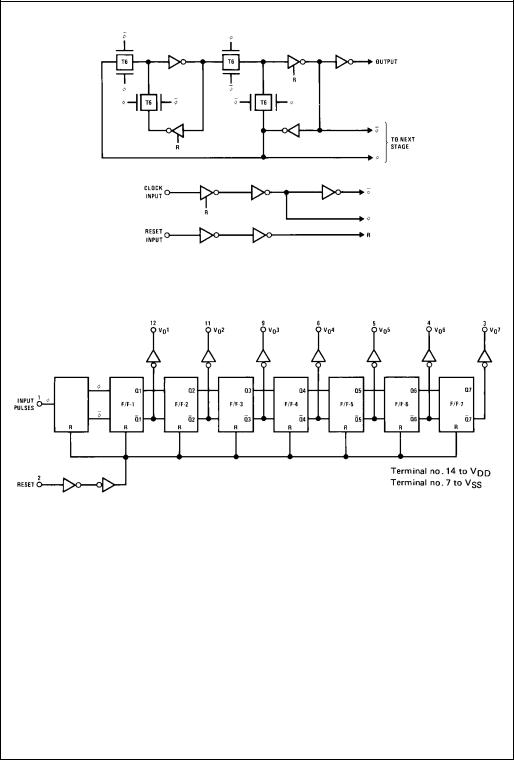

Logic Diagrams

Input Logic

Flip-flop logic (1 of 7 identical stages).

Block Diagram

www.fairchildsemi.com |

2 |

Loading...

Loading...