Fairchild Semiconductor CD4053BCSJX, CD4053BCSJ, CD4053BCN, CD4053BCMX, CD4053BCM Datasheet

...

November 1983

Revised August 2000

CD4051BC • CD4052BC • CD4053BC

Single 8-Channel Analog Multiplexer/Demultiplexer •

Dual 4-Channel Analog Multiplexer/Demultiplexer •

Triple 2-Channel Analog Multiplexer/Demultiplexer

General Description |

Features |

The CD4051BC, CD4052BC, and CD4053BC analog multiplexers/demultiplexers are digitally controlled analog switches having low “ON” impedance and very low “OFF” leakage currents. Control of analog signals up to 15Vp-p can be achieved by digital signal amplitudes of 3− 15V. For example, if VDD = 5V, VSS = 0V and VEE = − 5V, analog signals from − 5V to + 5V can be controlled by digital inputs of 0− 5V. The multiplexer circuits dissipate extremely low quiescent power over the full VDD− VSS and VDD− VEE supply voltage ranges, independent of the logic state of the control signals. When a logical “1” is present at the inhibit input terminal all channels are “OFF”.

CD4051BC is a single 8-channel multiplexer having three binary control inputs. A, B, and C, and an inhibit input. The three binary signals select 1 of 8 channels to be turned “ON” and connect the input to the output.

CD4052BC is a differential 4-channel multiplexer having two binary control inputs, A and B, and an inhibit input. The two binary input signals select 1 or 4 pairs of channels to be turned on and connect the differential analog inputs to the differential outputs.

CD4053BC is a triple 2-channel multiplexer having three separate digital control inputs, A, B, and C, and an inhibit input. Each control input selects one of a pair of channels which are connected in a single-pole double-throw configuration.

■Wide range of digital and analog signal levels: digital 3 – 15V, analog to 15Vp-p

■Low “ON” resistance: 80Ω (typ.) over entire 15Vp-p signal-input range for VDD − VEE = 15V

■High “OFF” resistance:

channel leakage of ± 10 pA (typ.) at VDD − VEE = 10V

■Logic level conversion for digital addressing signals of

3 – 15V (VDD − VSS = 3 – 15V) to switch analog signals to 15 Vp-p (VDD − VEE = 15V)

■Matched switch characteristics:

∆ RON = 5Ω (typ.) for VDD − VEE = 15V

■Very low quiescent power dissipation under all

digital-control input and supply conditions:

1 µ W (typ.) at VDD − VSS = VDD − VEE = 10V

■Binary address decoding on chip

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

CD4051BCM |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|

|

|

CD4051BCSJ |

M16D |

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

CD4051BCMTC |

MTC16 |

16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |

|

|

|

CD4051BCN |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

CD4052BCM |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|

|

|

CD4052BCSJ |

M16D |

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

CD4052BCN |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

CD4053BCM |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|

|

|

CD4053BCSJ |

M16D |

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

CD4053BCN |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Multiplexer/Demultiplexer Analog Channel-2 Triple • Multiplexer/Demultiplexer |

Multiplexer/Demultiplexer Analog Channel-8 Single CD4053BC • CD4052BC • CD4051BC |

|

Analog Channel-4 Dual • |

© 2000 Fairchild Semiconductor Corporation |

DS005662 |

www.fairchildsemi.com |

CD4051BC • CD4052BC • CD4053BC

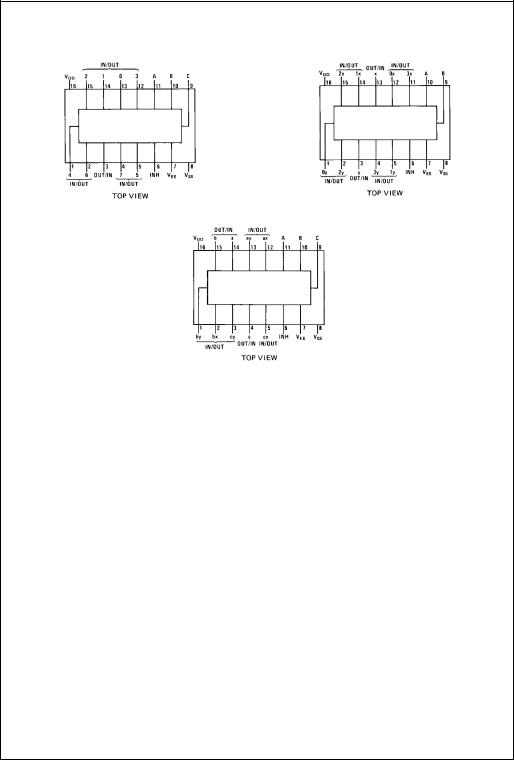

Connection Diagrams

Pin Assignments for DIP and SOIC

CD4051BC |

CD4052BC |

CD4053BC

Truth Table

|

INPUT STATES |

|

“ON” CHANNELS |

|||

|

|

|

|

|

|

|

INHIBIT |

C |

B |

A |

CD4051B |

CD4052B |

CD4053B |

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0X, 0Y |

cx, bx, ax |

0 |

0 |

0 |

1 |

1 |

1X, 1Y |

cx, bx, ay |

0 |

0 |

1 |

0 |

2 |

2X, 2Y |

cx, by, ax |

0 |

0 |

1 |

1 |

3 |

3X, 3Y |

cx, by, ay |

0 |

1 |

0 |

0 |

4 |

|

cy, bx, ax |

0 |

1 |

0 |

1 |

5 |

|

cy, bx, ay |

0 |

1 |

1 |

0 |

6 |

|

cy, by, ax |

0 |

1 |

1 |

1 |

7 |

|

cy, by, ay |

1 |

* |

* |

* |

NONE |

NONE |

NONE |

|

|

|

|

|

|

|

*Don’t Care condition.

www.fairchildsemi.com |

2 |

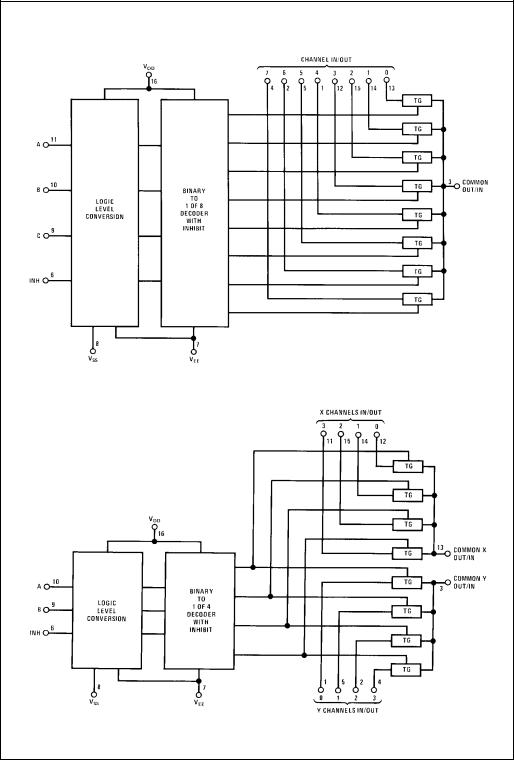

Logic Diagrams

CD4051BC

CD4052BC

CD4053BC • CD4052BC • CD4051BC

3 |

www.fairchildsemi.com |

CD4051BC • CD4052BC • CD4053BC

Logic Diagrams (Continued)

CD4053BC

www.fairchildsemi.com |

4 |

Loading...

Loading...