Fairchild Semiconductor CD4050BCSJ, CD4050BCN, CD4050BCMX, CD4050BCM, CD4050BCW Datasheet

...

October 1987

Revised January 1999

CD4049UBC • CD4050BC

Hex Inverting Buffer •

Hex Non-Inverting Buffer

General Description

The CD4049UBC and CD4050BC hex buffers are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. These devices feature logic level conversion using only one supply voltage (VDD). The input signal high level (VIH) can exceed the VDD supply voltage when these devices are used for logic level conversions. These devices are intended for use as hex buffers, CMOS to DTL/ TTL converters, or as CMOS current drivers, and at VDD = 5.0V, they can drive directly two DTL/TTL loads over the full operating temperature range.

Features

■Wide supply voltage range: 3.0V to 15V

■Direct drive to 2 TTL loads at 5.0V over full temperature range

■High source and sink current capability

■Special input protection permits input voltages greater than VDD

Applications

•CMOS hex inverter/buffer

•CMOS to DTL/TTL hex converter

•CMOS current “sink” or “source” driver

•CMOS HIGH-to-LOW logic level converter

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

CD4049UBCM |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow |

|

|

|

CD4049UBCN |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

CD4050BCM |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow |

|

|

|

CD4050BCN |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

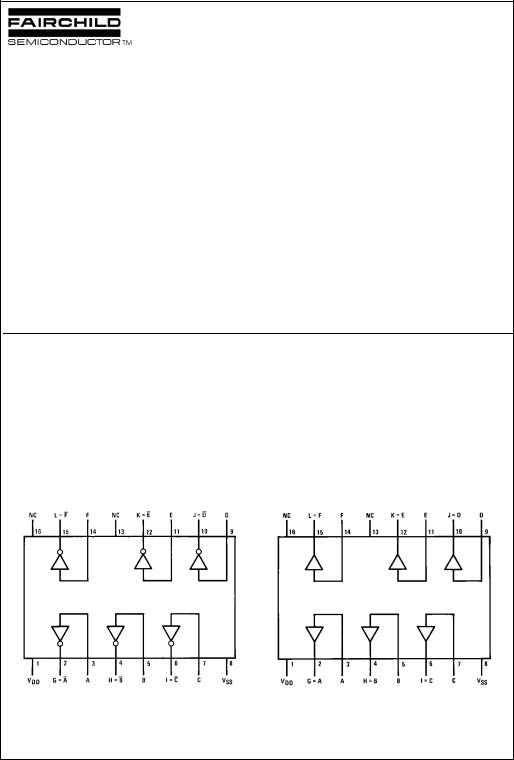

Connection Diagrams

Pin Assignments for DIP

CD4049UBC |

CD4050BC |

Top View |

Top View |

Buffer Inverting-Non Hex • Buffer Inverting Hex CD4050BC • CD4049UBC

© 1999 Fairchild Semiconductor Corporation |

DS005971.prf |

www.fairchildsemi.com |

CD4049UBC • CD4050BC

Schematic Diagrams

CD4049UBC

1 of 6 Identical Units

CD4050BC

1 of 6 Identical Units

www.fairchildsemi.com |

2 |

Absolute Maximum Ratings(Note 1)

(Note 2) |

|

Supply Voltage (VDD) |

−0.5V to +18V |

Input Voltage (VIN) |

−0.5V to +18V |

Voltage at Any Output Pin (VOUT) |

−0.5V to VDD + 0.5V |

Storage Temperature Range (TS) |

−65°C to +150°C |

Power Dissipation (PD) |

|

Dual-In-Line |

700 mW |

Small Outline |

500 mW |

Lead Temperature (TL) |

260°C |

(Soldering, 10 seconds) |

DC Electrical Characteristics (Note 3)

Recommended Operating

Conditions (Note 2)

Supply Voltage (VDD) |

3V to 15V |

Input Voltage (VIN) |

0V to 15V |

Voltage at Any Output Pin (VOUT) |

0 to VDD |

Operating Temperature Range (TA) |

−40°C to +85°C |

CD4049UBC, CD4050BC |

Note 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed; they are not meant to imply that the devices should be operated at these limits. The table of “Recommended Operating Conditions” and “Electrical Characteristics” provides conditions for actual device operation.

Note 2: VSS = 0V unless otherwise specified.

|

Symbol |

Parameter |

|

|

Conditions |

−40°C |

|

+25°C |

|

+85°C |

Units |

||||

|

|

|

|

|

|

|

|

Min |

Max |

Min |

Typ |

Max |

Min |

Max |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

IDD |

Quiescent Device Current |

VDD = 5V |

|

|

|

4 |

|

0.03 |

4.0 |

|

30 |

μA |

|||

|

|

|

VDD = 10V |

|

|

|

8 |

|

0.05 |

8.0 |

|

60 |

μA |

||

|

|

|

VDD = 15V |

|

|

|

16 |

|

0.07 |

16.0 |

|

120 |

μA |

||

VOL |

LOW Level Output Voltage |

VIH = VDD, VIL = 0V, |

|

|

|

|

|

|

|

|

|||||

|

|

|

|IO| < 1 μA |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

VDD = 5V |

|

|

|

0.05 |

|

0 |

0.05 |

|

0.05 |

V |

||

|

|

|

VDD = 10V |

|

|

|

0.05 |

|

0 |

0.05 |

|

0.05 |

V |

||

|

|

|

VDD = 15V |

|

|

|

0.05 |

|

0 |

0.05 |

|

0.05 |

V |

||

VOH |

HIGH Level Output Voltage |

VIH = VDD, VIL = 0V, |

|

|

|

|

|

|

|

|

|||||

|

|

|

|IO| < 1 μA |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

VDD = 5V |

|

|

4.95 |

|

4.95 |

5 |

|

4.95 |

|

V |

||

|

|

|

VDD = 10V |

|

|

9.95 |

|

9.95 |

10 |

|

9.95 |

|

V |

||

|

|

|

VDD = 15V |

|

|

14.95 |

|

14.95 |

15 |

|

14.95 |

|

V |

||

VIL |

LOW Level Input Voltage |

|IO| < 1 μA |

|

|

|

|

|

|

|

|

|

|

|||

|

|

(CD4050BC Only) |

VDD = 5V, VO = 0.5V |

|

1.5 |

|

2.25 |

1.5 |

|

1.5 |

V |

||||

|

|

|

VDD = 10V, VO = 1V |

|

3.0 |

|

4.5 |

3.0 |

|

3.0 |

V |

||||

|

|

|

VDD = 15V, VO = 1.5V |

|

4.0 |

|

6.75 |

4.0 |

|

4.0 |

V |

||||

VIL |

LOW Level Input Voltage |

|IO| < 1 μA |

|

|

|

|

|

|

|

|

|

|

|||

|

|

(CD4049UBC Only) |

VDD = 5V, VO = 4.5V |

|

1.0 |

|

1.5 |

1.0 |

|

1.0 |

V |

||||

|

|

|

VDD = 10V, VO = 9V |

|

2.0 |

|

2.5 |

2.0 |

|

2.0 |

V |

||||

|

|

|

VDD = 15V, VO = 13.5V |

|

3.0 |

|

3.5 |

3.0 |

|

3.0 |

V |

||||

VIH |

HIGH Level Input Voltage |

|IO| < 1 μA |

|

|

|

|

|

|

|

|

|

|

|||

|

|

(CD4050BC Only) |

VDD = 5V, VO = 4.5V |

3.5 |

|

3.5 |

2.75 |

|

3.5 |

|

V |

||||

|

|

|

VDD = 10V, VO = 9V |

7.0 |

|

7.0 |

5.5 |

|

7.0 |

|

V |

||||

|

|

|

VDD = 15V, VO = 13.5V |

11.0 |

|

11.0 |

8.25 |

|

11.0 |

|

V |

||||

VIH |

HIGH Level Input Voltage |

|IO| < 1 μA |

|

|

|

|

|

|

|

|

|

|

|||

|

|

(CD4049UBC Only) |

VDD = 5V, VO = 0.5V |

4.0 |

|

4.0 |

3.5 |

|

4.0 |

|

V |

||||

|

|

|

VDD = 10V, VO = 1V |

8.0 |

|

8.0 |

7.5 |

|

8.0 |

|

V |

||||

|

|

|

VDD = 15V, VO = 1.5V |

12.0 |

|

12.0 |

11.5 |

|

12.0 |

|

V |

||||

IOL |

LOW Level Output Current |

VIH = VDD, VIL = 0V |

|

|

|

|

|

|

|

|

|||||

|

|

(Note 4) |

VDD = 5V, VO = 0.4V |

4.6 |

|

4.0 |

5 |

|

3.2 |

|

mA |

||||

|

|

|

VDD = 10V, VO = 0.5V |

9.8 |

|

8.5 |

12 |

|

6.8 |

|

mA |

||||

|

|

|

VDD = 15V, VO = 1.5V |

29 |

|

25 |

40 |

|

20 |

|

mA |

||||

IOH |

HIGH Level Output Current |

VIH = VDD, VIL = 0V |

|

|

|

|

|

|

|

|

|||||

|

|

(Note 4) |

VDD = 5V, VO = 4.6V |

−1.0 |

|

−0.9 |

−1.6 |

|

−0.72 |

|

mA |

||||

|

|

|

VDD = 10V, VO = 9.5V |

−2.1 |

|

−1.9 |

−3.6 |

|

−1.5 |

|

mA |

||||

|

|

|

VDD = 15V, VO = 13.5V |

−7.1 |

|

−6.2 |

−12 |

|

−5 |

|

mA |

||||

I |

IN |

Input Current |

V |

DD |

= 15V, V |

IN |

= 0V |

−0.3 |

|

−0.3 |

−10−5 |

|

|

−1.0 |

μA |

|

|

|

= 15V, V |

= 15V |

|

|

|

10−5 |

|

|

|

μA |

|||

|

|

|

V |

DD |

IN |

0.3 |

|

0.3 |

|

|

1.0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Note 3: VSS = 0V unless otherwise specified. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CD4050BC • CD4049UBC

3 |

www.fairchildsemi.com |

Loading...

Loading...