Fairchild Semiconductor CD4046BCN, CD4046BCMX, CD4046BCM, CD4046BCCW Datasheet

October 1987

Revised January 1999

CD4046BC

Micropower Phase-Locked Loop

General Description

The CD4046BC micropower phase-locked loop (PLL) consists of a low power, linear, voltage-controlled oscillator (VCO), a source follower, a zener diode, and two phase comparators. The two phase comparators have a common signal input and a common comparator input. The signal input can be directly coupled for a large voltage signal, or capacitively coupled to the self-biasing amplifier at the signal input for a small voltage signal.

Phase comparator I, an exclusive OR gate, provides a digital error signal (phase comp. I Out) and maintains 90° phase shifts at the VCO center frequency. Between signal input and comparator input (both at 50% duty cycle), it may lock onto the signal input frequencies that are close to harmonics of the VCO center frequency.

Phase comparator II is an edge-controlled digital memory network. It provides a digital error signal (phase comp. II Out) and lock-in signal (phase pulses) to indicate a locked condition and maintains a 0° phase shift between signal input and comparator input.

The linear voltage-controlled oscillator (VCO) produces an output signal (VCO Out) whose frequency is determined by the voltage at the VCOIN input, and the capacitor and resistors connected to pin C1A, C1B, R1 and R2.

The source follower output of the VCOIN (demodulator Out) is used with an external resistor of 10 kΩ or more.

The INHIBIT input, when high, disables the VCO and source follower to minimize standby power consumption. The zener diode is provided for power supply regulation, if necessary.

Features

■Wide supply voltage range: 3.0V to 18V

■Low dynamic power consumption: 70 μW (typ.) at fo = 10 kHz, VDD = 5V

■VCO frequency: 1.3 MHz (typ.) at VDD = 10V

■Low frequency drift: 0.06%/°C at VDD = 10V with temperature

■High VCO linearity: 1% (typ.)

Applications

•FM demodulator and modulator

•Frequency synthesis and multiplication

•Frequency discrimination

•Data synchronization and conditioning

•Voltage-to-frequency conversion

•Tone decoding

•FSK modulation

•Motor speed control

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

CD4046BCM |

M16A |

16-Lead Small Outline integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body |

|

|

|

CD4046BCN |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

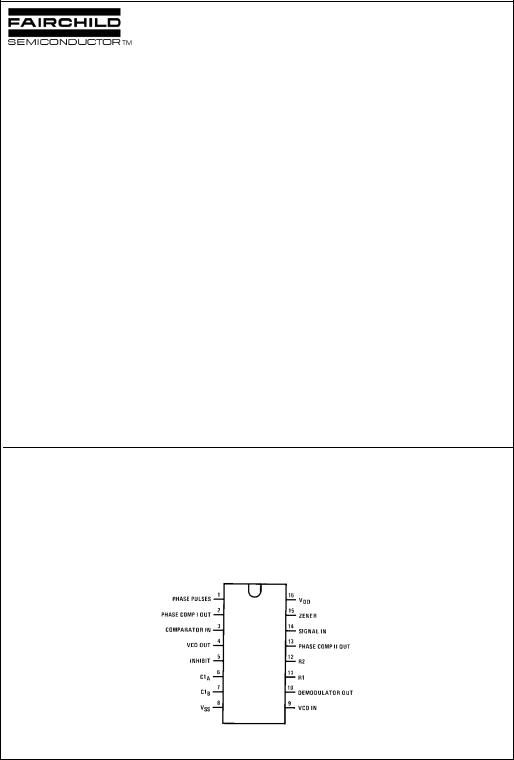

Connection Diagram

Pin Assignments for SOIC and DIP

Top View

Loop Locked-Phase Micropower CD4046BC

© 1999 Fairchild Semiconductor Corporation |

DS005968.prf |

www.fairchildsemi.com |

CD4046BC

Block Diagram

FIGURE 1.

www.fairchildsemi.com |

2 |

Absolute Maximum Ratings(Note 1)

(Note 2) |

|

|

DC Supply Voltage (VDD) |

−0.5 to +18 |

VDC |

Input Voltage (VIN) |

−0.5 to VDD +0.5 |

VDC |

Storage Temperature Range (TS) |

−65°C to +150°C |

|

Power Dissipation (PD) |

|

|

Dual-In-Line |

700 mW |

|

Small Outline |

500 mW |

|

Lead Temperature (TL) |

260°C |

|

(Soldering, 10 seconds) |

||

DC Electrical Characteristics (Note 2)

Recommended Operating

Conditions (Note 2)

DC Supply Voltage (VDD) |

3 to 15 VDC |

Input Voltage (VIN) |

0 to VDD VDC |

Operating Temperature Range (TA) |

−40°C to +85°C |

Note 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of “Recommended Operating Conditions” and “Electrical Characteristics” provides conditions for actual device operation.

Note 2: VSS = 0V unless otherwise specified.

Symbol |

Parameter |

|

|

|

Conditions |

−40°C |

|

+25°C |

|

+85°C |

Units |

|||

|

|

|

|

|

|

|

Min |

Max |

Min |

Typ |

Max |

Min |

Max |

|

|

|

|

|

|

|

|

|

|

|

|

||||

IDD |

Quiescent Device Current |

Pin 5 = VDD, Pin 14 = VDD, |

|

|

|

|

|

|

|

|

||||

|

|

Pin 3, 9 = VSS |

|

|

|

|

|

|

|

|

|

|||

|

|

VDD = |

5V |

|

|

20 |

|

0.005 |

20 |

|

150 |

μA |

||

|

|

VDD = |

10V |

|

|

40 |

|

0.01 |

40 |

|

300 |

μA |

||

|

|

VDD = |

15V |

|

|

80 |

|

0.015 |

80 |

|

600 |

μA |

||

|

|

Pin 5 = VDD, Pin 14 = Open, |

|

|

|

|

|

|

|

|

||||

|

|

Pin 3, 9 = VSS |

|

|

|

|

|

|

|

|

|

|||

|

|

VDD = |

5V |

|

|

70 |

|

5 |

55 |

|

205 |

μA |

||

|

|

VDD = |

10V |

|

|

530 |

|

20 |

410 |

|

710 |

μA |

||

|

|

VDD = |

15V |

|

|

1500 |

|

50 |

1200 |

|

1800 |

μA |

||

VOL |

LOW Level Output Voltage |

VDD = |

5V |

|

|

0.05 |

|

0 |

0.05 |

|

0.05 |

V |

||

|

|

VDD = |

10V |

|

|

0.05 |

|

0 |

0.05 |

|

0.05 |

V |

||

|

|

VDD = |

15V |

|

|

0.05 |

|

0 |

0.05 |

|

0.05 |

V |

||

VOH |

HIGH Level Output Voltage |

VDD = |

5V |

|

4.95 |

|

4.95 |

5 |

|

4.95 |

|

V |

||

|

|

VDD = |

10V |

|

9.95 |

|

9.95 |

10 |

|

9.95 |

|

V |

||

|

|

VDD = |

15V |

|

14.95 |

|

14.95 |

15 |

|

14.95 |

|

V |

||

VIL |

LOW Level Input Voltage |

VDD = |

5V, VO = 0.5V or 4.5V |

|

1.5 |

|

2.25 |

1.5 |

|

1.5 |

V |

|||

|

Comparator and Signal In |

VDD = |

10V, VO = 1V or 9V |

|

3.0 |

|

4.5 |

3.0 |

|

3.0 |

V |

|||

|

|

VDD = |

15V, VO = 1.5V or 13.5V |

|

4.0 |

|

6.25 |

4.0 |

|

4.0 |

V |

|||

VIH |

HIGH Level Input Voltage |

VDD = |

5V, VO = 0.5V or 4.5V |

3.5 |

|

3.5 |

2.75 |

|

3.5 |

|

V |

|||

|

Comparator and Signal In |

VDD = |

10V, VO = 1V or 9V |

7.0 |

|

7.0 |

5.5 |

|

7.0 |

|

V |

|||

|

|

VDD = |

15V, VO = 1.5V or 13.5V |

11.0 |

|

11.0 |

8.25 |

|

11.0 |

|

V |

|||

IOL |

LOW Level Output Current |

VDD = |

5V, VO = 0.4V |

0.52 |

|

0.44 |

0.88 |

|

0.36 |

|

mA |

|||

|

(Note 4) |

VDD = |

10V, VO = 0.5V |

1.3 |

|

1.1 |

2.25 |

|

0.9 |

|

mA |

|||

|

|

VDD = |

15V, VO = 1.5V |

3.6 |

|

3.0 |

8.8 |

|

2.4 |

|

mA |

|||

IOH |

HIGH Level Output Current |

VDD = |

5V, VO = 4.6V |

−0.52 |

|

−0.44 |

−0.88 |

|

−0.36 |

|

mA |

|||

|

(Note 4) |

VDD = |

10V, VO = 9.5V |

−1.3 |

|

−1.1 |

−2.25 |

|

−0.9 |

|

mA |

|||

|

|

VDD = 15V, VO = 13.5V |

−3.6 |

|

−3.0 |

−8.8 |

|

−2.4 |

|

mA |

||||

IIN |

Input Current |

All Inputs Except Signal Input |

|

|

|

−10−5 |

|

|

|

|

||||

|

|

V |

DD |

= 15V, V |

= 0V |

|

−0.3 |

|

−0.3 |

|

−1.0 |

μA |

||

|

|

|

= |

IN |

= 15V |

|

|

|

10−5 |

|

|

|

μA |

|

|

|

V |

DD |

15V, V |

|

0.3 |

|

0.3 |

|

1.0 |

||||

|

|

|

|

IN |

|

|

|

|

|

|

|

|

|

|

CIN |

Input Capacitance |

Any Input (Note 3) |

|

|

|

|

7.5 |

|

|

pF |

||||

PT |

Total Power Dissipation |

fo = 10 kHz, R1 = 1 MΩ, |

|

|

|

|

|

|

|

|

||||

|

|

R2 = ∞, ςΧΟΙΝ = ς /2 |

|

|

|

|

|

|

|

|

||||

|

|

VDD = |

5V |

|

|

|

|

0.07 |

|

|

|

mW |

||

|

|

VDD = |

10V |

|

|

|

|

0.6 |

|

|

|

mW |

||

|

|

VDD = |

15V |

|

|

|

|

2.4 |

|

|

|

mW |

||

Note 3: Capacitance is guaranteed by periodic testing.

Note 4: IOH and IOL are tested one output at a time.

CD4046BC

3 |

www.fairchildsemi.com |

CD4046BC

AC Electrical Characteristics (Note 5)

TA = 25°C, CL = 50 pF

Symbol |

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

VCO SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

IDD |

Operating Current |

fo = 10 kHz, R1 = 1 MW, |

|

|

|

|

|

|

R2 = ¥, VCOΙΝ = V /2 |

|

|

|

|

|

|

VDD = 5V |

|

20 |

|

mA |

|

|

VDD = 10V |

|

90 |

|

mA |

|

|

VDD = 15V |

|

200 |

|

mA |

fMAX |

Maximum Operating Frequency |

C1 = 50 pF, R1 = 10 kW, |

|

|

|

|

|

|

R2 = ¥, VCOΙΝ = V |

|

|

|

|

|

|

VDD = 5V |

0.4 |

0.8 |

|

MHz |

|

|

VDD = 10V |

0.6 |

1.2 |

|

MHz |

|

|

VDD = 15V |

1.0 |

1.6 |

|

MHz |

|

Linearity |

VCOIN = 2.5V ±0.3V, |

|

|

|

|

|

|

R1 ³ 10 kW, VDD = 5V |

|

1 |

|

% |

|

|

VCOIN = 5V ±2.5V, |

|

|

|

|

|

|

R1 ³ 400 kW, VDD = 10V |

|

1 |

|

% |

|

|

VCOIN = 7.5V ±5V, |

|

|

|

|

|

|

R1 ³ 1 MW, VDD = 15V |

|

1 |

|

% |

|

|

|

|

|

|

|

|

Temperature-Frequency Stability |

%/°Cµ1/f. V |

|

|

|

|

|

No Frequency Offset, fMIN = 0 |

R2 = ¥ |

|

|

|

|

|

|

VDD = 5V |

|

0.12–0.24 |

|

%/°C |

|

|

VDD = 10V |

|

0.04–0.08 |

|

%/°C |

|

|

VDD = 15V |

|

0.015–0.03 |

|

%/°C |

|

Frequency Offset, fMIN ¹ 0 |

VDD = 5V |

|

0.06–0.12 |

|

%/°C |

|

|

VDD = 10V |

|

0.05–0.1 |

|

%/°C |

|

|

VDD = 15V |

|

0.03–0.06 |

|

%/°C |

VCOIN |

Input Resistance |

VDD = 5V |

|

106 |

|

MW |

|

|

VDD = 10V |

|

106 |

|

MW |

|

|

VDD = 15V |

|

106 |

|

MW |

VCO |

Output Duty Cycle |

VDD = 5V |

|

50 |

|

% |

|

|

VDD = 10V |

|

50 |

|

% |

|

|

VDD = 15V |

|

50 |

|

% |

tTHL |

VCO Output Transition Time |

VDD = 5V |

|

90 |

200 |

ns |

tTHL |

|

VDD = 10V |

|

50 |

100 |

ns |

|

|

VDD = 15V |

|

45 |

80 |

ns |

PHASE COMPARATORS SECTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

RIN |

Input Resistance |

|

|

|

|

|

|

Signal Input |

VDD = 5V |

1 |

3 |

|

MW |

|

|

VDD = 10V |

0.2 |

0.7 |

|

MW |

|

|

VDD = 15V |

0.1 |

0.3 |

|

MW |

|

Comparator Input |

VDD = 5V |

|

106 |

|

MW |

|

|

VDD = 10V |

|

106 |

|

MW |

|

|

VDD = 15V |

|

106 |

|

MW |

|

AC-Coupled Signal Input Voltage |

CSERIES = 1000 pF |

|

|

|

|

|

Sensitivity |

f = 50 kHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD = 5V |

|

200 |

400 |

mV |

|

|

VDD = 10V |

|

400 |

800 |

mV |

|

|

VDD = 15V |

|

700 |

1400 |

mV |

|

|

|

|

|

|

|

www.fairchildsemi.com |

4 |

AC Electrical Characteristics (Continued)

Symbol |

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

DEMODULATOR OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

VCOIN- |

Offset Voltage |

RS ³ 10 kW, VDD = 5V |

|

1.50 |

2.2 |

V |

VDEM |

|

RS ³ 10 kW, VDD = 10V |

|

1.50 |

2.2 |

V |

|

|

RS ³ 50 kW, VDD = 15V |

|

1.50 |

2.2 |

V |

|

Linearity |

RS ³ 50 kW |

|

|

|

|

|

|

VCOIN = 2.5V ±0.3V, VDD = 5V |

|

0.1 |

|

% |

|

|

VCOIN = 5V ±2.5V, VDD = 10V |

|

0.6 |

|

% |

|

|

VCOIN = 7.5V ±5V, VDD = 15V |

|

0.8 |

|

% |

|

|

|

|

|

|

|

ZENER DIODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

VZ |

Zener Diode Voltage |

IZ = 50 mA |

6.3 |

7.0 |

7.7 |

V |

RZ |

Zener Dynamic Resistance |

IZ = 1 mA |

|

100 |

|

W |

Note 5: AC Parameters are guaranteed by DC correlated testing.

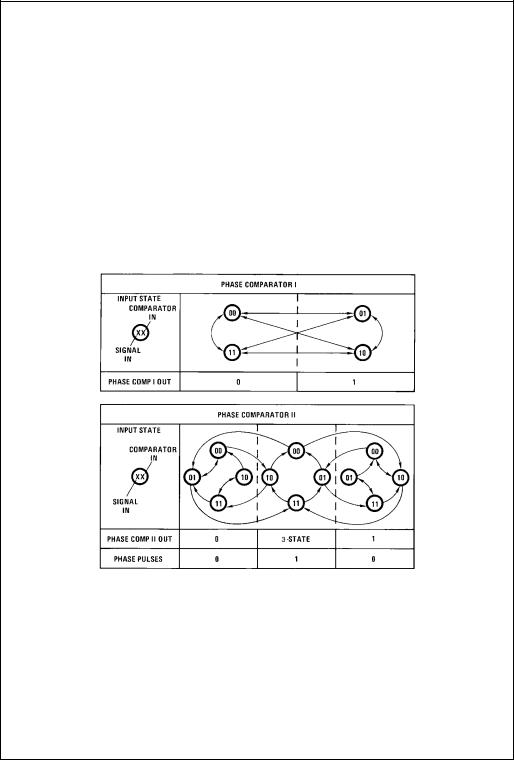

Phase Comparator State Diagrams

FIGURE 2.

CD4046BC

5 |

www.fairchildsemi.com |

Loading...

Loading...