Fairchild Semiconductor CD4514BCWMX, CD4514BCWM, CD4514BCN Datasheet

October 1987

Revised August 2000

CD4514BC• CD4515BC

4-Bit Latched/4-to-16 Line Decoders

General Description

The CD4514BC and CD4515BC are 4-to-16 line decoders with latched inputs implemented with complementary MOS (CMOS) circuits constructed with N- and P-channel enhancement mode transistors. These circuits are primarily used in decoding applications where low power dissipation and/or high noise immunity is required.

The CD4514BC (output active high option) presents a logical “1” at the selected output, whereas the CD4515BC presents a logical “0” at the selected output. The input latches are R–S type flip-flops, which hold the last input data presented prior to the strobe transition from “1” to “0”. This input data is decoded and the corresponding output is activated. An output inhibit line is also available.

Features

■Wide supply voltage range: 3.0V to 15V

■High noise immunity: 0.45 VDD (typ.)

■Low power TTL: fan out of 2 compatibility: driving 74L

■Low quiescent power dissipation:

0.025 µ W/package @ 5.0 VDC

■ Single supply operation

■ Input impedance = 1012Ω typically

■ Plug-in replacement for MC14514, MC14515

Ordering Code:

Order Number |

Package Number |

Package Diagram |

|

|

|

CD4514BCWM |

M24B |

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

CD4514BCN |

N24A |

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600 Wide |

|

|

|

CD4515BCWM |

M24B |

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

CD4515BCN |

N24A |

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

Connection Diagram

Top View

Decoders Line 16-to-Latched/4 Bit-4 CD4515BC CD4514BC•

© 2000 Fairchild Semiconductor Corporation |

DS005994 |

www.fairchildsemi.com |

CD4514BC• CD4515BC

Truth Table

Decode Truth Table (Strobe = 1)

|

|

Data Inputs |

|

Selected Output |

|||

Inhibit |

|

|

|

|

CD4514 = |

Logic “1” |

|

D |

C |

B |

A |

||||

|

|

|

|

|

CD4515 = |

Logic “0” |

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

S0 |

|

0 |

0 |

0 |

0 |

1 |

|

S1 |

|

0 |

0 |

0 |

1 |

0 |

|

S2 |

|

0 |

0 |

0 |

1 |

1 |

|

S3 |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

|

S4 |

|

0 |

0 |

1 |

0 |

1 |

|

S5 |

|

0 |

0 |

1 |

1 |

0 |

|

S6 |

|

0 |

0 |

1 |

1 |

1 |

|

S7 |

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

|

S8 |

|

0 |

1 |

0 |

0 |

1 |

|

S9 |

|

0 |

1 |

0 |

1 |

0 |

|

S10 |

|

0 |

1 |

0 |

1 |

1 |

|

S11 |

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

0 |

|

S12 |

|

0 |

1 |

1 |

0 |

1 |

|

S13 |

|

0 |

1 |

1 |

1 |

0 |

|

S14 |

|

0 |

1 |

1 |

1 |

1 |

|

S15 |

|

|

|

|

|

|

|

|

|

1 |

X |

X |

X |

X |

All Outputs = |

0, CD4514 |

|

|

|

|

|

|

All Outputs = |

1, CD4515 |

|

|

|

|

|

|

|

|

|

X = Don’t Care

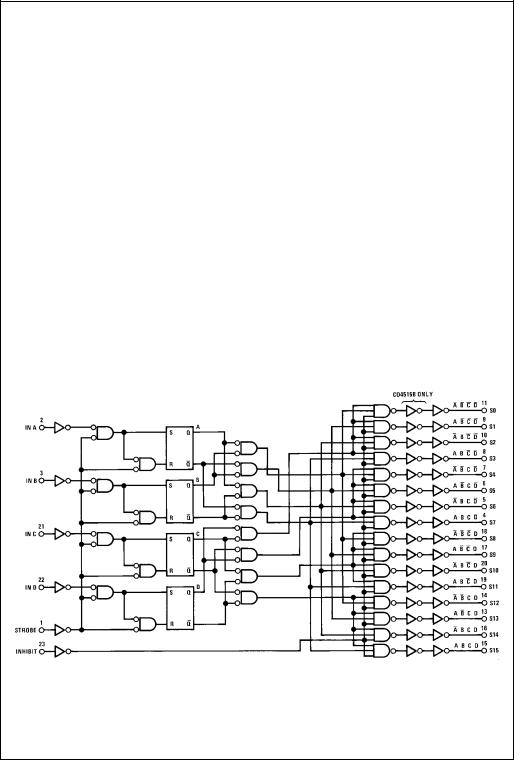

Logic Diagram

www.fairchildsemi.com |

2 |

Absolute Maximum Ratings(Note 1) |

Recommended Operating |

|

||||||||||||||||

(Note 2) |

|

|

|

|

|

Conditions (Note 2) |

|

|

|

|

|

|||||||

DC Supply Voltage (VDD) |

|

− 0.5V to + 18V |

|

DC Supply Voltage (VDD) |

|

|

|

|

3V to 15V |

|||||||||

Input Voltage (V ) |

− 0.5V to V |

|

+ 0.5V |

|

Input Voltage (V |

) |

|

|

|

|

|

0V to V |

||||||

|

IN |

|

DD |

|

|

|

|

|

IN |

|

|

|

|

|

DD |

|||

Storage Temperature Range (TS) |

|

− 65° C to + 150° C |

|

Operating Temperature Range (TA) |

|

|

|

|||||||||||

Power Dissipation (PD) |

|

|

|

|

|

CD4514BC, CD4515BC |

|

|

− 40° C to + 85° C |

|||||||||

Dual-In-Line |

|

|

700 mW |

Note 1: “Absolute Maximum Ratings” are those values beyond which the |

||||||||||||||

Small Outline |

|

|

500 mW |

safety of the device cannot be guaranteed. Except for “Operating Tempera- |

||||||||||||||

|

|

ture Range” they are not meant to imply that the devices should be oper- |

||||||||||||||||

|

|

|

|

|

|

|||||||||||||

Lead Temperature (TL) |

|

|

|

|

ated at these limits. The tables of “Recommended Operating Conditions” |

|||||||||||||

|

|

|

|

and “Electrical Characteristics” provide conditions for actual device opera- |

||||||||||||||

(Soldering, 10 seconds) |

|

|

|

260° C |

||||||||||||||

|

|

|

tion. |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

Note 2: VSS = |

0V unless otherwise specified. |

|

|

|

||||||||

DC Electrical Characteristics (Note 2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

CD4514BC, CD4515BC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Parameter |

|

Conditions |

|

|

− 40° C |

|

|

|

+ 25° C |

|

+ 85° C |

Units |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

Min |

Max |

|

Min |

|

|

Typ |

Max |

Min |

Max |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

IDD |

Quiescent Device |

VDD = |

5V, VIN = VDD or V SS |

|

|

|

20 |

|

|

|

0.005 |

20 |

|

150 |

µ A |

|||

|

Current |

VDD = |

10V, VIN = |

VDD or V SS |

|

|

40 |

|

|

|

0.010 |

40 |

|

300 |

µ A |

|||

|

|

VDD = |

15V, VIN = |

VDD or V SS |

|

|

80 |

|

|

|

0.015 |

80 |

|

600 |

µ A |

|||

VOL |

LOW Level |

VIL = |

0V, VIH = |

VDD, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage |

|IO| < |

1 µ A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD = |

5V |

|

|

|

|

|

0.05 |

|

|

|

|

0 |

0.05 |

|

0.05 |

V |

|

|

VDD = |

10V |

|

|

|

|

|

0.05 |

|

|

|

|

0 |

0.05 |

|

0.05 |

V |

|

|

VDD = |

15V |

|

|

|

|

|

0.05 |

|

|

|

|

0 |

0.05 |

|

0.05 |

V |

VOH |

HIGH Level |

VIL = |

0V, VIH = |

VDD, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage |

|IO| < |

1 µ A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD = |

5V |

|

|

|

|

4.95 |

|

|

4.95 |

|

|

5.0 |

|

4.95 |

|

V |

|

|

VDD = |

10V |

|

|

|

|

9.95 |

|

|

9.95 |

|

10.0 |

|

9.95 |

|

V |

|

|

|

VDD = |

15V |

|

|

|

|

14.95 |

|

|

14.95 |

|

15.0 |

|

14.95 |

|

V |

|

VIL |

LOW Level |

|IO| < |

1 µ A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltage |

VDD = |

5V, VO = |

0.5V or 4.5V |

|

|

|

1.5 |

|

|

|

2.25 |

1.5 |

|

1.5 |

V |

||

|

|

VDD = |

10V, VO = |

1.0V or 9.0V |

|

|

3.0 |

|

|

|

4.50 |

3.0 |

|

3.0 |

V |

|||

|

|

VDD = |

15V, VO = |

1.5V or 13.5V |

|

|

4.0 |

|

|

|

6.75 |

4.0 |

|

4.0 |

V |

|||

VIH |

HIGH Level |

|IO| < |

1 µ A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltage |

VDD = |

5V, VO = |

0.5V or 4.5V |

|

|

3.5 |

|

|

3.5 |

|

2.75 |

|

3.5 |

|

V |

||

|

|

VDD = |

10V, VO = |

1.0V or 9.0V |

|

7.0 |

|

|

7.0 |

|

5.50 |

|

7.0 |

|

V |

|||

|

|

VDD = |

15V, VO = |

1.5V or 13.5V |

|

11.0 |

|

|

11.0 |

|

8.25 |

|

11.0 |

|

V |

|||

IOL |

LOW Level Output |

VDD = |

5V, VO = |

0.4V |

|

|

0.52 |

|

|

0.44 |

|

0.88 |

|

0.36 |

|

mA |

||

|

Current (Note 3) |

VDD = |

10V, VO = |

0.5V |

|

|

1.3 |

|

|

1.1 |

|

2.25 |

|

0.90 |

|

mA |

||

|

|

VDD = |

15V, VO = |

1.5V |

|

|

3.6 |

|

|

3.0 |

|

|

8.8 |

|

2.4 |

|

mA |

|

IOH |

HIGH Level Output |

VDD = |

5V, VO = |

4.6V |

|

|

− 0.52 |

|

|

− 0.44 |

|

− |

0.88 |

|

− 0.36 |

|

mA |

|

|

Current (Note 3) |

VDD = |

10V, VO = |

9.5V |

|

|

− 1.3 |

|

|

− 1.1 |

|

− |

2.25 |

|

− 0.90 |

|

mA |

|

|

|

VDD = |

15V, VO = |

13.5V |

|

|

− 3.6 |

|

|

− 3.0 |

|

− 8.8 |

|

− 2.4 |

|

mA |

||

IIN |

Input Current |

VDD = |

15V, VIN = |

0V |

|

|

|

− 0.3 |

|

|

|

− |

10− 5 |

− 0.3 |

|

− 1.0 |

µ A |

|

|

|

VDD = |

15V, VIN = |

15V |

|

|

|

0.3 |

|

|

|

10− 5 |

0.3 |

|

1.0 |

µ A |

||

Note 3: IOH and IOL are tested one output at a time.

CD4515BC CD4514BC•

3 |

www.fairchildsemi.com |

Loading...

Loading...