Fairchild Semiconductor CD4030CSJX, CD4030CSJ, CD4030CN Datasheet

October 1987

Revised January 1999

CD4030C

Quad EXCLUSIVE-OR Gate

General Description

The CD4030C EXCLUSIVE-OR gates are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. All inputs are protected against static discharge with diodes to VDD and VSS.

Features

■Wide supply voltage range: 3.0V to 15V

■Low power: 100 nW (typ.)

■Medium speed operation:

tPHL = tPLH = 40 ns (typ.) at CL = 15 pF, 10V supply

■ High noise immunity 0.45 VCC (typ.)

Applications

•Automotive

•Data terminals

•Instrumentation

•Medical electronics

•Industrial controls

•Remote metering

•Computers

Ordering Code:

Order Number |

Package Number |

|

Package Description |

|

|

||

|

|

|

|

|

|

|

|

CD4030CSJ |

M14D |

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|||

|

|

|

|

|

|

|

|

CD4030CN |

N14A |

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|||||

|

|

|

|

|

|

|

|

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code. |

|

|

|

|

|||

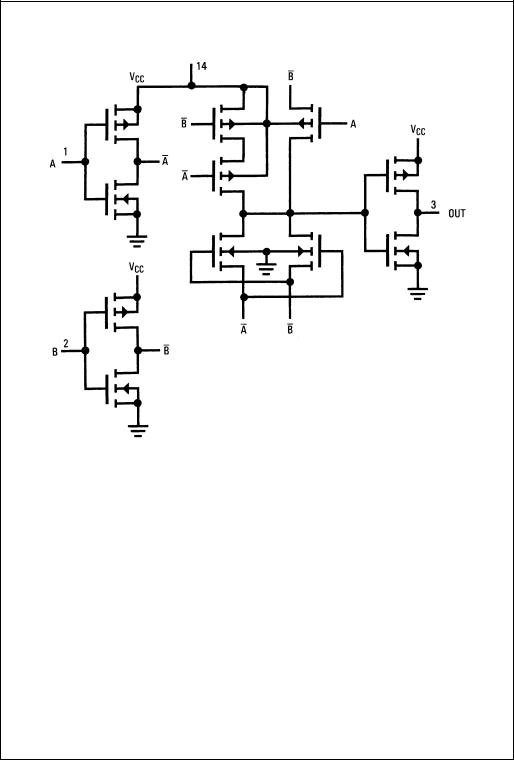

Connection Diagram |

Truth Table |

|

|

|

|

||

Pin Assignments for DIP and SOP |

|

|

|

|

|||

|

|

|

A |

B |

|

J |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

1 = HIGH Level

0 = LOW Level

Gate OR-EXCLUSIVE Quad CD4030C

© 1999 Fairchild Semiconductor Corporation |

DS005961.prf |

www.fairchildsemi.com |

CD4030C

Logic Diagram

www.fairchildsemi.com |

2 |

Loading...

Loading...