TEXAS INSTRUMENTS UC1827-1, UC1827-2, UC2827-1, UC2827-2, UC3827-1 Technical data

...

UC1827

UC1827-1, UC1827-2

UC2827-1, UC2827-2

UC3827-1, UC3827-2

www.ti.com |

SLUS365A –APRIL 1999 –REVISED AUGUST 2005 |

|

BUCK CURRENT/VOLTAGE FED PUSH-PULL

PWM CONTROLLERS

FEATURES

∙Ideal for Multiple Output and/or High Voltage Output Voltage Converters

∙Up to 500 kHz Operation

∙High Voltage, High Current Floating Driver for Buck Converter Stage

∙UC3827-1 Current Fed Controller has Push-Pull Drivers with Overlapping Conduction Periods

∙UC3827-2 Voltage Fed Controller has Push-Pull Drivers with Nonoverlapping Conduction Periods

∙Average Current Mode, Peak Current Mode or Voltage Mode with Input Voltage Feedforward Control for Buck Power Stage

∙Wide Bandwidth, Low Offset, Differential Current Sense Amplifier

∙Precise Short Circuit Current Control

DESCRIPTION

The UC3827 family of controller devices provides an integrated control solution for cascaded buck and push-pull converters. These converters are known as current fed or voltage fed push-pull converters and are ideally suited for multiple output and/or high voltage output applications. In both current fed and voltage fed modes, the push-pull switches are driven at 50% nominal duty cycles and at one half the switching frequency of the buck stage. In the current fed mode, the two switches are driven with a specified over-lap period to prevent ringing and voltage stress on the devices. In the voltage fed mode, the two switches are driven with a specified gap time between the switches to prevent shorting the transformer across the energy storage capacitor and to prohibit excessive currents flowing through the devices.

The converter'soutput voltage is regulated by pulse width modulation of the buck switch. The UC3827 contains complete protection and PWM control functions for the buck converter. Easy control of the floating switch is accomplished by the floating drive circuitry. The gate drive waveform is level shifted to support an input voltage up to 72 VDC.

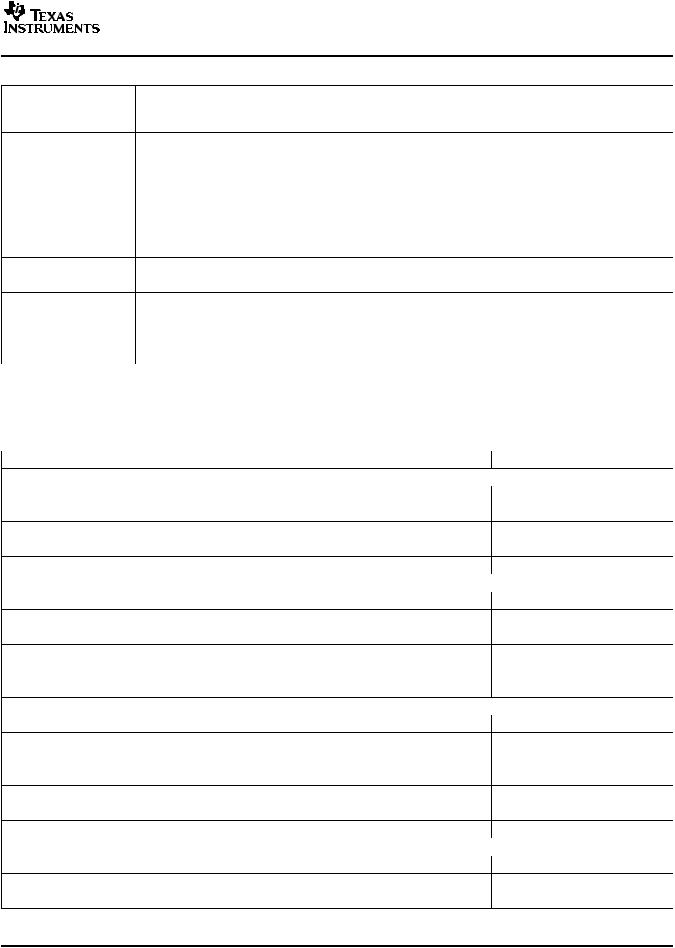

BLOCK DIAGRAM

VEAOCEA+ CEAO RAMP

|

|

10 |

12 |

6 |

5 |

|

|

|

|

|

|

|

|

Voltage Error |

|

|

|

|

|

|

|

|

|

VEA+ 14 |

Amplifier |

|

|

|

|

|

|

|

|

|

|

|

|

|

0.7 V |

PWM Comparator |

|

|

|

|

|||

|

|

|

Current Error |

|

|

|

|

||||

VEA− |

16 |

|

+ |

|

|

|

|

|

|

||

|

Amplifier |

|

|

|

|

|

|

|

|||

CEA− 13 |

|

|

|

|

|

|

|

|

|

|

|

CSAO 7 |

|

|

|

|

|

RD |

|

Flying |

1 |

V+ |

|

|

|

|

+3 V |

|

|

|

|

|

Driver |

||

CSA+ |

8 |

|

|

|

|

|

|

|

|

||

|

ILIM Comparator |

|

|

S |

Q |

|

2 |

BUCK |

|||

|

|

|

|

|

|

|

|

||||

CSA− |

9 |

Current Sense |

|

|

|

|

|

|

3 |

SRC |

|

|

|

|

|

|

|

|

|

||||

SS |

4 |

Amplifier |

|

SS |

|

|

OSC |

|

|

|

|

|

|

INHBT |

|

|

|

|

|

|

|||

SYNC 19 |

|

|

|

|

|

|

|

21 |

PGND |

||

|

|

UV |

|

|

|

|

|

||||

CT |

18 |

OSC |

|

|

|

Q |

DELAY |

|

|

|

|

500 kHz |

|

|

T |

|

|

|

|

|

|||

RT 17 |

|

|

|

|

|

Push/Pull |

|

|

|||

MAX |

|

|

|

Q |

|

|

|

|

|||

|

|

|

|

|

|

|

|

Drivers |

|

|

|

REF 15 |

|

|

|

|

|

|

|

|

24 |

PUSH |

|

|

|

|

|

|

|

|

|

|

|

||

VCC 23 |

REF |

|

|

|

|

|

|

|

|

|

|

|

|

& |

UVLO |

|

|

|

DELAY |

|

|

22 |

PULL |

GND |

11 |

UVLO |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

20 |

|

|

|

|

|

|

|

|

|

|

|

DELAY |

|

|

|

|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. |

Copyright © 1999–2005, Texas Instruments Incorporated |

Products conform to specifications per the terms of the Texas |

|

Instruments standard warranty. Production processing does not |

|

necessarily include testing of all parameters. |

|

UC1827-1, UC1827-2

UC2827-1, UC2827-2

UC3827-1, UC3827-2

www.ti.com

SLUS365A –APRIL 1999 –REVISED AUGUST 2005

DESCRIPTION (CONTINUED)

The UC3827 can be set up in traditional voltage mode control using input voltage feedforward technique or in current mode control. Using current mode control prevents potential core saturation of the push-pull transformer due to mismatches in timing and in component tolerances. With average current mode control, precise control of the inductor current feeding the push-pull stage is possible without the noise sensitivity associated with peak current mode control. The UC3827 average current mode loop can also be connected in parallel with the voltage regulation loop to assist only in fault conditions.

Other valuable features of the UC3827 include bidirectional synchronization capability, user programmable overlap time (UC3827-1), user programmable gap time (UC3827-2), a high bandwidth differential current sense amplifier, and soft start circuitry.

ORDERING INFORMATION(1)

TA = TJ |

PUSH-PULL TOPOLOGY |

|

PACKAGES |

|

|

SOIC-24 |

PDIP-24 |

PLCC-28 |

|||

|

|

||||

-55°C to 125°C |

Current Fed |

UC1827J-1 |

UC1827J-1 |

|

|

Voltage Fed |

UC1827J-2 |

UC1827J-2 |

|

||

|

|

||||

-40°C to 85°C |

Current Fed |

UC2827DW-1 |

UC2827N-1 |

- |

|

Voltage Fed |

UC2827DW-2 |

UC2827N-2 |

- |

||

|

|||||

0°C to 70°C |

Current Fed |

UC3827DW-1 |

UC3827N-1 |

UC3827Q-1 |

|

Voltage Fed |

UC3827DW-2 |

UC3827N-2 |

- |

||

|

(1)The DW and Q packages are also available taped and reeled. Add a TR suffix to the device type (i.e., UC2827DWTR-1).

DISSIPATION RATINGS

PACKAGE |

(θJA) JUNCTION-TO-AMBIENT |

(θJC) JUNCTION-TO-WHAT? |

|

TEMPERATURE (°C/W) |

TEMPERATURE (°C/W) |

24-pin (N) |

60(1) |

30 |

24-pin (J) |

70 to 90 |

28(2) |

28-pin (DW) |

71 to 83(3) |

24(3) |

28-pin (QLCC) |

40-65(1) |

30 |

(1)Specified θJA (junction-to-ambient) refers to devices mounted to 5-in2 FR4 PC board with 1 oz. copper where noted. When a resistance range is given, the lower values refer to a 5-in2 aluminum PC board. The test PWB is 0.062 inches thick and typically used 0.635 mm trace widths for power packages and 1.3 mm trace widths for non-power packages with a 100 × 100 mil probe land area at the end of each trace.

(2)Specified θJC (junction-to-what?) data values stated were derived from MIL-STD-1835B which states "The baseline values shown are worst case (mean + 2s) for a 60 x 60 mil microcircuit device silicon die and applicable for devices with die sizes up to 14400 mils2. For device sizes greater than 14400 mils2 use the following values; dual-in-line, 11 °C/W; flat pack, 10 °C/W; pin grid array, 10 °C/W pin grid array, 10 °C/W."

(3)Modeled data. If there is a value range given for θJA, the lower value refers to a 3 x 3 in., 1-oz, internal copper ground plane. The higher value refers to a 1 x 1 in. ground plane. All model data assumes only one trace for each non-fused lead.

2

UC1827-1, UC1827-2 UC2827-1, UC2827-2

UC3827-1, UC3827-2

www.ti.com

SLUS365A –APRIL 1999 –REVISED AUGUST 2005

ABSOLUTE MAXIMUM RATINGS(1)

Supply voltage, VCC

Supply voltage, VCC

Input voltage range

Input voltage range

BUCK driver

BUCK driver

PUSH/PULL driver

PUSH/PULL driver

|

UC2827-1 |

|

|

|

UC2827-2 |

UNITS |

|

|

UC3827-1 |

||

|

|

||

|

UC3827-2 |

|

|

|

20 |

|

|

CEAO, CEA+, CEA-, CSAO, CSA+, CSA-, CT, DELAY, PUSH, PULL, |

–0.3 to 5 |

|

|

RAMP, RT, SS, SYNC, VEA+, VEAO, |

V |

||

|

|||

V+ and BUCK |

90 |

|

|

SRC |

90-VCC |

|

|

I/O continuous |

±250 |

mA |

|

I/O peak |

±1 |

A |

|

I/O continuous |

±200 |

mA |

|

I/O peak |

±0.8 |

A |

Storage temperature |

–65 to 150 |

|

Junction temperature |

–55 to 150 |

°C |

Lead temperature (soldering, 10 sec) |

300 |

|

(1)Voltages are referenced to ground. Currents are positive into, negative out of the specified terminal. Consult Packaging section of databook for thermal limitations and considerations of packages.

CONNECTION DIAGRAMS

DIL-24 (N or J, DW PACKAGES) (TOP VIEW)

N, J OR DW PACKAGES

(TOP VIEW)

V+ |

|

|

1 |

24 |

|

|

PUSH |

|

|

|

|

||||

BUCK |

|

2 |

23 |

|

|

VCC |

|

|

|

|

|

||||

SRC |

|

3 |

22 |

|

|

PULL |

|

|

|

|

|

||||

SS |

|

4 |

21 |

|

|

PGND |

|

|

|

|

|

||||

RAMP |

|

5 |

20 |

|

|

DELAY |

|

|

|

|

|

||||

CEAO |

|

6 |

19 |

|

|

SYNC |

|

|

|

|

|

||||

CSAO |

|

7 |

18 |

|

|

CT |

|

|

|

|

|

||||

CSA+ |

|

8 |

17 |

|

|

RT |

|

|

|

|

|

||||

CSA− |

|

9 |

16 |

|

|

VEA− |

|

|

|

|

|

||||

VEAO |

|

10 |

15 |

|

|

REF |

|

|

|

|

|

||||

GND |

|

11 |

14 |

|

|

VEA+ |

|

|

|

|

|

||||

CEA+ |

|

|

12 |

13 |

|

|

CEA− |

|

|

|

|

||||

|

|

|

|

|

|

|

|

PLCC-28 (Q PACKAGE)

(TOP VIEW)

Q PACKAGE (TOP VIEW)

|

SRC |

BUCK |

NC |

V+ |

PUSH |

VCC |

PULL |

|

SS |

4 |

3 |

2 |

1 |

28 27 26 |

PGND |

||

5 |

|

|

|

|

|

25 |

||

RAMP |

6 |

|

|

|

|

|

24 |

NC |

CEAO |

7 |

|

|

|

|

|

23 |

NC |

CSAO |

8 |

|

|

|

|

|

22 |

DELAY |

CSA+ |

9 |

|

|

|

|

|

21 |

SYNC |

CSA− |

10 |

|

|

|

|

|

20 |

CT |

VEAO |

11 |

|

|

|

|

|

19 |

RT |

|

12 13 14 15 16 17 18 |

|

||||||

|

GND |

CEA+ |

CEA− |

VEA+ |

REF |

NC |

VEA− |

|

NC − No internal connection

3

UC1827-1, UC1827-2

UC2827-1, UC2827-2

UC3827-1, UC3827-2

www.ti.com

SLUS365A –APRIL 1999 –REVISED AUGUST 2005

|

|

|

|

|

Terminal Functions |

|

TERMINAL |

|

|

|

|

NAME |

N or |

Q |

I/O |

DESCRIPTION |

|

DW |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

Output of the buck PWM controller. The BUCK output is a floating driver, optimized for controlling the |

BUCK |

|

2 |

3 |

O |

gate of an N-channel MOSFET. The peak sink and source currents are 1 A. VCC undervoltage faults |

|

|

|

|

|

disables BUCK to an off condition (low). |

CEA+ |

|

12 |

13 |

I |

Non-inverting input of the current error amplifier. |

CEA- |

|

13 |

14 |

I |

Inverting input of the current error amplifier |

CEAO |

|

6 |

7 |

O |

Output of the current error amplifier and the inverting input of the PWM comparator of the buck |

|

converter. |

||||

|

|

|

|

|

|

CSA+ |

|

8 |

9 |

I |

Noninverting input of the current sense amplifier. |

CSA– |

|

9 |

10 |

I |

Inverting input of the current sense amplifier. |

|

|

|

|

|

Output of the current sense amplifier and the noninverting input of the current limit comparator. When |

CSAO |

|

7 |

8 |

O |

the signal level on this pin exceeds the 3V threshold of the current limit comparator, the buck gate drive |

|

pulse is terminated. This feature is useful to implement cycle-by-cycle current limiting for the buck |

||||

|

|

|

|

|

|

|

|

|

|

|

converter. |

|

|

|

|

|

Provides for the timing capacitor which is connected between CT and GND. The oscillator frequency is |

CT |

|

18 |

20 |

I |

set by CT and a resistor RT, connected between pin RT and GND. The CT discharge current is |

|

approximately 40 x the bias current through the resistor connected to RT. A practical maximum value for |

||||

|

|

|

|

|

|

|

|

|

|

|

the discharge current is 20 mA. The frequency of the oscillator is given by equation(1) |

|

|

|

|

|

A resistor to GND programs the overlap time of the PUSH and PULL outputs of the UC3827-1 and the |

DELAY |

|

20 |

22 |

I |

dead time of the PUSH and PULL outputs of the UC3827-2. The minimum value of the resistor, RDELAY, |

|

|

|

|

|

is 18 kΩ. The delay or overlap time is given by equation(2) |

GND |

|

11 |

12 |

- |

Ground reference for all sensitive setup components not related to driving the outputs. They include all |

|

timing, voltage sense, current sense, and bypass components. |

||||

|

|

|

|

|

|

|

|

|

|

|

Ground connection for the PUSH and PULL outputs. PGND must be connected to GND at a single point |

PGND |

|

21 |

25 |

- |

on the printed circuit board. This is imperative to prevent large, high frequency switching currents |

|

|

|

|

|

flowing through the ground metalization inside the device. |

|

|

|

|

|

Ground referenced output to drive an N-channel MOSFET. The PULL and the PUSH outputs are driving |

PULL |

|

22 |

26 |

O |

the two switches of the push-pull converter with complementary signals at close to a 50% duty cycle. |

|

|

|

|

|

Any undervoltage faults will disable PULL to an off condition (low). |

|

|

|

|

|

Ground referenced output to drive an N-channel MOSFET. The PULL and the PUSH outputs are driving |

PUSH |

|

24 |

28 |

O |

the two switches of the push-pull converter with complementary signals at close to a 50% duty cycle. |

|

|

|

|

|

Any undervoltage faults disables PUSH to an off condition (low). |

|

|

|

|

|

The RAMP voltage, after a 700 mV internal level shift, is fed to the noninverting input of the buck PWM |

|

|

|

|

|

comparator. A resistor to VIN and a capacitor to GND provide an input voltage feedforward signal for the |

RAMP |

|

5 |

6 |

I |

buck controller in voltage mode control. In peak current mode control, the RAMP pin receives the |

|

current signal of the buck converter. In an average current mode setup, the RAMP pin has a linearly |

||||

|

|

|

|

|

|

|

|

|

|

|

increasing ramp signal. This waveform may be generated either by connecting RAMP directly to CT, or |

|

|

|

|

|

by connecting both a resistor from VCC to RAMP and a capacitor from RAMP to GND. |

REF |

|

15 |

16 |

O |

The output of the +5V on board reference. Bypass this pin with a capacitor to GND. The reference is off |

|

when the chip is in undervoltage lockout mode.o |

||||

|

|

|

|

|

|

|

|

|

|

|

A resistor to GND programs the charge current of the timing capacitor connected to CT. The charge |

|

|

|

|

|

current approximately equals that shown in equation(3). The charge current should be less than 500 µA |

RT |

|

17 |

19 |

I |

to keep CT'sdischarge peak current less than 20 mA, which is CT'smaximum practical discharge value. |

|

|

|

|

|

The discharge time, which sets the maximum duty cycle, is set internally and is influenced by the charge |

|

|

|

|

|

current. |

|

|

|

|

|

The source connection for the floating buck switch. The voltage on the SRC pin can exceed VCC but |

SRC |

|

3 |

4 |

I |

must be lower than 90 V–VVCC. Also, during turn-off transients of the buck switch, the voltage at SRC |

|

|

|

|

|

can go to –2V. |

f |

OSC |

|

0.77 |

(Hz) |

|

|

|||||

(1) |

RRT |

CCT |

|

||

|

|

||||

tDELAY RDELAY 10 9 (s)

(2)200

2.5 V

(3) IRT RRT

4

UC1827-1, UC1827-2 UC2827-1, UC2827-2

UC3827-1, UC3827-2

www.ti.com

|

|

|

|

|

SLUS365A –APRIL 1999 –REVISED AUGUST 2005 |

|

|

|

|

|

Terminal Functions (continued) |

|

TERMINAL |

|

|

|

|

NAME |

N or |

Q |

I/O |

DESCRIPTION |

|

DW |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

5Soft-start pin requires a capacitor to GND. During soft-start the output of the voltage error amplifier is |

SS |

|

4 |

5 |

O |

clamped to the soft-start capacitor voltage which is slowly charged by an internal current source. In |

|

|

|

|

|

UVLO, SS is held low. |

|

|

|

|

|

A bidirectional pin for the oscillator., used to synchronize several chips to the fastest oscillator. Its input |

SYNC |

|

19 |

21 |

I |

synchronization threshold is 1.4 V. The SYNC voltage is 3.6 V when the oscillator capacitor, CT, is |

|

discharged. Otherwise it is 0 V. If the recommended synchronization circuit is not used, a 1 kΩ or lower |

||||

|

|

|

|

|

|

|

|

|

|

|

value resistor from SYNC to GND may be needed to increase the fall time of the signal at SYNC. |

VCC |

|

23 |

27 |

I |

A voltage source connected to this pin supplies the power for the UC3827. It is recommended to bypass |

|

this pin to both GND and PGND ground connections with good quality high frequency capacitors |

||||

|

|

|

|

|

|

VEA+ |

|

14 |

15 |

I |

Non-inverting input of the voltage error amplifier |

VEA- |

|

16 |

18 |

I |

Inverting input of the voltage error amplifier |

VEAO |

|

10 |

11 |

O |

Output of the voltage error amplifier |

|

|

|

|

|

Supply voltage for the buck output. The floating driver of the UC3827 uses the bootstrap technique |

V+ |

|

1 |

1 |

I |

which requires a reservoir capacitor to store the required energy for the on time of the buck switch. A |

|

diode must be connected from VCC to V+ to charge the reservoir capacitor. This diode must be able to |

||||

|

|

|

|

|

|

withstand VIN. The reservoir capacitor must be connected between V+ and SRC.

ELECTRICAL CHARACTERISTICS

Unless otherwise spsecified, VVCC = 15 V, VV+ = 14.3 V, CCT = 340 pF, RRT = 10 kΩ, RDELAY = 24.3 kΩ, VSRC = VGND = VBUCK= VPUSH = VPULL outputs no load, TJ = TA

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

SUPPLY |

|

|

|

|

|

|

|

VCC UVLO, Turn-on |

|

8.3 |

8.8 |

9.5 |

V |

|

Hysteresis |

|

0.9 |

1.2 |

1.5 |

V |

IVCC |

Supply current start |

VVCC = 8 V |

|

|

1000 |

µA |

IVCC |

Supply current run |

|

|

32 |

45 |

mA |

|

IV+ buck high |

|

0.2 |

1 |

2 |

mA |

VOLTAGE ERROR AMPLIFIER |

|

|

|

|

|

|

IB |

|

|

|

0.5 |

3 |

µA |

VIO |

|

|

|

|

10 |

mV |

AVOL |

|

|

80 |

95 |

|

dB |

GBW(1) |

Gain bandwidth |

|

1 |

4 |

|

MHz |

VOL |

Low-level output voltage |

IVEAO = 0 µA (No load) |

|

0.3 |

0.5 |

V |

VOH |

High-level output voltage |

IVEAO = 0 µA (No load) |

2.85 |

3 |

3.20 |

V |

CURRENT SENSE AMPLIFIER |

|

|

|

|

|

|

IB |

|

|

|

–1 |

–5 |

µA |

VIO |

|

|

|

|

5 |

mV |

AVOL |

|

|

80 |

110 |

|

dB |

GBW (1) |

Gain bandwidth |

|

15 |

29 |

|

MHz |

VOL |

Low-level output voltage |

ICEAO = 0 µA (No load) |

|

0.25 |

0.5 |

V |

VOH |

High-level output voltage |

ICEAO = 0 µA (No load) |

3 |

3.3 |

|

V |

CMRR |

Common mode range(1) |

|

-0.3 |

|

2 |

V |

CURRENT ERROR AMPLIFIER |

|

|

|

|

|

|

IB |

|

|

|

–1 |

–5 |

µA |

VIO |

|

|

|

|

10 |

mV |

AVOL |

|

|

80 |

110 |

|

dB |

(1)Ensured by design. Not production tested.

5

Loading...

Loading...