Texas Instruments TVP3026-250BPCE, TVP3026-250BMDN, TVP3026-250APCE, TVP3026-250AMDN, TVP3026-220BPCE Datasheet

...

TVP3026

Data Manual

Video Interface Palette

SLAS098B

July 1996

Printed on Recycled Paper

IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright 1996, Texas Instruments Incorporated

ii

Contents

Section |

|

|

|

Title |

Page |

|

1 |

Introduction . |

. . |

. |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 1–1 |

|

|

1.1 |

Features |

. . |

. |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1–2 |

|

1.2 |

Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1–3 |

|||

|

1.3 |

Terminal Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1–4 |

|||

|

1.4 |

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1–5 |

|||

|

1.5 |

Terminal Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

1–5 |

|||

2 |

Detailed Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–1 |

||||

|

2.1 |

Microprocessor Unit Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–1 |

|||

|

|

2.1.1 |

|

|

Operation |

2–3 |

|

|

8/6 |

||||

|

|

2.1.2 |

Pixel Read-Mask Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–3 |

||

|

|

2.1.3 |

Palette-Page Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–3 |

||

|

|

2.1.4 |

Cursor and Overscan Color Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–4 |

||

|

2.2 |

Color-Palette RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–4 |

|||

|

|

2.2.1 |

Writing to Color-Palette RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–5 |

||

|

|

2.2.2 |

Reading From Color-Palette RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–5 |

||

|

2.3 |

Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–5 |

|||

|

2.4 |

PLL Clock Generators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–6 |

|||

|

|

2.4.1 |

Pixel Clock PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–8 |

||

|

|

2.4.2 |

Memory Clock PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–10 |

||

|

|

2.4.3 |

Loop Clock PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–12 |

||

|

2.5 |

Frame-Buffer Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–16 |

|||

|

|

2.5.1 |

Frame-Buffer Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–17 |

||

|

|

2.5.2 |

Frame-Buffer Timing Without Using SCLK . . . . . . . . . . . . . . . . . . . . . . . |

2–17 |

||

|

|

2.5.3 |

Frame-Buffer Timing Using SCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–17 |

||

|

|

2.5.4 |

Split Shift-Register-Transfer Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–18 |

||

|

2.6 |

Multiplexing Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–19 |

|||

|

|

2.6.1 |

Little-Endian and Big-Endian Data Format . . . . . . . . . . . . . . . . . . . . . . . |

2–19 |

||

|

|

2.6.2 |

VGA Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–19 |

||

|

|

2.6.3 |

Pseudo-Color Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–19 |

||

|

|

2.6.4 |

Direct-Color Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–20 |

||

|

|

2.6.5 |

True-Color Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–20 |

||

|

|

2.6.6 |

Packed-24 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–21 |

||

|

|

2.6.7 |

Multiplex-Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–23 |

||

|

2.7 |

On-Chip Cursor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–31 |

|||

|

|

2.7.1 |

Cursor RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–31 |

||

|

|

2.7.2 |

Cursor Positioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–32 |

||

|

|

2.7.3 |

Three-Color 64 x 64 Cursor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–33 |

||

|

|

2.7.4 |

Interlaced Cursor Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–34 |

||

iii

Contents (Continued)

Section |

Title |

Page |

2.8 Port-Select and Color-Key Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–34 2.8.1 Port-Select Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–35 2.8.2 Color-Key Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–35 2.9 Overscan Border . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–36

2.10 Horizontal Zooming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–37 2.11 Test Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–37 2.11.1 16-Bit CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–37 2.11.2 Sense Comparator Output and Test Register . . . . . . . . . . . . . . . . . . . . . 2–38 2.11.3 Identification Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–38 2.11.4 Silicon Revision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–39 2.12 General-Purpose I/O Register and Terminals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–39 2.13 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–39 2.14 Analog Output Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–39 2.15 Register Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–42 2.15.1 General-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–42 2.15.2 Miscellaneous-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–42 2.15.3 Indirect Cursor-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–43 2.15.4 Direct Cursor-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–43 2.15.5 Cursor-Position (x, y) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–44 2.15.6 Color-Key Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–45 2.15.7 Color-Key (Overlay, Red, Green, Blue) Registers . . . . . . . . . . . . . . . . . 2–46 2.15.8 CRC Remainder LSB and MSB Registers . . . . . . . . . . . . . . . . . . . . . . . 2–46 2.15.9 CRC Bit Select Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–46

3 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

3.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range . . . . 3–1 3.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1 3.3 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2 3.4 Operating Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3 3.5 Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4 3.6 Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5 3.7 Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Appendix A |

Frequency Synthesis PLL Register Settings . . . . . . . . . . . . . . . . . . . . . . |

A–1 |

Appendix B |

PLL Programming Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

B–1 |

Appendix C |

Recommended Clock Programming Procedures . . . . . . . . . . . . . . . . . . |

C–1 |

Appendix D |

PC-Board Layout Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

D–1 |

Appendix E |

Crystal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

E–1 |

Appendix F |

Changes Made For TVP3026 Revision B . . . . . . . . . . . . . . . . . . . . . . . . . . |

F–1 |

Appendix G |

Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

G–1 |

iv

List of Illustrations

Figure |

Title |

Page |

1–1. |

Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 1–3 |

1–2. |

Terminal Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 1–4 |

2–1. |

TVP3026 Clocking Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–8 |

2–2. |

Loop Clock PLL Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–12 |

2–3. |

Typical Configuration – VRAM Clocked by Accelerator . . . . . . . . . . . . . . . . . . . . . . |

2–16 |

2–4. |

Typical Configuration – VRAM Clocked by TVP3026 . . . . . . . . . . . . . . . . . . . . . . . . |

2–16 |

2–5. |

Frame-Buffer Timing Without Using SCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–17 |

2–6. |

Frame-Buffer Timing Using SCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–18 |

2–7. |

Frame-Buffer Timing Using SCLK (With First SCLK Pulse Relocated) . . . . . . . . . |

2–18 |

2–8. |

Cursor-RAM Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–32 |

2–9. |

Cursor Positioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–33 |

2–10. |

Overscan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–37 |

2–11. |

CRC Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–38 |

2–12. |

Equivalent Circuit of the Current Output (IOG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–40 |

2–13. |

Composite Video Output (With 0 IRE, 8-Bit Output) . . . . . . . . . . . . . . . . . . . . . . . . . |

2–41 |

2–14. |

Composite Video Output (With 7.5 IRE, 8-Bit Output) . . . . . . . . . . . . . . . . . . . . . . . |

2–41 |

3–1. |

MPU Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

3–11 |

3–2. |

Video Input/Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

3–12 |

v

List of Tables

Table |

Title |

Page |

2–1. |

Direct Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 2–1 |

2–2. |

Indirect Register Map (Extended Registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–2 |

2–3. |

Allocation of Palette-Page Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–3 |

2–4. |

Color Register Address Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–4 |

2–5. |

Clock-Selection Register Bits CSR (6 – 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–6 |

2–6. |

Clock-Selection Register Bits CSR (3 – 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–6 |

2–7. |

PLL Top Level Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–7 |

2–8. |

PLL Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–7 |

2–9. |

PLL Data Register Pointer Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–7 |

2–10. |

Pixel Clock PLL Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–9 |

2–11. |

Pixel Clock PLL Frequency Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 2–9 |

2–12. |

MCLK PLL Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–10 |

2–13. |

MCLK/Loop Clock Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–11 |

2–14. |

Loop Clock PLL Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–13 |

2–15. |

Loop Clock PLL Settings for Packed-24 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–14 |

2–16. |

Latch-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–15 |

2–17. |

Multiplex Mode and Bus-Width Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–24 |

2–18. |

Pseudo-Color Mode Pixel-Latching Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–27 |

2–19. |

Packed-24 Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–28 |

2–20. |

Direct-Color Mode Pixel-Latching Sequence (Little-Endian) . . . . . . . . . . . . . . . . . . |

2–29 |

2–21. |

Direct-Color Mode Pixel-Latching Sequence (Big-Endian) . . . . . . . . . . . . . . . . . . . |

2–30 |

2–22. |

Cursor RAM Vs. Color Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–33 |

2–23. |

Port-Select Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–35 |

2–24. |

Sense-Test Register Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–38 |

2–25. |

General Purpose I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–39 |

2–26. |

General-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–42 |

2–27. |

Miscellaneous-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–42 |

2–28. |

Indirect Cursor-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–43 |

2–29. |

Direct Cursor-Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–43 |

2–30. |

Cursor Position (x, y) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–44 |

2–31. |

Color-Key Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–45 |

2–32. |

Color-Key Low and High Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–46 |

2–33. |

CRC Remainder LSB and MSB Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–46 |

2–34. |

CRC Bit Select Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

2–46 |

vi

1 Introduction

The TVP3026 is an advanced video interface palette (VIP) from Texas Instruments implemented in EPIC 0.2-micron CMOS process. The TVP3026 is a 64-bit VIP that supports packed-24 modes enabling 24-bit true color and high resolution at the same time without excessive amounts of frame buffer memory. For example, a 24-bit true color display with 1280 x 1024 resolution may be packed into 4M of VRAM. A PLL-generated, 50 % duty cycle reference clock is output in the packed-24 modes, maximizing VRAM cycle time and the screen refresh rate.

The TVP3026 supports all of the pixel formats of the TVP3020 VIP. Data can be split into 4 or 8 bit planes for pseudo-color mode or split into 12-, 16or 24-bit true-color and direct-color modes. For the 24-bit direct color modes, an 8-bit overlay plane is available. The 16-bit directand true-color modes can be configured to IBM XGA (5, 6, 5), TARGA (1, 5, 5, 5), or 16-bit/pixel (6, 6, 4) configuration as another existing format. An additional 12-bit mode with 4-bit overlay (4, 4, 4, 4) is supported with 4 bits for each color and overlay. All color modes support selection of little or big endian data format for the pixel bus. Additionally, the device is also software compatible with the INMOS IMSG176/8 and Brooktree Bt476/8 color palettes.

Two fully programmable phase-locked loops (PLLs) for pixel clock and memory clock functions are provided, as well as a simple frequency doubler for dramatic improvements in graphics system cost and integration. A third loop clock PLL is incorporated making pixel data latch timing much simpler than with other existing color palettes. In addition, four digital clock inputs (2 TTLand 2 ECL/TTL-compatible) may be utilized and are software selectable. The video clock provides a software selected divide ratio of the chosen pixel clock. The shift clock output may be used directly as the VRAM shift clock. The reference clock output is driven by the loop clock PLL and provides a timing reference to the graphics accelerator.

Like the TVP3020, the TVP3026 also integrates a complete IBM XGA-compatible hardware cursor on chip, making significant graphics performance enhancements possible. Additionally, hardware port select and color-keyed switching functions are provided, giving the user several efficient means of producing graphical overlays on direct-color backgrounds.

The TVP3026 has three 256-by-8 color lookup tables with triple 8-bit video digital-to-analog converters (DACs) capable of directly driving a doubly terminated 75-Ω line. The lookup tables are designed with a dual-ported RAM architecture that enables ultra-high speed operation. Sync generation is incorporated on the green output channel. Horizontal sync (HSYNC) and vertical sync (VSYNC) are pipeline delayed through the device and optionally inverted to indicate screen resolution to the monitor. A palette-page register is available to select from multiple color maps in RAM when 4 bit planes are used. This allows the screen colors to be changed with only one microprocessor write cycle.

The device features a separate VGA bus which supports the integrated VGA modes in graphics accelerator applications, allowing efficient support for VGA graphics and text modes. The separate bus also is useful for accepting data from the feature connector of most VGA-supported personal computers, without the need for external data multiplexing.

The TVP3026 is highly system integrated. It can be connected to the serial port of VRAM devices without external buffer logic and connected to many graphics engines directly. It also supports the split shift-register transfer function, which is common to many industry standard VRAM devices.

The system-integration concept is even carried further to manufacturing test and field diagnosis. To support these, several highly integrated test functions have been designed to enable simplified testing of the palette and the entire graphics system.

EPIC is a trademark of Texas Instruments Incorporated.

XGA is a registered trademark of International Business Machines Corporation

TARGA is a registered trademark of Truevision Incorporated.

Brooktree is a trademark of Brooktree Corporation.

INMOS is a trademark of INMOS International Limited.

1–1

1.1Features

There are many features that the TVP3026 video interface palette possesses; and, the itemized list of them are:

•Supports system resolutions up to 1600 × 1280 @ 76-Hz refresh rate

•Supports color depths of 4, 8, 16, 24 and 32 bit/pixel

•64-bit-wide pixel bus

•Versatile direct-color modes:

–24-bit/pixel with 8-bit overlay (O, R, G, B)

–24-bit/pixel (R, G, B)

–16-bit/pixel (5, 6, 5) XGA configuration

–16-bit/pixel (6, 6, 4) configuration

–15-bit/pixel with 1 bit overlay (1, 5, 5, 5) TARGA configuration

–12-bit/pixel with 4 bit overlay (4, 4, 4, 4)

•True-color gamma correction

•Supports packed pixel formats for 24 bit/pixel using a 32-or 64-bit/pixel bus

•50% duty cycle reference clock for higher screen refresh rates in packed-24 modes

•Programmable frequency synthesis phase-locked loops (PLLs) for dot clock and memory clock

•Loop clock PLL compensates for system delay and ensures reliable data latching

•Versatile pixel bus interface supports littleand big-endian data formats

•135-, 175-, and 220-MHz versions

• On-chip hardware cursor, 64 × 64 × 2 cursor (XGA and X-windows functionally compatible)

•Direct interfacing to video RAM

•Supports overscan for creation of custom screen borders

•Color-keyed switching of direct color and true color or overlay

•Hardware port select switching between direct color and true color or overlay

•Triple 8-Bit D/A converters

•Analog output comparators for monitor detection

•RS-343A compatible outputs

•Direct VGA pass-through capability

•Palette page register

•Horizontal zooming capability

1–2

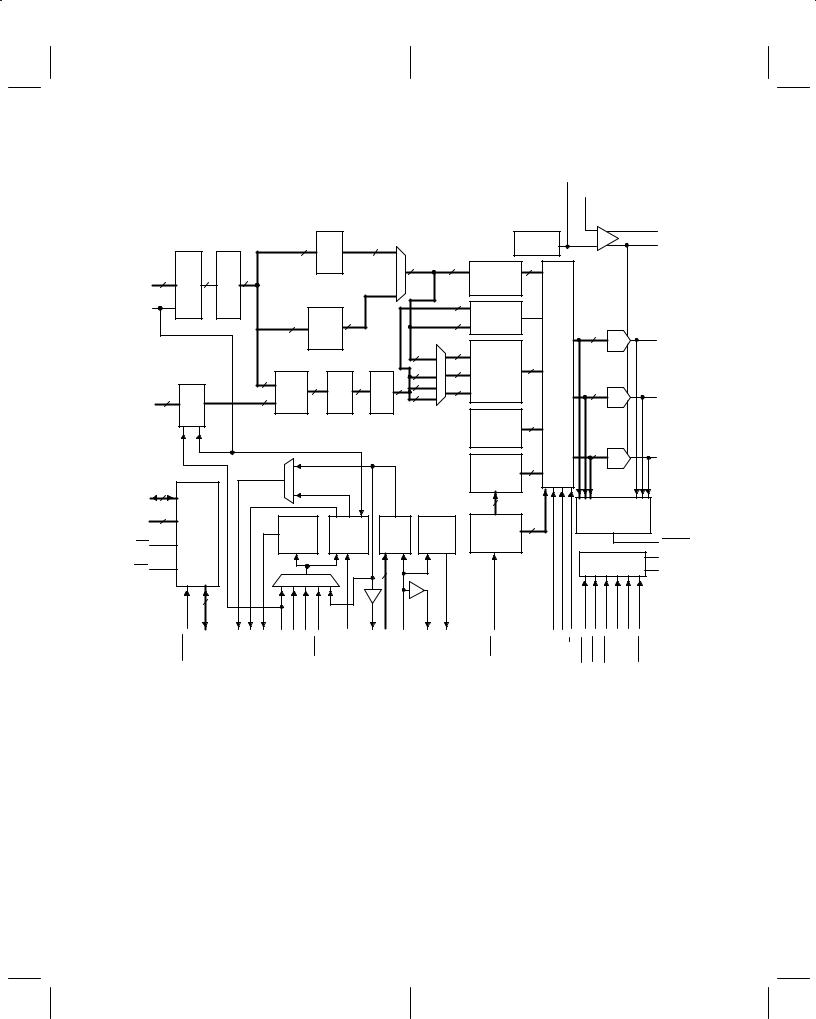

1.2Functional Block Diagram

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FS ADJUST |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vref |

|

|

|

COMP2 |

|

|

|

|

|

|

|

|

True |

|

|

|

24 |

|

|

|

|

|

|

|

|

COMP1 |

|

|

|

|

|

|

|

|

|

Color |

|

|

|

|

|

|

|

1.235 V |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

1:1 |

|

|

|

MUX |

|

|

|

|

|

|

|

|

Direct-Color |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Pixel |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

2:1 |

|

|

|

|

|

|

|

|

|

24 |

|

24 |

|

Pipeline |

24 |

|

|

|

|

|

P(63 – 0) |

Bus |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Pipe |

32 |

|

|

|

|

|

|

|

|

|

|

|

|

Delay |

|

|

|

|

|

||

64 |

Latch |

64 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

LCLK |

|

|

MUX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

Color Key |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

24 |

|

|

|

|

|

Switch |

|

|

|

|

|

|

|

|

|

|

|

|

|

Unpack |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

32 |

Logic |

|

|

|

|

|

|

|

24 |

|

|

|

|

DAC |

IOR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

|

3× 256× 8 |

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

Output |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

Color |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Palette |

MUX |

|

|

|

|

|

|

|

|

|

|

|

Pseudo |

|

|

|

|

|

|

|

8 |

|

8 |

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RAM |

|

|

|

|

||||

|

|

|

|

|

32 |

|

Read |

|

Page |

|

|

|

|

|

|

|||||||

|

|

|

|

|

Color |

|

|

8 |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

VGA |

|

|

|

8 |

Mask |

8 |

Reg |

8 |

|

8 |

|

|

|

|

DAC |

IOG |

|||||

VGA(7 – 0) |

|

|

|

|

MUX |

|

|

|

|

|

|

|||||||||||

|

|

|

8 |

|

|

|

|

|

|

|

|

8 |

|

|||||||||

8 |

Latch |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1× 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Overscan |

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Color |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3× 24 |

|

|

|

DAC |

IOB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cursor |

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Colors |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D(7 – 0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

Test Function |

|

8 |

MPU |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64× 64× 2 |

|

|

|

and |

|

||

RS(3 – 0) |

Registers |

|

|

|

DOT |

|

|

Loop |

|

Pixel |

Memory |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

Sense Comparator |

|||||||||||||

5 |

and |

|

|

|

Clock |

|

|

Clock |

|

Clock |

Clock |

|

Cursor RAM |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

2 |

|

|

|

|

||||||||||

RD |

Control |

|

|

|

Divider |

|

PLL |

|

|

PLL |

|

PLL |

|

and Control |

|

|

|

SENSE |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

Logic |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Video-Signal |

HSYNCOUT |

|

WR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

Control |

VSYNCOUT |

|

|

|

|

|

|

|

Clock Select |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

GI/O(4–0) |

RCLK |

SCLK |

VCLK |

CLK0 CLK1 CLK2 |

|

CLK2 |

SFLAG |

|

PCLKOUT |

PLLSEL(1,0) |

XTAL2 |

XTAL1 |

MCLK |

|

ODD/EVEN |

PSEL OVS |

8/6 |

SYSHS |

SYSVS SYSBL VGAHS VGAVS |

VGABL |

Figure 1–1. Functional Block Diagram

1–3

1.3Terminal Assignments

PLLSEL0

1 DVDD

1 DVDD

2 P33

2 P33

3 P32

3 P32

4 P31

4 P31

5 P30

5 P30

6 P29

6 P29

7 P28

7 P28

8 P27

8 P27

9

9

P26  10

10

P25

11

11

P24  12

12

P23

13

13

P22  14

14

P21

15

15

P20  16

16

GND

17

17

DVDD  18 P19

18 P19  19

19

P18

20

20

P17  21

21

P16

22

22

P15  23

23

P14

24

24

P13  25

25

P12

26

26

P11  27

27

P10

28

28

P9  29

29

P8

30

30

P7  31

31

P6

32

32

P5  33

33

P4

34

34

P3  35

35

P2

36

36

P1  37

37

P0

38 DVDD

38 DVDD

39 DVDD

39 DVDD

40

40

PLLSEL1 |

|

GND |

|

P34 |

|

P35 |

|

P36 |

|

P37 |

|

P38 |

|

P39 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

160 |

|

159 |

158 |

|

157 |

|

156 |

|

155 |

|

154 |

|

153 |

|||||||

41 |

42 |

43 |

44 |

45 |

46 |

47 |

48 |

||

GND |

RS3 |

|

WR |

|

RD |

DD |

GND |

D7 |

D6 |

|

|

||||||||

|

|

|

DV |

|

|

||||

NC – No internal connection

152 P40

D5 49

151 P41

D4 50

P42 |

P43 |

NC |

NC |

150 |

149 |

148 |

147 |

51 |

52 |

53 |

54 |

D3 |

D2 |

D1 |

D0 |

DD |

|

PLLV |

NC |

146 |

145 |

55 |

56 |

RS0 |

RS1 |

PCLKOUT |

|

PLLV |

PLLGND |

||

|

|

|

DD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

144 |

|

143 |

|

142 |

|

57 |

58 |

59 |

RS2 |

GI/O0 |

GI/O1 |

141 P44

GI/O2 60

140 P45

GI/O3 61

139 P46

GI/O4 62

P47 |

DD |

GND |

DV |

||

138 |

137 |

136 |

63 |

64 |

65 |

RESET |

SENSE |

DV |

|

|

DD |

135 P48

GND 66

134 P49

HSYNCOUT 67

133 P50

VSYNCOUT 68

132 P51

GND 69

131 P52

IOR 70

P53 |

P54 |

|

|

|

|

|

|

|

130 |

|

129 |

71 |

72 |

GND |

IOG |

128 P55

GND 73

127 P56

IOB 74

126 SCLK

GND 75

125 VCLK

FS ADJUST 76

124 RCLK

COMP1 77

123 LCLK

REF 78

122 ODD/EVEN

COMP2 79

MCLK |

|

|

|

121 |

XTAL2 |

||

120 |

|||

119 |

XTAL1 |

||

118 |

GND |

||

117 |

DVDD |

||

116 |

P57 |

||

115 |

P58 |

||

114 |

P59 |

||

113 |

P60 |

||

112 |

P61 |

||

111 |

P62 |

||

110 |

P63 |

||

109 |

CLK2 |

|

|

108 |

CLK2 |

||

107 |

CLK1 |

||

106 |

CLK0 |

||

105 |

SFLAG |

||

104 |

VGABL |

||

103 |

VGAVS |

||

102 |

VGAHS |

||

101 |

SYSBL |

|

|

100 |

SYSVS |

|

|

99 |

SYSHS |

||

98 |

8/6 |

|

|

97 |

PSEL |

||

96 |

OVS |

||

95 |

VGA7 |

||

94 |

VGA6 |

||

93 |

VGA5 |

||

92 |

VGA4 |

||

91 |

VGA3 |

||

90 |

VGA2 |

||

89 |

VGA1 |

||

88 |

VGA0 |

||

87 |

AVDD |

||

86 |

AVDD |

||

85 |

GND |

||

84 |

AVDD |

||

83 |

GND |

||

82 |

GND |

||

81 |

GND |

||

80 |

|

|

|

DD |

|

|

|

AV |

|

|

|

Figure 1–2. Terminal Assignments

1–4

1.4Ordering Information

TVP3026 – XXX XXXX

Pixel Clock Frequency Indicator

MUST CONTAIN THREE CHARACTERS:

–135: 135-MHz pixel clock (revision A only)

–175: 175-MHz pixel clock

–220: 220-MHz pixel clock

–250: 250-MHz pixel clock

Device Revision

MUST CONTAIN ONE LETTER:

A

B

Package

MUST CONTAIN THREE LETTERS:

PCE: Plastic, Quad Flat Pack

MDN:Metal, Quad Flat Pack

1.5Terminal Functions

|

TERMINAL |

I/O |

DESCRIPTION |

||||

NAME |

NO. |

||||||

|

|

|

|

||||

|

|

|

|

|

|

|

|

AVDD |

80, 84, |

|

Analog power. All AVDD terminals must be connected. A separate cutout in the |

||||

|

|

86, 87 |

|

DVDD plane should be made for AVDD. The DVDD and AVDD planes should be |

|||

|

|

|

|

connected only at a single point through a ferrite bead close to where power enters |

|||

|

|

|

|

the board. |

|||

|

|

|

|

|

|

|

|

CLK0 |

106 |

I |

Dot clock 0 TTL input. CLK0 can be selected to drive the dot clock at frequencies |

||||

|

|

|

|

up to 140 MHz. When using the VGA port, the maximum frequency is 85 MHz. |

|||

|

|

|

|

CLK0 can be selected as the latch clock for VGA data and video controls. |

|||

|

|

|

|

(power-up default). |

|||

|

|

|

|

|

|

|

|

CLK1 |

107 |

I |

Dot clock 1 TTL input. CLK1 can be selected to drive the dot clock at frequencies |

||||

|

|

|

|

up to 140 MHz. |

|||

|

|

|

|

|

|

||

CLK2, |

|

108, 109 |

I |

Dual-mode dot clock input. These inputs are emitter-coupled logic |

|||

CLK2 |

|||||||

|

|

|

|

(ECL)-compatible inputs. Alternatively, CLK2 and |

CLK2 |

may be used as |

|

|

|

|

|

individual TTL clock inputs. Programming the clock selection register selects the |

|||

|

|

|

|

chosen configuration. These inputs may be selected as the dot clock up to the |

|||

|

|

|

|

device limit while in the ECL mode or up to 140 MHz in the TTL mode. |

|||

|

|

|

|

||||

COMP1, |

77, 79 |

I |

Compensation. COMP1 and COMP2 provide compensation for the internal |

||||

COMP2 |

|

|

reference amplifier. A 0.1- F ceramic capacitor is required between COMP1 and |

||||

|

|

|

|

COMP2. This capacitor must be as close to the device as possible to avoid noise |

|||

|

|

|

|

pick up. |

|||

|

|

|

|

||||

DVDD |

2, 18, 39, |

|

Digital power. All DVDD terminals must be connected to the digital power plane |

||||

|

|

40, 45, 65, |

|

with sufficient decoupling capacitors near the TVP3026. |

|||

|

|

117, 137 |

|

|

|

|

|

|

|

|

|

||||

D7 –D0 |

47 –54 |

I/O |

MPU interface data bus. Data is transferred in and out of the register map, palette |

||||

|

|

|

|

RAM, and cursor RAM on D7 –D0. |

|||

|

|

|

|

|

|

||

NOTE 1: All unused inputs should be tied to a logic level and not allowed to float. |

|||||||

1–5

1.5Terminal Functions (Continued)

|

TERMINAL |

I/O |

DESCRIPTION |

|||||

NAME |

NO. |

|||||||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

FS ADJUST |

76 |

I |

Full-scale adjustment. A resistor connected between FS ADJUST and GND |

|||||

|

|

|

|

|

controls the full-scale range of the DACs. |

|||

|

|

|

|

|

|

|

|

|

GND |

17, 41, 46, |

|

Ground. All GND terminals must be connected. A common ground plane should |

|||||

|

|

|

66, 69, 71, |

|

be used. |

|||

|

|

|

73, 75, |

|

|

|

|

|

|

|

|

81–83, 85, |

|

|

|

|

|

|

|

|

118, 136, |

|

|

|

|

|

|

|

|

159 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HSYNCOUT, |

67, 68 |

O |

Horizontal and vertical sync outputs. These outputs are pipeline delayed |

|||||

VSYNCOUT |

|

|

versions of the selected sync inputs. Output polarity inversion may be |

|||||

|

|

|

|

|

independently selected using general control register bits GCR(1,0). |

|||

|

|

|

|

|

|

|

|

|

IOR, IOG, |

70, 72, 74 |

O |

Analog current outputs. These outputs can drive a 37.5-Ω load directly (doubly |

|||||

IOB |

|

|

terminated 75-Ω line), thus eliminating the requirement for any external buffering. |

|||||

|

|

|

|

|

|

|

|

|

GI/O4 –GI/O0 |

58 –62 |

I/O |

Software programmable general I/O terminals that can be used to control |

|||||

|

|

|

|

|

external devices. |

|||

|

|

|

|

|

|

|

|

|

LCLK |

123 |

I |

Latch clock input. LCLK latches pixel-bus-input data and system video controls. |

|||||

|

|

|

|

|

VGA data may also be latched with LCLK when selected. LCLK may be a delayed |

|||

|

|

|

|

|

version of RCLK provided that linear phase changes in RCLK cause |

|||

|

|

|

|

|

corresponding linear phase changes in LCLK. |

|||

|

|

|

|

|

|

|

|

|

MCLK |

121 |

O |

Memory clock output. MCLK is the output of an independently programmable |

|||||

|

|

|

|

|

PLL frequency synthesizer. The frequency range is 14 – 100 MHz. The dot clock |

|||

|

|

|

|

|

may be output on this terminal while the MCLK frequency is reprogrammed. See |

|||

|

|

|

|

|

subsection 2.4.2.1, Changing the MCLK Frequency. |

|||

|

|

|

|

|

|

|

|

|

PCLKOUT |

144 |

O |

Pixel clock PLL output. PCLKOUT is a buffered version of the pixel clock PLL |

|||||

|

|

|

|

|

output and is mainly for test purposes. This output is independent of the dot clock |

|||

|

|

|

|

|

source selected by the clock selection register. |

|||

|

|

|

|

|

|

|

|

|

PLLGND |

142 |

|

Ground for PLL supplies. Decoupling capacitors should be connected between |

|||||

|

|

|

|

|

PLLVDD and PLLGND. PLLGND should be connected to the system ground |

|||

|

|

|

|

|

through a ferrite bead. |

|||

|

|

|

|

|

|

|

|

|

PLLVDD |

143, 146 |

|

PLL power supply. PLLVDD must be a well regulated 5-V power supply voltage. |

|||||

|

|

|

|

|

Decoupling capacitors should be connected between PLLVDD and PLLGND. |

|||

|

|

|

|

|

Terminal 143 supplies power to the pixel clock PLL. Terminal 146 supplies power |

|||

|

|

|

|

|

to the MCLK PLL and the loop clock PLL. |

|||

|

|

|

|

|

|

|

|

|

OVS |

96 |

I |

Overscan input. OVS controls the display of custom screen borders. When OVS |

|||||

|

|

|

|

|

is not used, it should be connected to GND. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

122 |

I |

|

|

|

|

ODD/EVEN |

|

Odd or even field display. ODD/EVEN indicates odd or even field during |

||||||

|

|

|

|

|

interlaced display for cursor operation. A low signal indicates the even field and |

|||

|

|

|

|

|

a high signal indicates the odd field. See subsection 2.7.4, Interlaced Cursor |

|||

|

|

|

|

|

Operation, for cursor operation in interlace mode. |

|||

|

|

|

|

|||||

PLLSEL0, |

1, 160 |

I |

Pixel clock PLL frequency selection. PLLSELx selects among two fixed |

|||||

PLLSEL1 |

|

|

frequencies and the programmed frequency of the pixel clock PLL. |

|||||

|

|

|

|

|

|

|

|

|

NOTE 1: All unused inputs should be tied to a logic level and not allowed to float.

1–6

1.5Terminal Functions (Continued)

|

|

|

|

TERMINAL |

I/O |

DESCRIPTION |

|||||

|

|

NAME |

NO. |

||||||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

PSEL |

97 |

I |

Port select. PSEL provides the capability of switching between direct color and |

|||||||

|

|

|

|

|

|

|

true color or overlay. Multiple true color or overlay windows may be displayed |

||||

|

|

|

|

|

|

|

using the PSEL control. Since PSEL is sampled with LCLK, the granularity for |

||||

|

|

|

|

|

|

|

switching depends on the number of pixels loaded per LCLK. When PSEL is not |

||||

|

|

|

|

|

|

|

used, it should be connected to GND. |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

P63 –P0 |

3 –16, |

I |

Pixel input port. The port can be used in various modes as described in |

|||||||

|

|

|

|

|

19 –38, |

|

Section 2.6, Multplexing Modes of Operation. Unused terminals should not be |

||||

|

|

|

|

|

110 –116, |

|

allowed to float. |

||||

|

|

|

|

|

127 –135, |

|

|

|

|

|

|

|

|

|

|

|

138 –141, |

|

|

|

|

|

|

|

|

|

|

|

149 –158 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RCLK |

124 |

O |

Reference clock output. RCLK can be programmed to output either the pixel clock |

|||||||

|

|

|

|

|

|

|

PLL (power up default) or the loop clock PLL. The pixel clock PLL is selected to |

||||

|

|

|

|

|

|

|

provide a reference clock to the VGA controller. In this configuration, the VGA |

||||

|

|

|

|

|

|

|

controller returns VGA data and video controls along with a synchronous clock |

||||

|

|

|

|

|

|

|

which becomes the TVP3026 dot clock source using CLK0. For all other modes, |

||||

|

|

|

|

|

|

|

the loop clock PLL is selected to provide the reference clock. In this configuration, |

||||

|

|

|

|

|

|

|

the pixel clock PLL (or external clock) becomes the TVP3026 dot clock source. |

||||

|

|

|

|

|

|

|

The reference clock is used to generate VRAM shift clocks (or clocks a VGA |

||||

|

|

|

|

|

|

|

controller) and generate video controls. The pixel port (or VGA port) and video |

||||

|

|

|

|

|

|

|

controls are latched by LCLK. The loop clock PLL controls the phase of RCLK to |

||||

|

|

|

|

|

|

|

phase-lock the received LCLK with the internal dot clock. |

||||

|

|

|

|

|

|

|

For systems that use SCLK as the VRAM shift clock, RCLK should be connected |

||||

|

|

|

|

|

|

|

to LCLK. An external buffer may be used between RCLK and LCLK when SCLK |

||||

|

|

|

|

|

|

|

is also buffered, within the timing constraints of the TVP3026. RCLK is not gated |

||||

|

|

|

|

|

|

|

off during blanking. |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

REF |

78 |

I/O |

Voltage reference for DACs. An internal voltage reference of nominally 1.235 V |

|||||||

|

|

|

|

|

|

|

is provided that requires an external 0.1- F ceramic capacitor between REF and |

||||

|

|

|

|

|

|

|

analog GND. However, the internal reference voltage can be overdriven by an |

||||

|

|

|

|

|

|

|

externally-supplied reference voltage. |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

63 |

I |

Master reset. All the registers assume their default state after reset. The default |

||||

|

RESET |

|

|

||||||||

|

|

|

|

|

|

|

state is VGA mode 2 (CLK0 latching of VGA data and video controls). |

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

44 |

I |

Read strobe input. A low signal on |

|

initiates a read from the register map. Read |

||

|

RD |

|

|

RD |

|||||||

|

|

|

|

|

|

|

transfer data is enabled onto the D(7 –0) bus when RD is low (see |

||||

|

|

|

|

|

|

|

Figure 3–1). |

||||

|

|

|

|

|

|

|

|

||||

|

RS3 –RS0 |

42, 55 –57 |

I |

Register select inputs. These terminals specify the location in the direct register |

|||||||

|

|

|

|

|

|

|

map that is to be accessed as shown in Table 2–1. |

||||

|

|

|

|

|

|

|

|

||||

|

SCLK |

126 |

O |

Shift clock output. SCLK is a gated version of the loop clock PLL output and is |

|||||||

|

|

|

|

|

|

|

gated off during blanking. SCLK may drive the VRAM shift clock directly. This is |

||||

|

|

|

|

|

|

|

intended for designs in which the graphics controller does not supply the VRAM |

||||

|

|

|

|

|

|

|

shift clock. |

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

64 |

O |

Test mode DAC comparator output signal. |

|

is low when one or more of the |

||

|

SENSE |

|

SENSE |

||||||||

|

|

|

|

|

|

|

DAC output analog levels is above the internal comparator reference of |

||||

|

|

|

|

|

|

|

350 mV ± 50 mV. |

||||

NOTE 1: All unused inputs should be tied to a logic level and not allowed to float.

1–7

1.5Terminal Functions (Continued)

|

|

|

|

|

|

|

TERMINAL |

I/O |

|

|

|

|

DESCRIPTION |

|||

|

|

|

NAME |

NO. |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SFLAG |

105 |

I |

Split shift register transfer flag. A high pulse on SFLAG during blanking is passed |

||||||||||||

|

|

|

|

|

|

|

|

|

|

directly to the SCLK terminal. This operation is available to meet the special serial |

||||||

|

|

|

|

|

|

|

|

|

|

clocking requirements of some VRAM devices. When SFLAG is not used, |

||||||

|

|

|

|

|

|

|

|

|

|

SFLAG should be connected to GND. |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

101 |

I |

System blank input. |

|

|

is active low. This should be selected for all modes |

|||

|

SYSBL |

|

|

|

SYSBL |

|||||||||||

|

|

|

|

|

|

|

|

|

|

other than VGA mode 2. This signal is pipeline delayed before being passed to |

||||||

|

|

|

|

|

|

|

|

|

|

the DACs. |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

99, 100 |

I |

System horizontal and vertical sync inputs. These signals should be selected for |

||||||||

|

SYSHS |

, |

||||||||||||||

|

SYSVS |

|

|

all modes other than VGA mode 2. These signals are pipeline delayed and each |

||||||||||||

|

|

|

|

|

|

|

|

|

|

may be inverted before being passed to the HSYNCOUT and VSYNCOUT |

||||||

|

|

|

|

|

|

|

|

|

|

terminals. General control register bits GCR(1,0) control the polarity inversion. |

||||||

|

|

|

|

|

|

|

|

|

|

When used to generate the sync level on the green current output, SYSHS and |

||||||

|

|

|

|

|

|

|

|

|

|

SYSVS must be active low at the input to the TVP3026. |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

VCLK |

125 |

O |

Programmable auxiliary clock output. VCLK is derived from the internal dot clock |

||||||||||||

|

|

|

|

|

|

|

|

|

|

using a programmable divide ratio and does not utilize the loop clock PLL for |

||||||

|

|

|

|

|

|

|

|

|

|

synchronization. Since pixel data and video controls are always referenced to |

||||||

|

|

|

|

|

|

|

|

|

|

RCLK and LCLK (or CLK0), use of VCLK for the frame buffer interface or video |

||||||

|

|

|

|

|

|

|

|

|

|

timing is not recommended. |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

104 |

I |

VGA blank input. |

|

is active low. This should be selected when in VGA |

|||||||

|

VGABL |

|

VGABL |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

mode 2 (CLK0 latching of VGA data and video controls). VGABL is pipeline |

||||||

|

|

|

|

|

|

|

|

|

|

delayed before being passed to the DACs. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

VGAHS, |

102, 103 |

I |

VGA horizontal and vertical sync inputs. These signals should be used when in |

||||||||||||

|

VGAVS |

|

|

VGA mode 2 (CLK0 latching of VGA data and video controls). These signals are |

||||||||||||

|

|

|

|

|

|

|

|

|

|

pipeline delayed and each may be inverted before being passed to the |

||||||

|

|

|

|

|

|

|

|

|

|

HSYNCOUT and VSYNCOUT terminals. General control register bits GCR(1,0) |

||||||

|

|

|

|

|

|

|

|

|

|

control the polarity inversion. When used to generate the sync level on the green |

||||||

|

|

|

|

|

|

|

|

|

|

current output, VGAHS and VGAVS must be active low at the input to the |

||||||

|

|

|

|

|

|

|

|

|

|

TVP3026. |

||||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

VGA7 –VGA0 |

88 –95 |

I |

VGA port. This bus can be selected as the pixel input bus for VGA modes, but |

||||||||||||

|

|

|

|

|

|

|

|

|

|

it does not allow for any multiplexing. |

||||||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

43 |

I |

Write strobe input. A low signal on |

|

initiates a write to the register map. Write |

||||

|

WR |

|

WR |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

transfer data is latched from the D(7 –0) bus with the rising edge of WR. |

||||||

|

|

|

|

|

|

|

||||||||||

|

XTAL1, |

119, 120 |

I/O |

Connections for quartz crystal resonator. XTALx is a reference for the frequency |

||||||||||||

|

XTAL2 |

|

|

synthesis PLLs. XTAL2 may be used as a TTL reference clock input, in which |

||||||||||||

|

|

|

|

|

|

|

|

|

|

case XTAL1 is left unconnected. |

||||||

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

98 |

I |

DAC resolution selection. This terminal is used to select the data bus width (8 or |

||||||

8/6 |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

6 bits) for the DACs and is provided for VGA downward compatibility. When the |

||||||

|

|

|

|

|

|

|

|

|

|

8/6 signal is high, 8-bit bus transfers are used with D7 the MSB and D0 the LSB. |

||||||

|

|

|

|

|

|

|

|

|

|

For 6-bit bus operation, while the color palette RAM still has the 8-bit information, |

||||||

|

|

|

|

|

|

|

|

|

|

the data is shifted to the upper six bits and the two LSBs are filled with zeros at |

||||||

|

|

|

|

|

|

|

|

|

|

the output multiplexer to the DACs. The palette RAM data register zeroes the two |

||||||

|

|

|

|

|

|

|

|

|

|

MSBs when the palette RAM is read in the 6-bit mode. The function of this |

||||||

|

|

|

|

|

|

|

|

|

|

terminal may be overridden in software. When not used, the 8/6 terminal should |

||||||

|

|

|

|

|

|

|

|

|

|

be connected to GND so that 6-bit VGA operation begins at power up. |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE 1: All unused inputs should be tied to a logic level and not allowed to float.

1–8

2 Detailed Description

2.1Microprocessor Unit Interface

The standard microprocessor unit (MPU) interface is supported, giving the MPU direct access to the registers and memories of the TVP3026. The processor interface is controlled using read and write strobes (RD, WR), four register select terminals (RS3 –RS0), the D7 –D0 data terminals, and the 8/6-select terminal. The 8/6 terminal is used to select between an 8- or 6-bit-wide data path to the color palette RAM and is provided to maintain compatibility with the IMSG176. See subsection 2.1.1, 8/6 Operation.

Table 2–1 lists the direct register map. These registers are addressed directly by the register select lines RS0 –RS3. Table 2–2 lists the indirect register map. The index for the indirect register map is loaded into the index register (direct register: 0000). This register also stores the palette RAM write address and cursor RAM write address. The indexed data register (direct register: 1010) is then used to read or write the register pointed to in the indirect register map. The index does not post-increment following accesses to the indirect map.

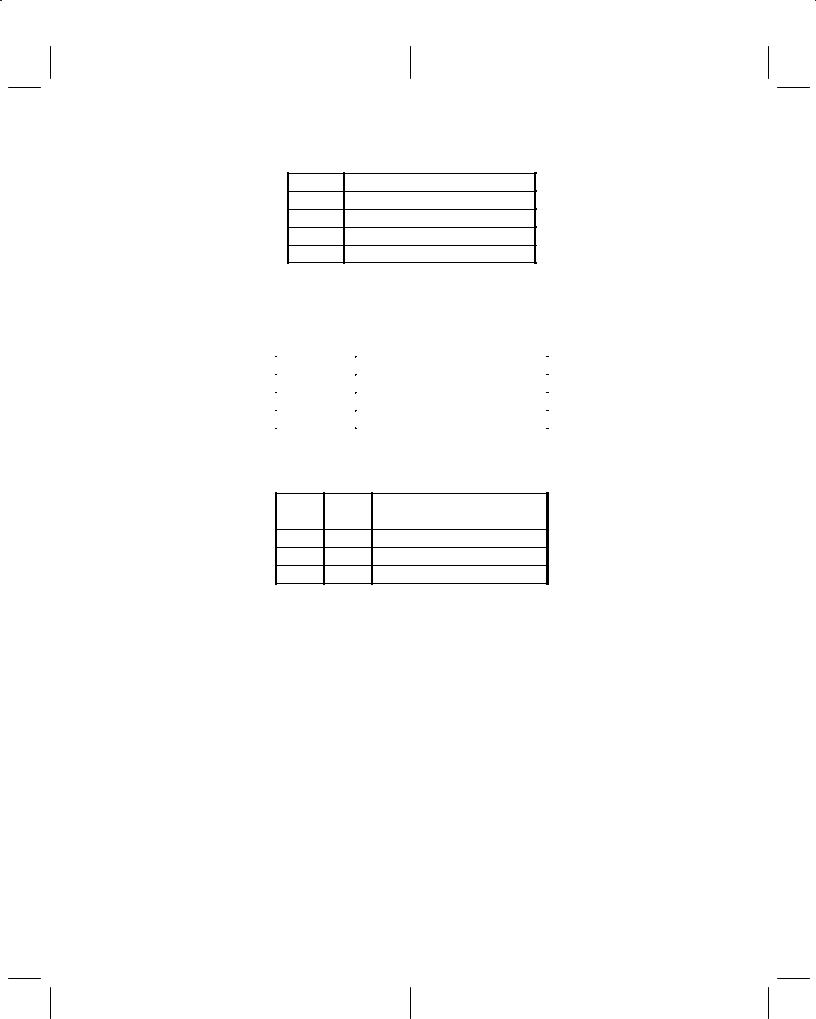

Table 2–1. Direct Register Map

RS3 |

RS2 |

RS1 |

RS0 |

REGISTER ADDRESSED BY MPU |

R / W |

DEFAULT (HEX) |

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

Palette/ Cursor RAM Write Address/ |

R / W |

XX |

|

Index Register |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

Palette RAM Data |

R / W |

XX |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

Pixel Read-Mask |

R / W |

FF |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

Palette/ Cursor RAM Read Address |

R / W |

XX |

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

Cursor / Overscan Color Write Address |

R / W |

XX |

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

Cursor / Overscan Color Data |

R / W |

XX |

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

Reserved |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

Cursor / Overscan Color Read Address |

R / W |

XX |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

Reserved |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

Direct Cursor Control |

R / W |

00 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

Indexed Data |

R / W |

XX |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

Cursor RAM Data |

R / W |

XX |

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

Cursor-Position X LSB |

R / W |

XX |

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

Cursor-Position X MSB |

R / W |

XX |

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

Cursor-Position Y LSB |

R / W |

XX |

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

Cursor-Position Y MSB |

R / W |

XX |

|

|

|

|

|

|

|

|

2–1

Table 2–2. Indirect Register Map (Extended Registers)

INDEX |

R / W |

DEFAULT |

REGISTER ADDRESSED |

|

BY INDEX REGISTER |

||||

|

|

|

||

|

|

|

|

|

0x00 |

|

|

Reserved |

|

|

|

|

|

|

0x01 |

R |

0x00† |

Silicon Revision |

|

0x02 –0x05 |

|

|

Reserved |

|

|

|

|

|

|

0x06 |

R / W |

0x00 |

Indirect Cursor Control |

|

|

|

|

|

|

0x07 –0x0E |

|

|

Reserved |

|

|

|

|

|

|

0x0F |

R / W |

0x06 |

Latch Control |

|

|

|

|

|

|

0x10 –0x17 |

|

|

Reserved |

|

|

|

|

|

|

0x18 |

R / W |

0x80 |

True Color Control |

|

|

|

|

|

|

0x19 |

R / W |

0x98 |

Multiplex Control |

|

|

|

|

|

|

0x1A |

R / W |

0x07 |

Clock Selection |

|

|

|

|

|

|

0x1B |

|

|

Reserved |

|

|

|

|

|

|

0x1C |

R / W |

0x00 |

Palette Page |

|

|

|

|

|

|

0x1D |

R / W |

0x00 |

General Control |

|

|

|

|

|

|

0x1E |

R / W |

0x00 |

Miscellaneous Control |

|

|

|

|

|

|

0x1F –0x29 |

|

|

Reserved |

|

|

|

|

|

|

0x2A |

R / W |

0x00 |

General-Purpose I/O Control |

|