Motorola MCM72F7ADG10, MCM72F7ADG12, MCM72F7ADG9, MCM72F6ADG10, MCM72F6ADG12 Datasheet

...

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MCM72F6A/D

512KB and 1MB Synchronous

Fast Static RAM Module

The MCM72F6A (512KB) is configured as 64K x 72 bits and the MCM72F7A (1MB) is configured as 128K x 72 bits. Both are packaged in a 168±pin dual± in±line memory module DIMM. Each module uses Motorola's 3.3 V 64K x 18 bit flow±through BurstRAMs.

Address (A), data inputs (DQ, DP), and all control signals except output enable

(G) are clock (K) controlled through positive±edge±triggered noninverting registers.

Write cycles are internally self±timed and initiated by the rising edge of the clock (K) input. This feature provides increased timing flexibility for incoming signals. Synchronous byte write (W) allows writes to either individual bytes or to both bytes.

•Single 3.3 V + 10%, ± 5% Power Supply

•Plug and Pin Compatibility with 2MB and 4MB

•Multiple Clock Pins for Reduced Loading

•All Inputs and Outputs are LVTTL Compatible

•Byte Write Capability

•Fast SRAM Access Times: 9/10/12 ns

•Decoupling Capacitors for Each Fast Static RAM

•High Quality Multi±Layer FR4 PWB With Separate Power and Ground Planes

•Amp Connector, Part Number: 390064±4

•5 V Tolerant on All Pins (Inputs and I/Os)

•168±Pin DIMM Module

MCM72F6A

MCM72F7A

168±LEAD DIMM CASE 1115J±01 TOP VIEW

1

11

40

41

84

1/29/98

MOTOROLA FAST SRAM |

MCM72F6A MCM72F7A |

Motorola, Inc. 1998 |

• |

|

1 |

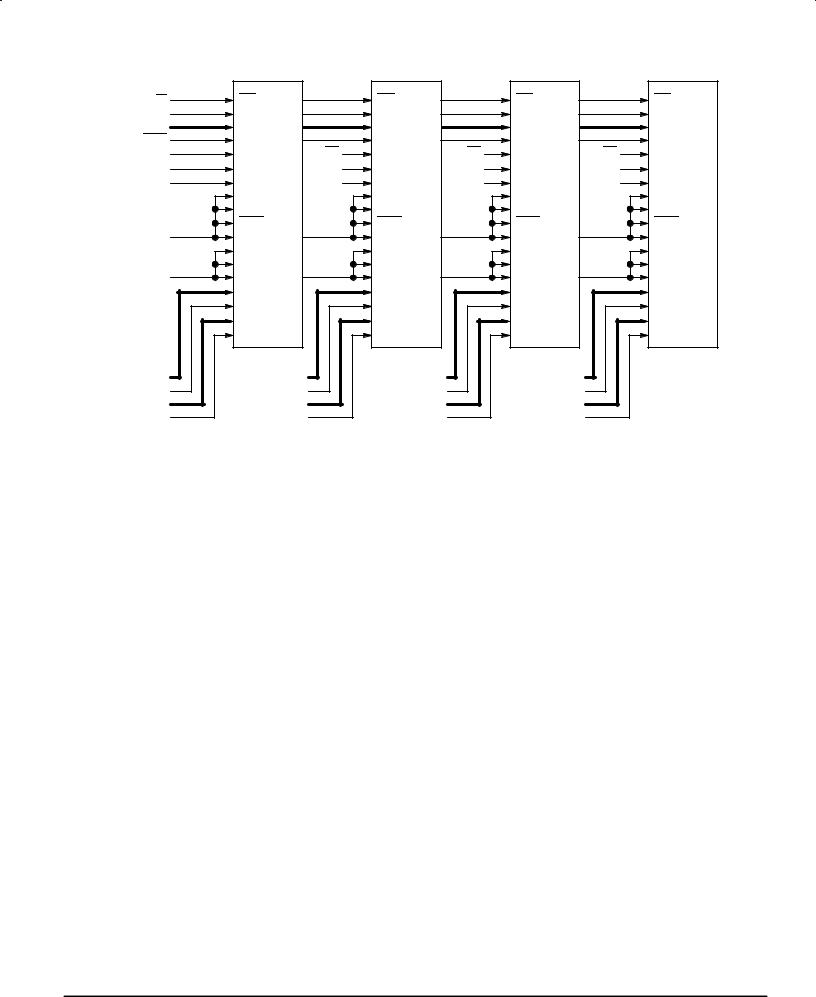

MCM72F6A BLOCK DIAGRAM

|

64K x 18 |

|

64K x 18 |

|

64K x 18 |

|

64K x 18 |

E0 |

SE1 |

|

SE1 |

|

SE1 |

|

SE1 |

G0 |

G |

|

G |

|

G |

|

G |

A0 ± A15 |

A0 ± A15 |

|

A0 ± A15 |

|

A0 ± A15 |

|

A0 ± A15 |

ADSP |

ADSC |

|

ADSC |

|

ADSC |

|

ADSC |

W0 |

SBa |

W2 |

SBa |

W4 |

SBa |

W6 |

SBa |

W1 |

SBb |

W3 |

SBb |

W5 |

SBb |

W7 |

SBb |

K0 |

K |

K1 |

K |

K2 |

K |

K3 |

K |

|

SE2 |

|

SE2 |

|

SE2 |

|

SE2 |

|

ADV |

|

ADV |

|

ADV |

|

ADV |

VDD |

ADSP |

|

ADSP |

|

ADSP |

|

ADSP |

SGW |

|

SGW |

|

SGW |

|

SGW |

|

|

SW |

|

SW |

|

SW |

|

SW |

VSS |

LBO |

|

LBO |

|

LBO |

|

LBO |

SE3 |

|

SE3 |

|

SE3 |

|

SE3 |

|

|

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

|

DQa8 |

|

DQa8 |

|

DQa8 |

|

DQa8 |

|

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

|

DQb8 |

|

DQb8 |

|

DQb8 |

|

DQb8 |

DQ0 ± DQ7 |

DQ16 ± DQ23 |

|

DQ32 ± DQ39 |

|

DQ48 ± DQ55 |

|

|

DP0 |

DP2 |

|

DP4 |

|

DP6 |

|

|

DQ8 ± DQ15 |

DQ24 ± DQ31 |

|

DQ40 ± DQ47 |

|

DQ56 ± DQ63 |

|

|

DP1 |

DP3 |

|

DP5 |

|

DP7 |

|

|

MCM72F6A•MCM72F7A |

MOTOROLA FAST SRAM |

2 |

|

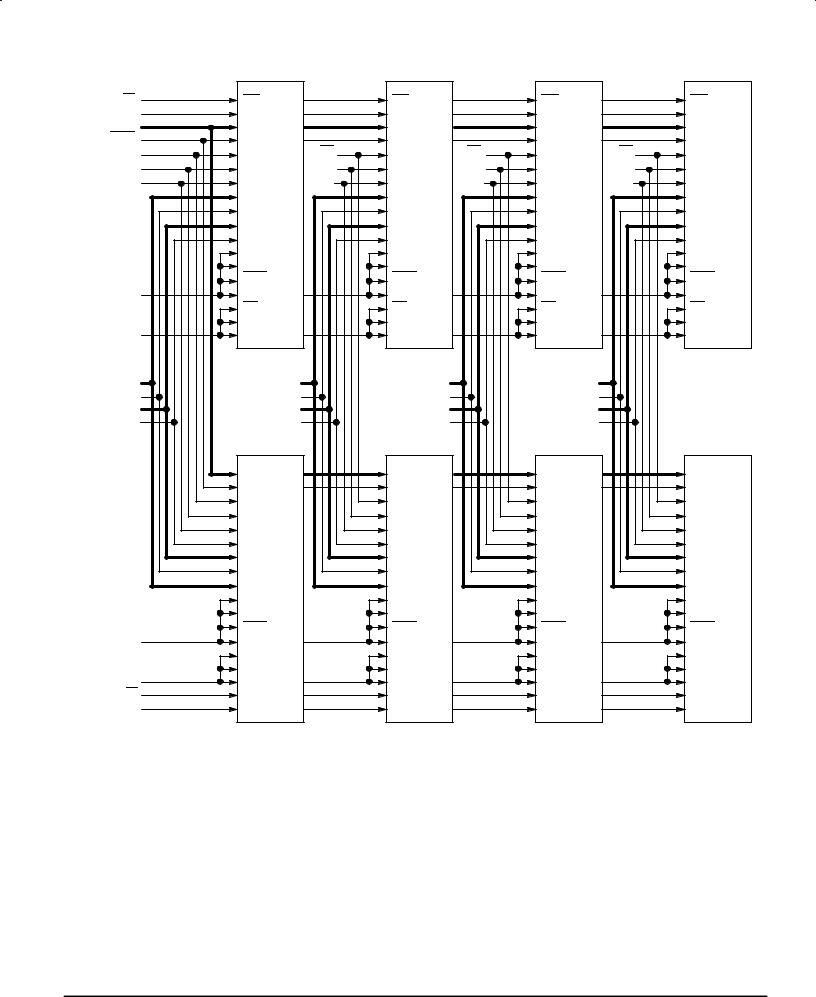

MCM72F7A BLOCK DIAGRAM

E0

G0

A0 ± A15

ADSP

W0

W1

K0

VDD

VSS

DQ0 ± DQ7 DP0

DQ8 ± DQ15

DP1

VDD

VSS

E1

G1

64K x 18 |

|

64K x 18 |

|

64K x 18 |

|

64K x 18 |

SE1 |

|

SE1 |

|

SE1 |

|

SE1 |

G |

|

G |

|

G |

|

G |

A0 ± A15 |

|

A0 ± A15 |

|

A0 ± A15 |

|

A0 ± A15 |

ADSC |

W2 |

ADSC |

W4 |

ADSC |

W6 |

ADSC |

SBa |

SBa |

SBa |

SBa |

|||

SBb |

W3 |

SBb |

W5 |

SBb |

W7 |

SBb |

K |

K1 |

K |

K2 |

K |

K3 |

K |

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

DQa8 |

|

DQa8 |

|

DQa8 |

|

DQa8 |

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

DQb8 |

|

DQb8 |

|

DQb8 |

|

DQb8 |

SE2 |

|

SE2 |

|

SE2 |

|

SE2 |

ADV |

|

ADV |

|

ADV |

|

ADV |

ADSP |

|

ADSP |

|

ADSP |

|

ADSP |

SGW |

|

SGW |

|

SGW |

|

SGW |

SW |

|

SW |

|

SW |

|

SW |

LBO |

|

LBO |

|

LBO |

|

LBO |

SE3 |

|

SE3 |

|

SE3 |

|

SE3 |

DQ16 ± DQ23 |

|

DQ32 ± DQ39 |

|

DQ48 ± DQ55 |

|

|

DP2 |

|

DP4 |

|

DP6 |

|

|

DQ24 ± DQ31 |

|

DQ40 ± DQ47 |

|

DQ56 ± DQ63 |

|

|

DP3 |

|

DP5 |

|

DP7 |

|

|

64K x 18 |

|

64K x 18 |

|

64K x 18 |

|

64K x 18 |

A0 ± A15 |

|

A0 ± A15 |

|

A0 ± A15 |

|

A0 ± A15 |

ADSC |

|

ADSC |

|

ADSC |

|

ADSC |

SBa |

|

SBa |

|

SBa |

|

SBa |

SBb |

|

SBb |

|

SBb |

|

SBb |

K |

|

K |

|

K |

|

K |

DQb8 |

|

DQb8 |

|

DQb8 |

|

DQb8 |

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

|

DQb0 ± DQb7 |

DQa8 |

|

DQa8 |

|

DQa8 |

|

DQa8 |

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

|

DQa0 ± DQa7 |

SE2 |

|

SE2 |

|

SE2 |

|

SE2 |

ADV |

|

ADV |

|

ADV |

|

ADV |

ADSP |

|

ADSP |

|

ADSP |

|

ADSP |

SGW |

|

SGW |

|

SGW |

|

SGW |

SW |

|

SW |

|

SW |

|

SW |

LBO |

|

LBO |

|

LBO |

|

LBO |

SE3 |

|

SE3 |

|

SE3 |

|

SE3 |

SE1 |

|

SE1 |

|

SE1 |

|

SE1 |

G |

|

G |

|

G |

|

G |

MOTOROLA FAST SRAM |

MCM72F6A•MCM72F7A |

|

3 |

Loading...

Loading...