Motorola MCM63P733ATQ90R, MCM63P733ATQ133R, MCM63P733ATQ177, MCM63P733ATQ177R, MCM63P733ATQ90 Datasheet

...

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MCM63P733A/D

Advance Information

128K x 32 Bit Pipelined

BurstRAM Synchronous

Fast Static RAM

The MCM63P733A is a 4M±bit synchronous fast static RAM designed to provide a burstable, high performance, secondary cache for the PowerPC and other high performance microprocessors. It is organized as 128K words of 32 bits each, fabricated with high performance silicon gate CMOS technology. This device integrates input registers, an output register, a 2±bit address counter, and high speed SRAM onto a single monolithic circuit for reduced parts count in cache data RAM applications. Synchronous design allows precise cycle control with the use of an external clock (K). CMOS circuitry reduces the overall power consumption of the integrated functions for greater reliability.

Addresses (SA), data inputs (DQx), and all control signals except output enable (G) and Linear Burst Order (LBO) are clock (K) controlled through positive±edge±triggered noninverting registers.

Bursts can be initiated with either ADSP or ADSC input pins. Subsequent burst addresses can be generated internally by the MCM63P733A (burst sequence operates in linear or interleaved mode dependent upon state of LBO) and controlled by the burst address advance (ADV) input pin.

Write cycles are internally self±timed and are initiated by the rising edge of the clock (K) input. This feature eliminates complex off±chip write pulse generation and provides increased timing flexibility for incoming signals.

Synchronous byte write (SBx), synchronous global write (SGW), and synchronous write enable (SW) are provided to allow writes to either individual bytes or to all bytes. The four bytes are designated as ªaº, ªbº, ªcº, and ªdº.controlsSBa DQa, SBb controls DQb, etc. Individual bytes are written if the selected byte writes SBx are asserted with SW. All bytes are written if either SGW is asserted or if all SBx and SW are asserted.

For read cycles, pipelined SRAMs output data is temporarily stored by an edge±triggered output register and then released to the output buffers at the next rising edge of clock (K).

The MCM63P733A operates from a 3.3 V core power supply and all outputs operate on a 2.5 V or 3.3 V power supply. All inputs and outputs are JEDEC standard JESD8±5 compatible.

•MCM63P733A±133 = 4 ns Access/7.5 ns Cycle (133 MHz) MCM63P733A±117 = 4.2 ns Access/8.5 ns Cycle (117 MHz) MCM63P733A±100 = 4.5 ns Access/10 ns Cycle (100 MHz) MCM63P733A±90 = 5 ns Access/11 ns Cycle (90 MHz)

•3.3 V + 10%/± 5% Core, Power Supply, 2.5 V or 3.3 V I/O Supply

•ADSP, ADSC, and ADV Burst Control Pins

•Selectable Burst Sequencing Order (Linear/Interleaved)

•Internally Self±Timed Write Cycle

•Byte Write and Global Write Control

•Single±Cycle Deselect

•Sleep Mode (ZZ)

•100±Pin TQFP Package

MCM63P733A

TQ PACKAGE

TQFP

CASE 983A±01

PowerPC is a trademark of IBM Corp.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

REV 1 3/24/98

MOTOROLA FAST SRAM |

MCM63P733A |

Motorola, Inc. 1998 |

|

|

1 |

|

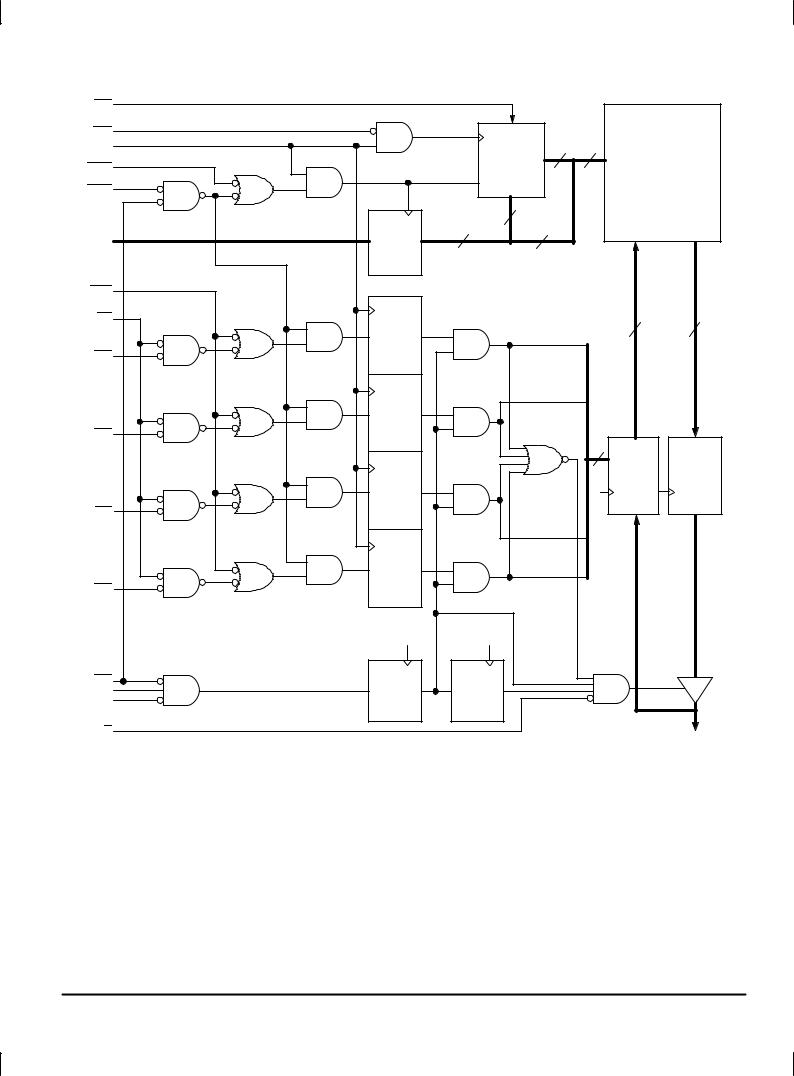

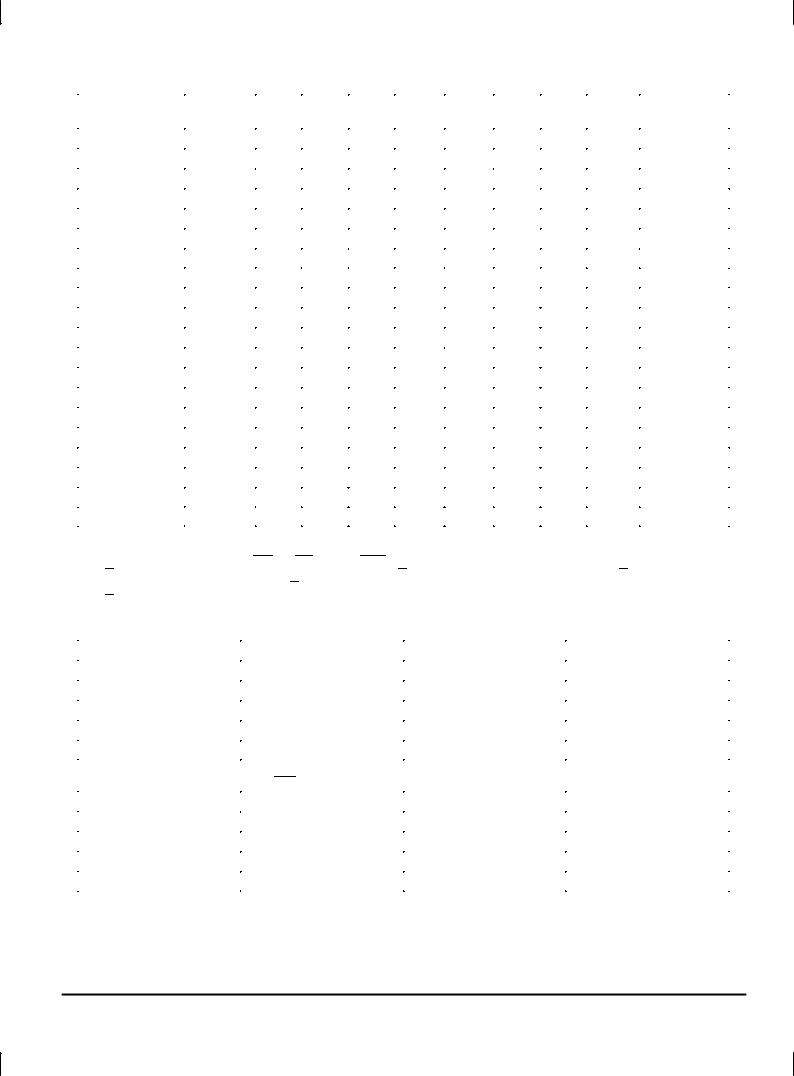

FUNCTIONAL BLOCK DIAGRAM |

|

|

|

LBO |

|

|

|

|

ADV |

|

|

|

|

K |

|

BURST |

2 |

17 |

|

|

|||

ADSC |

K2 |

COUNTER |

|

|

|

CLR |

|

|

|

ADSP |

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

SA |

ADDRESS |

17 |

15 |

|

SA1 |

|

|||

REGISTER |

|

|

|

|

SA0 |

|

|

|

|

|

|

|

|

|

SGW |

|

|

|

|

SW |

WRITE |

|

|

|

|

|

|

|

|

|

REGISTER |

|

|

|

SBa |

a |

|

|

|

|

|

|

|

|

|

WRITE |

|

|

|

|

REGISTER |

|

|

|

SBb |

b |

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

WRITE |

|

|

|

|

REGISTER |

|

|

K |

|

c |

|

|

|

SBc |

|

|

|

|

|

|

|

|

|

|

WRITE |

|

|

|

|

REGISTER |

|

|

|

SBd |

d |

|

|

|

|

|

|

|

|

|

K2 |

K |

|

|

SE1 |

ENABLE |

ENABLE |

|

|

SE2 |

|

|

||

REGISTER |

REGISTER |

|

|

|

SE3 |

|

|

||

|

|

|

|

|

128K x 32 ARRAY

32 32

DATA±IN DATA±OUT REGISTER REGISTER

G

DQa ± DQd

MCM63P733A |

MOTOROLA FAST SRAM |

2 |

|

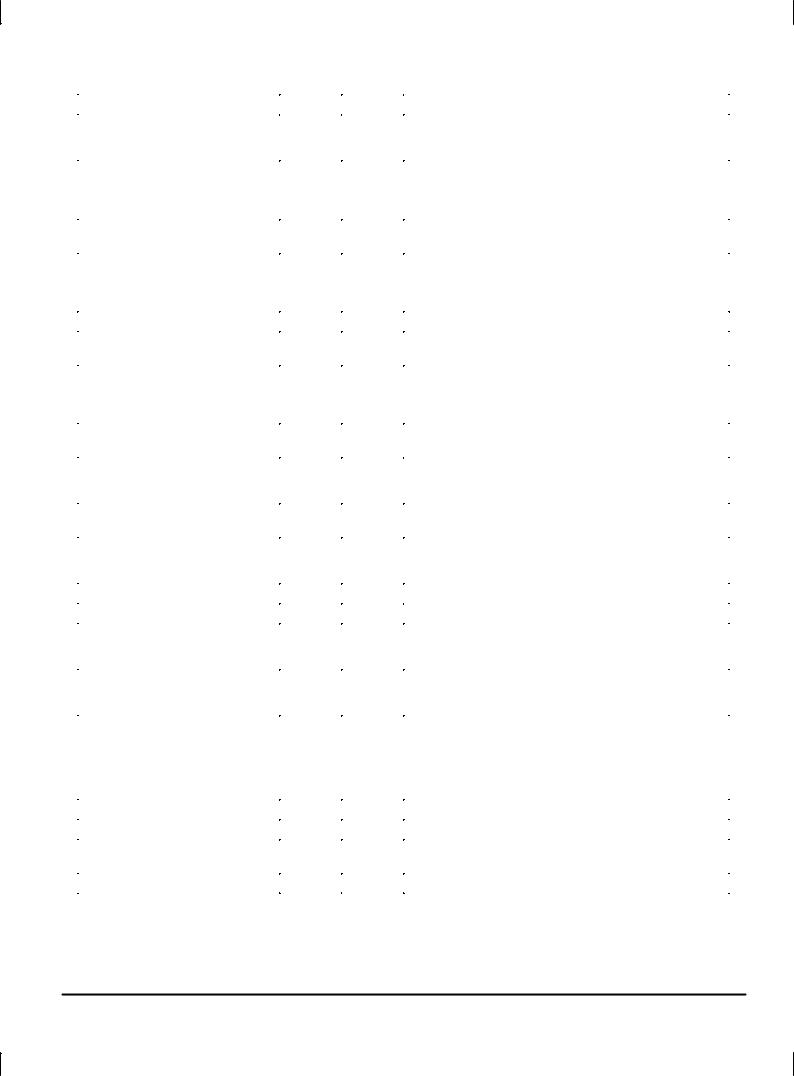

PIN ASSIGNMENT

SA SA SE1 SE2 SBd |

SBc SBb SBa SE3 |

V |

V K |

SGW SW |

G |

ADSC |

ADSP |

ADV SA SA |

||||||

|

|

|

|

|

|

|

DD |

SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

|

100 99 9897 9695 94 93 92 91 90 89 88 87 86 85 84 83 82 81 |

|

|

||||||||||||||||||||||||||||||||||

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

80 |

|

NC |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

DQc |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

79 |

|

DQb |

||||||||||||

DQc |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

78 |

|

DQb |

||||||||||||

VDDQ |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

77 |

|

VDDQ |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

VSS |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

76 |

|

VSS |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

DQc |

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

75 |

|

DQb |

|||||||||||

DQc |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74 |

|

DQb |

||||||||||||

DQc |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

73 |

|

DQb |

||||||||||||

DQc |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

72 |

|

DQb |

||||||||||||

VSS |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

71 |

|

VSS |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

VDDQ |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

70 |

|

VDDQ |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

DQc |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

69 |

|

DQb |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

DQc |

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

68 |

|

DQb |

||||||||||||

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

NC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

67 |

|

VSS |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

VDD |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

66 |

|

NC |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

NC |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

65 |

|

VDD |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

VSS |

|

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 |

|

ZZ |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

DQd |

|

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

63 |

|

DQa |

||||||||||||

DQd |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

62 |

|

DQa |

|||||||||||||

VDDQ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

61 |

|

V |

|||||||||||||

VSS |

|

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DDQ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

|

V |

||||||||||||||

DQd |

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

|

DQa |

||||||||||||||

DQd |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

|

DQa |

|||||||||||||

DQd |

|

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

|

DQa |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

DQd |

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

|

DQa |

||||||||||||

VSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

|

VSS |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

VDDQ |

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

|

VDDQ |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

DQd |

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

53 |

|

DQa |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

DQd |

|

29 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

|

DQa |

||||||||||||

|

30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

NC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

|

NC |

|||||||||||||

|

|

31 32 33 34 35 36 3738 39 40 41 42 43 444546 4748 49 50 |

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LBO SA SA SA SA SA1 SA0 |

NC NC V |

V |

NC NC SA SA SA SA SA SA SA |

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SS |

DD |

|

|

||||||||||||||

MOTOROLA FAST SRAM |

MCM63P733A |

|

3 |

PIN DESCRIPTIONS

Pin Locations |

Symbol |

Type |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Description |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

85 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Synchronous Address Status Controller: Active low, interrupts any |

||||||||||||||||||||||||||

ADSC |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ongoing burst and latches a new external address. Used to initiate a |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

READ, WRITE, or chip deselect. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

84 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Synchronous Address Status Processor: Active low, interrupts any |

|||||||||||||||||||||||||||

|

ADSP |

|||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ongoing burst and latches a new external address. Used to initiate a |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

new READ, WRITE, or chip deselect (exception Ð chip deselect |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

does not occur when |

|

|

|

|

|

is asserted and |

|

is high). |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADSP |

SE1 |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

83 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Synchronous Address Advance: Increments address count in |

||||||||||||||||||||||||||||

|

|

|

ADV |

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

accordance with counter type selected (linear/interleaved). |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

(a) 51, 52, 53, 56, 57, 58, 59, 62, 63 |

|

|

|

DQx |

I/O |

Synchronous Data I/O: ªxº refers to the byte being read or written |

||||||||||||||||||||||||||||||||||||||||

(b) 68, 69, 72, 73, 74, 75, 78, 79, 80 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(byte a, b, c, d). |

||||||||||||||||||||||||||

(c) 1, 2, 3, 6, 7, 8, 9, 12, 13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(d) 18, 19, 22, 23, 24, 25, 28, 29, 30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

86 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Asynchronous Output Enable Input. |

|||||||||||||||||||||||||||||

|

|

|

G |

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

89 |

|

|

|

|

|

|

|

|

K |

Input |

Clock: This signal registers the address, data in, and all control |

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

signals except |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G, LBO, and ZZ. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Linear Burst Order Input: This pin may be left floating; it will default |

|||||||||||||||||||||||||||||

|

|

|

LBO |

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

as interleaved. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Low Ð linear burst counter (68K/PowerPC). |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

High Ð interleaved burst counter (486/i960/Pentium). |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

32, 33, 34, 35, 44, 45, 46, |

|

|

|

|

|

|

|

SA |

Input |

Synchronous Address Inputs: These inputs are registered and must |

||||||||||||||||||||||||||||||||||||

47, 48, 49, 50, 81, 82, 99, 100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

meet setup and hold times. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

36, 37 |

SA1, SA0 |

Input |

Synchronous Address Inputs: These pins must be wired to the two |

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSBs of the address bus for proper burst operation. These inputs |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

are registered and must meet setup and hold times. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

93, 94, 95, 96 |

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Synchronous Byte Write Inputs: ªxº refers to the byte being written |

||||||||||||||||||||||||||||||||

|

|

|

|

SBx |

||||||||||||||||||||||||||||||||||||||||||

(a) (b) (c) (d) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(byte a, b, c, d). |

SGW |

overrides |

SBx. |

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

98 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Synchronous Chip Enable: Active low to enable chip. |

||||||||||||||||||||||||||||||

|

|

|

|

SE1 |

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Negated high Ð blocks |

ADSP |

or deselects chip when |

ADSC |

is |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

asserted. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

97 |

|

|

|

|

SE2 |

Input |

Synchronous Chip Enable: Active high for depth expansion. |

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

92 |

|

|

|

|

|

|

|

|

|

|

Input |

Synchronous Chip Enable: Active low for depth expansion. |

||||||||||||||||||||||||||||||||||

|

|

|

|

SE3 |

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

88 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

Synchronous Global Write: This signal writes all bytes regardless of |

||||||||||||||||||||||||||||

|

SGW |

|||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

the status of the |

SBx |

and |

SW |

signals. If only byte write signals |

SBx |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

are being used, tie this pin high. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||

87 |

|

|

|

|

|

|

|

|

|

|

|

Input |

Synchronous Write: This signal writes only those bytes that have |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

SW |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

been selected using the byte write |

SBx |

pins. If only byte write |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

signals |

SBx |

are being used, tie this pin low. |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

64 |

|

|

|

|

|

|

|

ZZ |

Input |

Sleep Mode: This active high asynchronous signal places the RAM |

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

into the lowest power mode. The ZZ pin disables the RAMs internal |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

clock when placed in this mode. When ZZ is negated, the RAM |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

remains in low power mode until it is commanded to READ or |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WRITE. Data integrity is maintained upon returning to normal |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

operation. |

||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||

15, 41, 65, 91 |

|

|

VDD |

Supply |

Core Power Supply. |

|||||||||||||||||||||||||||||||||||||||||

4, 11, 20, 27, 54, 61, 70, 77 |

VDDQ |

Supply |

I/O Power Supply. |

|||||||||||||||||||||||||||||||||||||||||||

5, 10, 17, 21, 26, 40, |

|

|

|

VSS |

Supply |

Ground. |

||||||||||||||||||||||||||||||||||||||||

55, 60, 67, 71, 76, 90 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

14, 16, 38, 39, 42, 43, 66 |

|

|

|

|

|

|

|

NC |

Ð |

No Connection: There is no connection to the chip. |

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MCM63P733A |

MOTOROLA FAST SRAM |

4 |

|

TRUTH TABLE (See Notes 1 through 5)

|

Address |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

Write 2, 4 |

Next Cycle |

Used |

|

|

|

SE2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DQx |

||

SE1 |

SE3 |

ADSP |

ADSC |

ADV |

G |

|||||||||||||||||

Deselect |

None |

1 |

|

X |

|

X |

|

X |

|

0 |

|

|

X |

|

|

X |

High±Z |

X |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Deselect |

None |

0 |

|

X |

|

1 |

|

0 |

|

|

X |

|

|

X |

|

|

X |

High±Z |

X |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Deselect |

None |

0 |

|

0 |

|

X |

0 |

|

|

X |

|

|

X |

|

|

X |

High±Z |

X |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Deselect |

None |

|

X |

X |

|

1 |

|

1 |

|

0 |

|

|

X |

|

|

X |

High±Z |

X |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Deselect |

None |

|

X |

0 |

|

X |

1 |

|

0 |

|

|

X |

|

|

X |

High±Z |

X |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Begin Read |

External |

0 |

|

1 |

|

0 |

|

0 |

|

|

X |

|

|

X |

|

|

X |

High±Z |

X |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Begin Read |

External |

0 |

|

1 |

|

0 |

|

1 |

|

0 |

|

|

X |

|

|

X |

High±Z |

READ |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Continue Read |

Next |

|

X |

X |

|

X |

1 |

|

1 |

|

0 |

|

1 |

High±Z |

READ |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Continue Read |

Next |

|

X |

X |

|

X |

1 |

|

1 |

|

0 |

|

0 |

DQ |

READ |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Continue Read |

Next |

1 |

|

X |

|

X |

|

X |

|

1 |

|

0 |

|

1 |

High±Z |

READ |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Continue Read |

Next |

1 |

|

X |

|

X |

|

X |

|

1 |

|

0 |

|

0 |

DQ |

READ |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Suspend Read |

Current |

|

X |

X |

|

X |

1 |

|

1 |

|

1 |

|

1 |

High±Z |

READ |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Suspend Read |

Current |

|

X |

X |

|

X |

1 |

|

1 |

|

1 |

|

0 |

DQ |

READ |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Suspend Read |

Current |

1 |

|

X |

|

X |

|

X |

|

1 |

|

1 |

|

1 |

High±Z |

READ |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Suspend Read |

Current |

1 |

|

X |

|

X |

|

X |

|

1 |

|

1 |

|

0 |

DQ |

READ |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Begin Write |

External |

0 |

|

1 |

|

0 |

|

1 |

|

0 |

|

|

X |

|

|

X |

High±Z |

WRITE |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Continue Write |

Next |

|

X |

X |

|

X |

1 |

|

1 |

|

0 |

|

|

X |

High±Z |

WRITE |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Continue Write |

Next |

1 |

|

X |

|

X |

|

X |

|

1 |

|

0 |

|

|

X |

High±Z |

WRITE |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Suspend Write |

Current |

|

X |

X |

|

X |

1 |

|

1 |

|

1 |

|

|

X |

High±Z |

WRITE |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Suspend Write |

Current |

1 |

|

X |

|

X |

|

X |

|

1 |

|

1 |

|

|

X |

High±Z |

WRITE |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.X = Don't Care. 1 = logic high. 0 = logic low.

2.Write is defined as either 1) any SBx and SW low, or 2) SGW is low.

3.G is an asynchronous signal and is not sampled by the clock K. G drives the bus immediately (tGLQX) following G going low.

4.On write cycles that follow read cycles, G must be negated prior to the start of the write cycle to ensure proper write data setup times. G must also remain negated at the completion of the write cycle to ensure proper write data hold times.

ASYNCHRONOUS TRUTH TABLE

|

|

|

|

|

|

Operation |

ZZ |

G |

|

I/O Status |

|

|

|

|

|

|

|

Read |

L |

|

L |

|

Data Out (DQx) |

|

|

|

|

|

|

Read |

L |

|

H |

|

High±Z |

|

|

|

|

|

|

Write |

L |

|

X |

|

High±Z |

|

|

|

|

|

|

Deselected |

L |

|

X |

|

High±Z |

|

|

|

|

|

|

Selected |

H |

|

X |

|

High±Z |

|

|

|

|

|

|

LINEAR BURST ADDRESS TABLE (LBO = VSS)

1st Address (External) |

2nd Address (Internal) |

3rd Address (Internal) |

4th Address (Internal) |

||||

|

|

|

|

|

|

|

|

X . . . |

X00 |

X . . . |

X01 |

X . . . |

X10 |

X . . . |

X11 |

|

|

|

|

|

|

|

|

X . . . |

X01 |

X . . . |

X10 |

X . . . |

X11 |

X . . . |

X00 |

|

|

|

|

|

|

|

|

X . . . |

X10 |

X . . . |

X11 |

X . . . |

X00 |

X . . . |

X01 |

|

|

|

|

|

|

|

|

X . . . |

X11 |

X . . . |

X00 |

X . . . |

X01 |

X . . . |

X10 |

|

|

|

|

|

|

|

|

MOTOROLA FAST SRAM |

MCM63P733A |

|

5 |

Loading...

Loading...