Fairchild Semiconductor DM74ALS138SJX, DM74ALS138SJ, DM74ALS138N, DM74ALS138MX, DM74ALS138M Datasheet

© 2000 Fairchild Semiconductor Corporation DS006111 www.fairchildsemi.com

September 1986

Revised February 2000

DM74ALS138 3 to 8 Line Decoder/Demultiplexer

DM74ALS138

3 to 8 Line Decoder/Demultiplexer

General Description

These Schottky-clamped circuits are designed to be used

in high-performance memory-decoding or data-routing

applications, requiring very short propagatio n delay times.

In high-performance memo ry systems these decoders can

be used to minimize the effects of system decoding. When

used with high-speed me mories, the delay tim es of these

decoders are usually less th an the typical access time of

the memory. This means that the effective system delay

introduced by the decoder is negligible.

The DM74ALS138 decodes one-of-eight lines, based upon

the conditions at the three binary select inputs and the

three enable inputs. Two active-LOW and one active-HIGH

enable inputs reduce the need fo r external gate s or invert-

ers when expanding. A 24-line decoder can be imple-

mented with no external inverters, and 32-line decoder

requires only one inverter. An enable input can be used as

a data input for demultiplexing applications.

This decoder/demul tiplexer features fully buffered inputs,

presenting only one normalized load to its driving circuit. All

inputs are clamped wit h hig h-p er for man ce Sc h ottk y diod es

to suppress line-ringing and simplify system design.

Features

■ Designed specifically for high speed:

Memory decoders

Data transmission systems

■ 3- to 8-line decoder inco rpo ra tes 3 enable inputs to sim-

plify cascading and/or data reception

■ Low power dissipation…23 mW typ

■ Switching specifications guaranteed over full tempera-

ture and V

CC

range

■ Advanced oxide-isolated, ion-implanted Schottky TTL

process

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

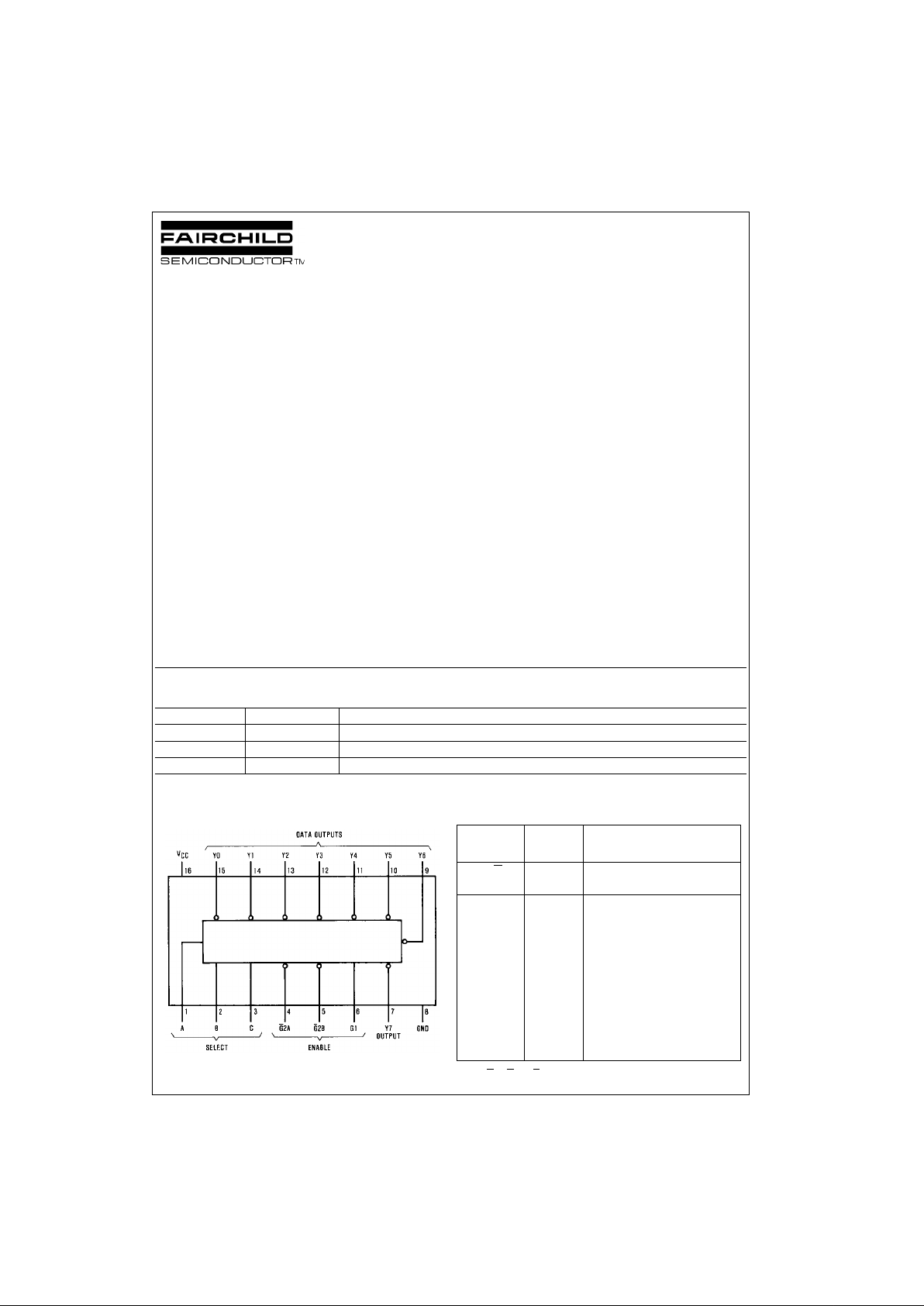

Connection Diagram Function Table

Note 1: G2 = G2A + G2B

Order Number Package Number Package Description

DM74ALS138M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74ALS138SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

DM74ALS138N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Enable Select

Outputs

Inputs Inputs

G1 G

2

(Note 1)

C B AY0Y1Y2Y3Y4Y5Y6Y7

X H XXXHHHHHHHH

L X XXXHHHHHHHH

H L L LL LHHHHHHH

H L L LHHLHHHHHH

H L LHLHHLHHHHH

H L LHHHHHLHHHH

H L HLLHHHHLHHH

H L HLHHHHHHLHH

H L HHLHHHHHHLH

H L HHHHHHHHHHL

www.fairchildsemi.com 2

DM74ALS138

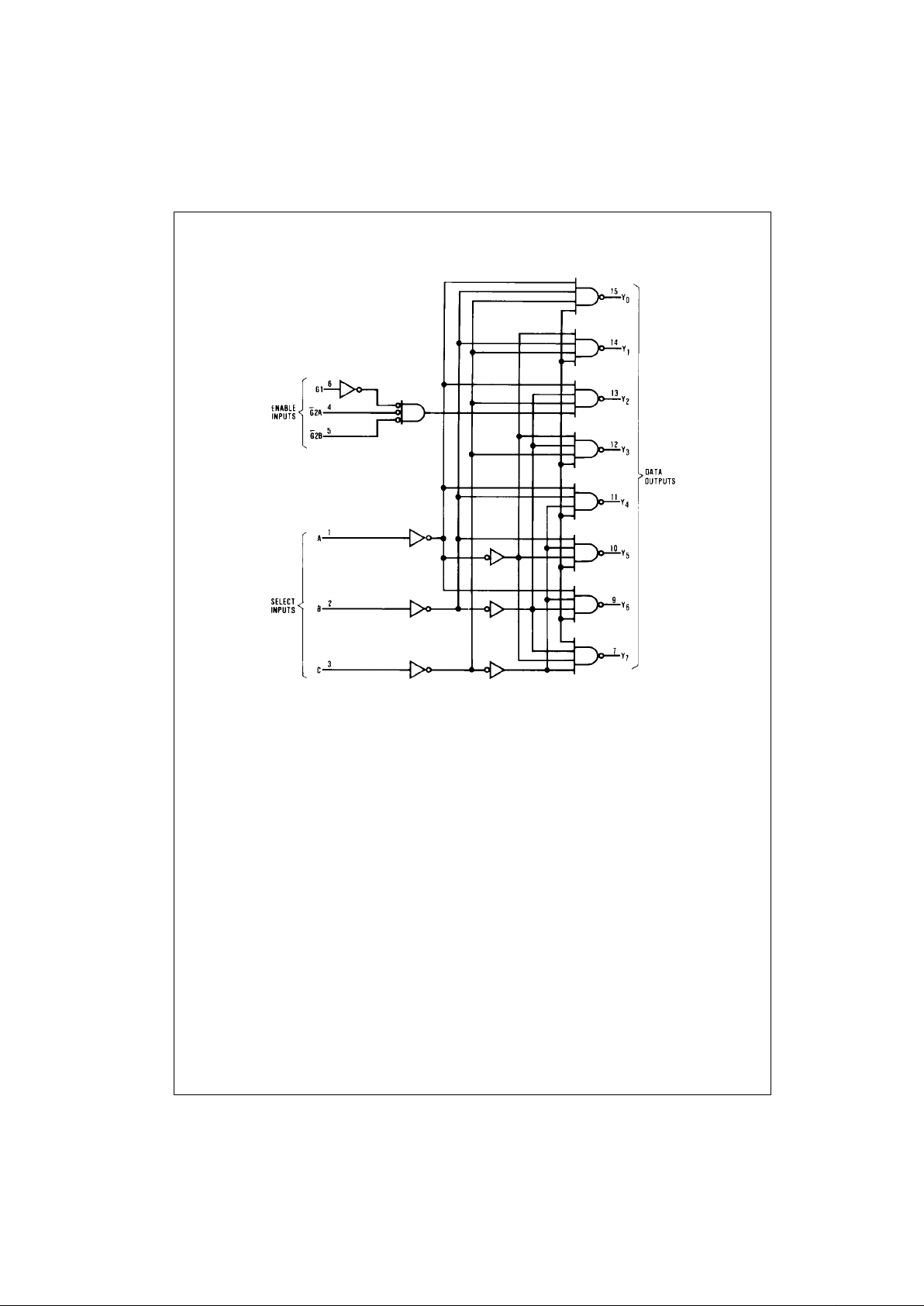

Logic Diagram

Loading...

Loading...