Motorola MC12036AD, MC12036AP, MC12036BD Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

1.1GHz |

Dual Modulus Prescaler |

|

MC12036A |

With Stand-By Mode |

|

||

|

MC12036B |

||

Consider |

MC12053 for New Designs |

||

The MC12036 is a 1.1GHz 64/65, 128/129 dual modulus prescaler used in phase±locked loop (PLL) applications. Stand±By mode is featured to reduce current drain to 0.5mA typical when the standby pin (SB) is switched LOW, disabling the prescaler. On±chip output termination provides sufficient output current to drive a 12pF (typical) high impedance load.

The MC12036A can be used with CMOS synthesizers requiring positive edges to trigger internal counters such as Motorola's MC145xxx series in a PLL to provide tuning signals up to 1.1GHz in programmable frequency steps. The MC12036B can be used with CMOS synthesizers requiring negative edges to trigger internal counters.

A Divide Ratio Control (SW) permits selection of a 64/65 or 128/129 divide ratio as desired.

The Modulus Control (MC) selects the proper divide number after SW has been biased to select the desired divide ratio.

•1.1GHz Toggle Frequency

•Low Power 4.0mA Typical

•Stand±By Mode

•On±Chip Output Termination

•Supply Voltage 4.5V to 5.5V

•Operating Temperature Range of ±40°C to +85°C

•Short Setup Time (tset ) 16ns Maximum @ 1.1GHz

•Modulus Control Input Level is Compatible With Standard CMOS and TTL

Pinout: 8±Lead Plastic (Top View)

|

IN |

|

SB |

|

MC |

|

GND |

|

|

|

|

|

|

|

|

|

|

|

8 |

|

7 |

|

6 |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

3 |

|

4 |

|

|

|

|

|

|

IN |

VCC |

SW |

|

OUT |

|

|||||

|

|

|

|

|

|

|

|

|||||

Design Criteria |

|

|

|

|

|

Value |

Unit |

|||||

|

|

|

|

|

|

|

||||||

Internal Gate Count * |

|

|

|

|

|

|

|

67 |

ea |

|||

|

|

|

|

|

||||||||

Internal Gate Propagation Delay |

|

|

|

|

|

200 |

ps |

|||||

|

|

|

|

|

|

|

||||||

Internal Gate Power Dissipation |

|

|

|

|

|

|

|

0.75 |

mW |

|||

|

|

|

|

|

|

|

||||||

Speed Power Product |

|

|

|

|

|

|

|

0.15 |

pJ |

|||

*Equivalent to a two±input NAND gate.

MECL PLL COMPONENTS

64/65, 128/129

DUAL MODULUS PRESCALER WITH STAND±BY MODE

P SUFFIX

8±LEAD PLASTIC PACKAGE

CASE 626±05

D SUFFIX

8±LEAD PLASTIC SOIC PACKAGE

CASE 751±05

FUNCTION TABLE

SW |

MC |

Divide Ratio |

|

|

|

H |

H |

64 |

|

|

|

H |

L |

65 |

|

|

|

L |

H |

128 |

|

|

|

L |

L |

129 |

|

|

|

Note: SW: H = VCC, L = OPEN

MC: H = 2.0V to VCC, L = GND to 0.8V

1/97

Motorola, Inc. 1997 |

1 |

REV 2 |

MC12036A MC12036B

MAXIMUM RATINGS

Symbol |

Characteristic |

Range |

Unit |

|

|

|

|

VCC |

Power Supply Voltage, Pin 2 |

±0.5 to +7.0 |

Vdc |

TA |

Operating Temperature Range |

±40 to +85 |

°C |

Tstg |

Storage Temperature Range |

±65 to +150 |

°C |

MC |

Modulus Control Input, Pin 6 |

±0.5 to +6.5 |

Vdc |

ELECTRICAL CHARACTERISTICS (VCC = 4.5 to 5.5 Vdc, TA = ±40°C to +85°C)

Symbol |

Characteristic |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

ft |

Toggle Frequency (Sine Wave Input) |

0.1 |

1.4 |

1.1 |

GHz |

ICC |

Supply Current (Pin 2) |

Ð |

4.0 |

6.5 |

mA |

VIH1 |

Modulus Control & Standby Input High (MC & SB) |

2.0 |

Ð |

VCC |

V |

VIL1 |

Modulus Control & Standby Input Low (MC & SB) |

Ð |

Ð |

0.8 |

V |

VIH2 |

Divide Ratio Control Input High (SW) |

VCC |

VCC |

VCC |

Vdc |

VIL2 |

Divide Ratio Control Input Low (SW) |

OPEN |

OPEN |

OPEN |

Ð |

Vout |

Output Voltage Swing, CL = 8pF |

1.0 |

1.4 |

Ð |

Vp±p |

tSET |

Modulus Setup Time MC to Out |

Ð |

11 |

16 |

ns |

Vin |

Input Voltage Sensitivity 250±1100 MHz |

100 |

Ð |

1000 |

mVpp |

|

100±250 MHz |

400 |

Ð |

1000 |

|

|

|

|

|

|

|

ISB |

Standby Current |

Ð |

0.5 |

Ð |

mA |

|

|

|

D |

Q |

|

D |

Q |

|

D |

Q |

|

|

|

Prop. Delay |

|

|

|

|

A |

|

|

B |

|

|

C |

|

|

|

In |

|

|

|

C |

QB |

|

C |

QB |

|

C |

QB |

|

|

|

|

In |

|

|

|

|

M |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In |

|

|

|

|

|

|

|

|

|

|

|

|

|

Out |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MC |

|

|

|

|

|

|

|

|

|

|

|

|

|

MC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SB |

|

|

|

|

|

|

|

|

|

|

|

|

|

MC Setup |

D |

Q |

D |

QB |

|

D |

Q |

|

D |

QB |

|

D |

QB |

|

MC Release |

|

|

|

|

|

||||||||||

|

D |

|

E |

|

|

F |

|

|

G |

|

|

H |

|

Modulus setup time MC to out is the MC |

C |

QB |

C |

Q |

|

C |

QB |

|

C |

Q |

|

C |

S Q |

Out |

|

|

|

|

setup or MC release plus the prop. delay. |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SW |

|

|

|

|

|

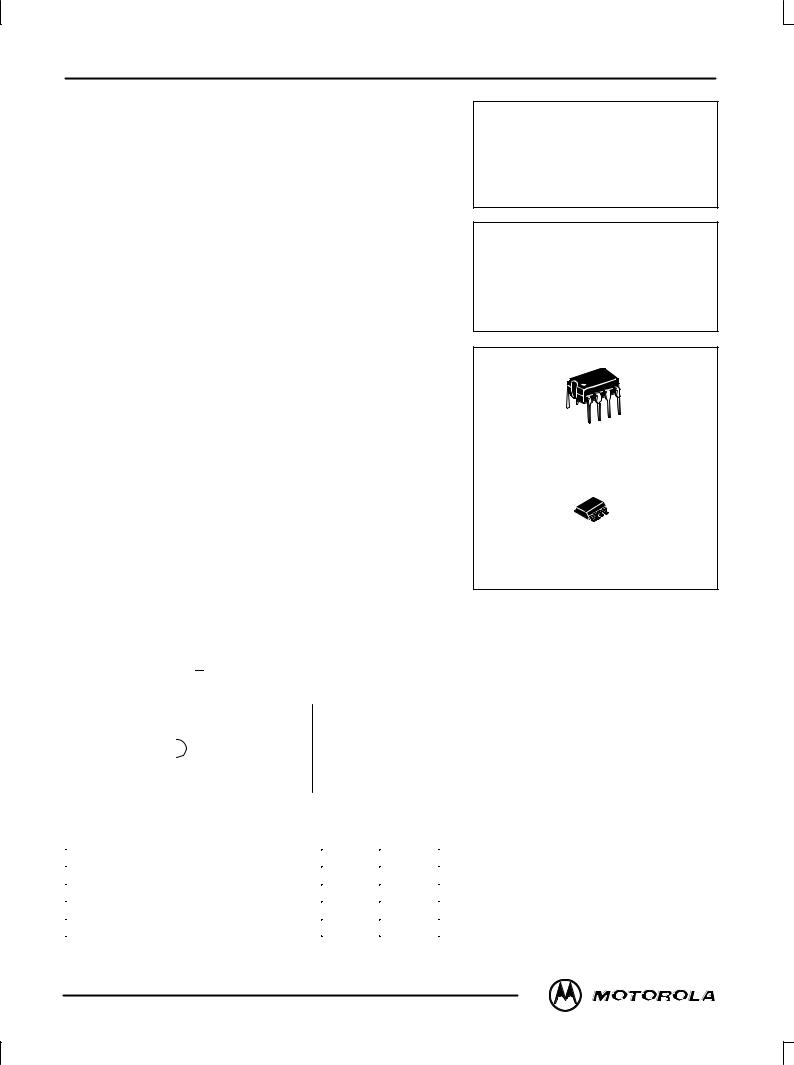

Figure 1. Logic Diagram (MC12036A) |

Figure 2. Modulus Setup Time |

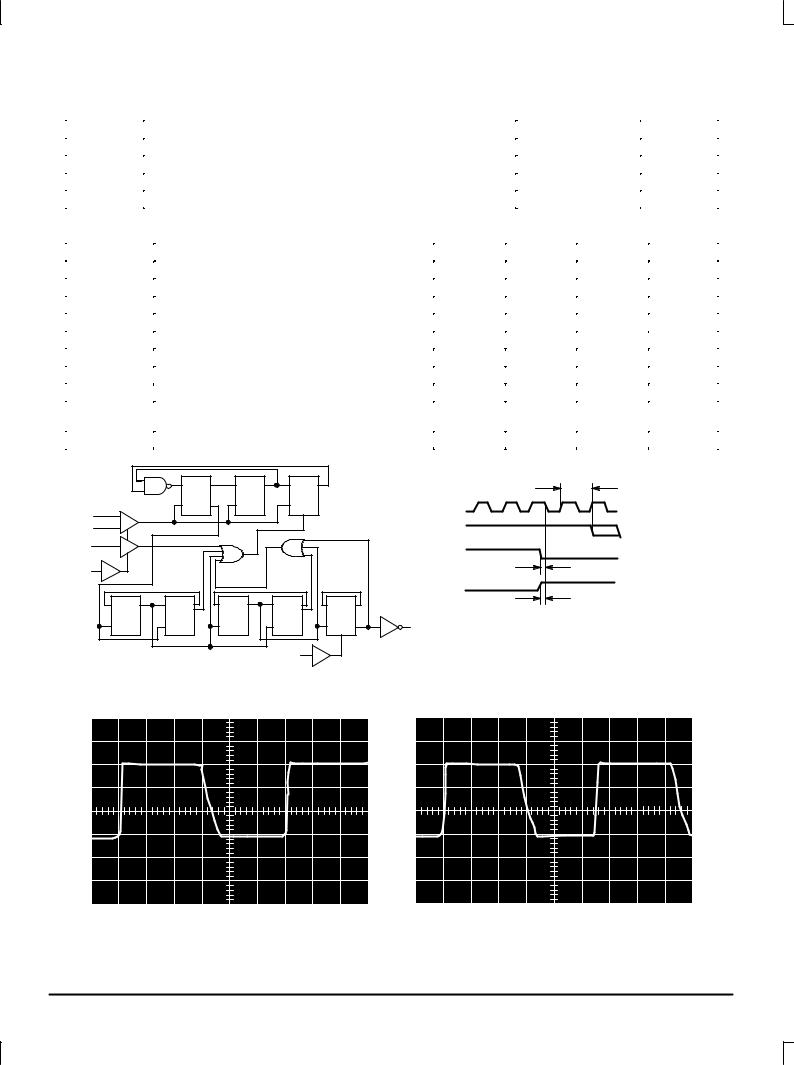

500 m≈ |

20 ns |

( 64, 500MHz Input Frequency, VCC = 5.0V, TA = 25°C, |

|

|

Output Loaded) |

500 m≈ |

20 ns |

( 128, 1.1GHz Input Frequency, VCC = 5.0V, TA = 25°C, |

|

|

Output Loaded) |

Figure 3. Typical Output Waveform

MOTOROLA |

2 |

HIPERCOMM |

|

|

BR1334 Ð Rev 4 |

Loading...

Loading...