Motorola MC12034AD, MC12034AP, MC12034BD, MC12034BP Datasheet

Order this document by MC12034A/D

MC12034A 2.0GHz Dual Modulus Prescaler MC12034B

MC12034A 2.0GHz Dual Modulus Prescaler MC12034B

The MC12034A can be used with CMOS synthesizers requiring positive |

|

|

|

|

|

||||||||||

|

|

|

|

|

|||||||||||

edges to trigger internal counters such as Motorola's MC145xxx series in a |

|

|

|

|

|

||||||||||

PLL to provide tuning signals up to 2.0 GHz in programmable frequency |

MECL PLL COMPONENTS |

||||||||||||||

steps. |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

32/33, |

64/65 |

||||||

The MC12034B can be used with CMOS synthesizers requiring negative |

|||||||||||||||

|

|

|

|

|

|||||||||||

edges to trigger internal counters such as Fujitsu's MB87001. |

|

|

DUAL MODULUS PRESCALER |

||||||||||||

A Divide Ratio Control (SW) permits selection of a 32/33 or 64/65 divide |

|||||||||||||||

|

|

|

|

|

|||||||||||

ratio as desired. |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

The Modulus Control (MC) selects the proper divide number after SW has |

SEMICONDUCTOR |

||||||||||||||

been biased to select the desired divide ratio. |

|

|

|

|

TECHNICAL DATA |

||||||||||

• 2.0 GHz Toggle Frequency |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

• Supply Voltage 4.5 to 5.5 V |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

• MC12034A for Positive Edge Triggered Synthesizers |

|

|

|

|

|

|

|

||||||||

• 12mA Maximum, ±40 to 85°C, VCC = 5.5 Vdc |

|

|

|

|

|

8 |

|

|

|

||||||

• Modulus Control Input is Compatible with Standard CMOS and TTL |

|

|

1 |

|

|

||||||||||

|

|

|

|

|

|||||||||||

• Low±Power 8.5 mA Typical |

|

|

|

|

|

|

|

D SUFFIX |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

FUNCTIONAL TABLE |

|

|

|

|

|

|

|

|

PLASTIC PACKAGE |

||||||

|

|

|

|

|

|

|

|

|

CASE 751 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

SW |

|

MC |

|

Divide Ratio |

|

|

|

(SO±8) |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

H |

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

L |

|

|

|

33 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

H |

|

|

|

64 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

|

|

|

65 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

NOTES: 1. SW: H = VCC, L = Open. A logic L can also be applied by grounding this pin, |

|

8 |

|

|

|

||||||||||

but this is not recommended due to increased power consumption. |

|

|

|

|

|

|

|

||||||||

2. MC: H = 2.0 V to VCC, L = GND to 0.8 V. |

|

|

|

|

|

1 |

|

|

|

||||||

|

Design Criteria |

|

|

Value |

|

Unit |

|

|

P SUFFIX |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Internal Gate Count * |

|

|

|

|

67 |

|

ea |

|

PLASTIC PACKAGE |

||||||

|

|

|

|

|

|

|

|

|

|

|

CASE 626 |

|

|

||

Internal Gate Propagation Delay |

|

|

200 |

|

ps |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

Internal Gate Power Dissipation |

|

|

0.75 |

|

mW |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Speed Power Product |

|

|

|

|

0.15 |

|

pJ |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

NOTE: *Equivalent to a two±input NAND gate. |

|

|

|

|

|

|

PIN CONNECTIONS |

||||||||

|

|

|

|

|

|

|

|

|

|

||||||

MAXIMUM RATINGS |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||||

Characteristic |

Symbol |

|

Range |

Unit |

|

|

|

|

|

|

|||||

IN |

1 |

8 |

IN |

||||||||||||

Power Supply Voltage, Pin 2 |

VCC |

|

±0.5 to +7.0 |

Vdc |

|

V |

2 |

7 |

NC |

||||||

|

|

CC |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

SW 3 |

6 |

MC |

|||

Operating Temperature Range |

TA |

|

±40 to +85 |

°C |

|

||||||||||

|

|

OUT |

4 |

5 |

Gnd |

||||||||||

Storage Temperature Range |

Tstg |

|

±65 to +150 |

°C |

|

||||||||||

|

|

|

(Top View) |

|

|

||||||||||

Modulus Control Input, Pin 6 |

MC |

|

±0.5 to +6.5 |

Vdc |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES: 1. ESD data available upon request.

2.This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high

impedance circuit. For proper operation, Vin and Vout should be constrained |

ORDERING INFORMATION |

|||

to the range GND ≤ (Vin or Vout) ≤ VCC. |

|

|

|

|

|

Operating |

|

||

|

|

|

|

|

|

|

Device |

Temp Range |

Package |

|

|

|

|

|

|

|

MC12034AD |

|

SO±8 |

|

|

|

|

|

|

|

MC12034AP |

TA = ±40° to +85°C |

Plastic |

|

|

|

|

|

|

|

MC12034BD |

SO±8 |

|

|

|

|

||

|

|

|

|

|

|

|

MC120348BP |

|

Plastic |

|

|

|

|

|

Motorola, Inc. 1997 |

Rev 3 |

MC12034A MC12034B

ELECTRICAL CHARACTERISTICS (VCC = 4.5 to 5.5 Vdc, TA = ±40 to 85°C, unless otherwise noted.)

Characteristic |

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

Toggle Frequency (Sine Wave) |

ft |

0.5 |

2.4 |

2.0 |

GHz |

Supply Current Output Unloaded (Pin 2) |

ICC |

± |

8.5 |

12 |

mA |

Modulus Control Input High (MC) |

VIH1 |

2.0 |

± |

VCC |

V |

Modulus Control Input Low (MC) |

VIL1 |

± |

± |

0.8 |

V |

Divide Ratio Control Input High (SW) |

VIH2 |

VCC |

VCC |

VCC |

Vdc |

Divide Ratio Control Input Low (SW) |

VIL2 |

OPEN |

OPEN |

OPEN |

± |

Output Voltage Swing (CL = 12 pF, RL = 1.1 kΩ) |

Vout |

1.0 |

1.6 |

± |

Vpp |

Modulus Setup Time MC to Out |

tSET |

± |

8.0 |

10.0 |

ns |

Input Voltage Sensitivity 500±2000 MHz |

Vin |

100 |

± |

1500 |

mVpp |

Output Current (CL = 12 pF, RL = 1.1 kΩ) |

IO |

± |

± |

3.5 |

mA |

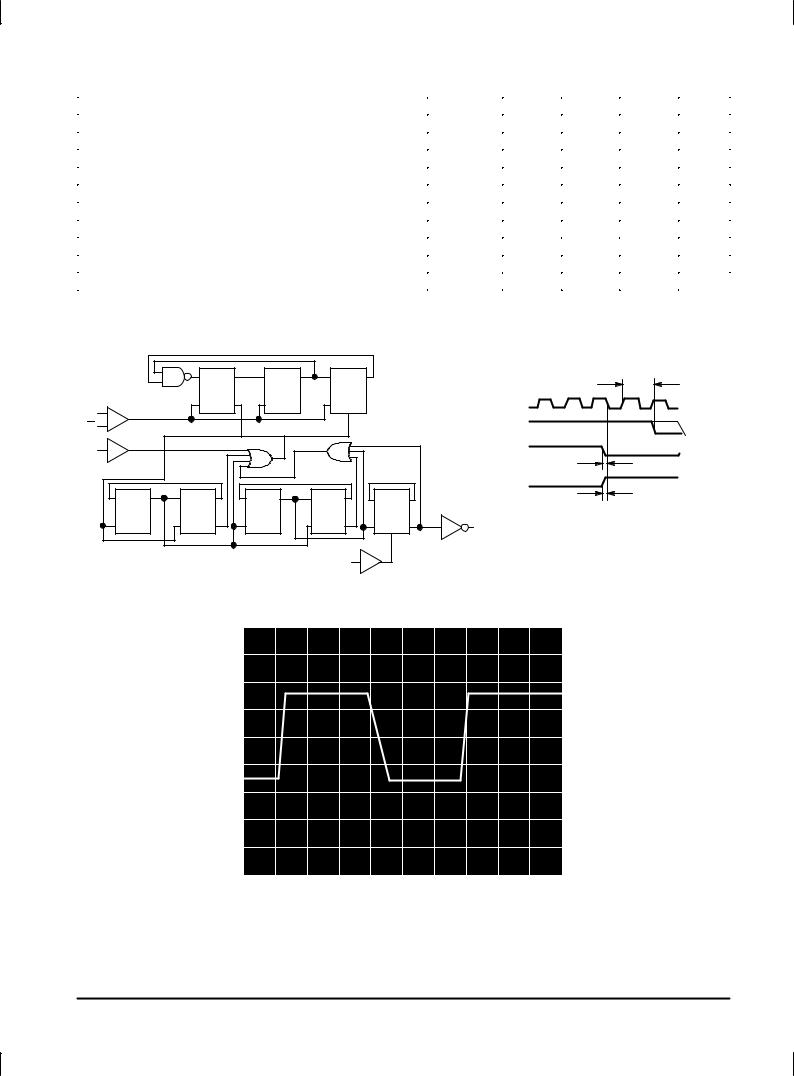

Figure 1. Logic Diagram (MC12034A) |

Figure 2. Modulus Setup Time |

|||||

D |

Q |

D |

Q |

D |

Q |

PROP. DELAY |

|

A |

|

B |

|

C |

|

|

|

|

|

|||

C |

QB |

C |

QB |

C |

QB |

IN |

M |

|

|||||

In |

|

|

|

|

|

|

In |

|

|

|

|

|

OUT |

MC |

|

|

|

|

|

|

|

|

|

|

MC |

|

|

|

|

|

|

|

|

|

|

|

|

MC SETUP |

|

D |

Q |

D |

QB |

D |

Q |

D |

QB |

D |

QB |

|

MC RELEASE |

|

|

|

|||||||||||

|

D |

|

E |

|

F |

|

G |

|

H |

|

Modulus setup time MC to out is the MC |

|

C |

QB |

C |

Q |

C |

QB |

C |

Q |

C |

S Q |

Out |

||

setup or MC release plus the prop. delay. |

||||||||||||

|

|

|

|

|

|

|

SW |

|

|

|

|

Figure 3. Typical Output Waveform

500 m ≈ |

20 ns |

2 |

MOTOROLA RF/IF DEVICE DATA |

Loading...

Loading...