Motorola MC14044BCL, MC14044BCP, MC14044BD, MC14043BD, MC14043BCL Datasheet

...

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

CMOS MSI

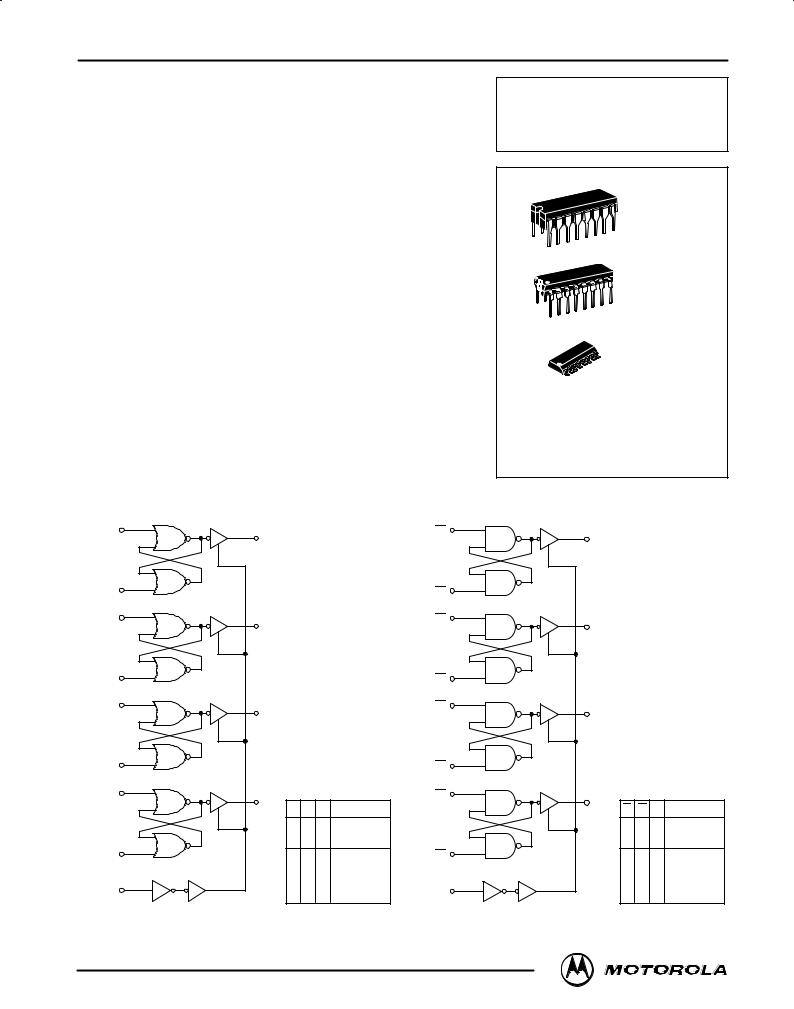

Quad R±S Latches

The MC14043B and MC14044B quad R±S latches are constructed with MOS P±channel and N±channel enhancement mode devices in a single monolithic structure. Each latch has an independent Q output and set and reset inputs. The Q outputs are gated through three±state buffers having a common enable input. The outputs are enabled with a logical ª1º or high on the enable input; a logical ª0º or low disconnects the latch from the Q outputs, resulting in an open circuit at the Q outputs.

•Double Diode Input Protection

•Three±State Outputs with Common Enable

•Outputs Capable of Driving Two Low±power TTL Loads or One Low± Power Schottky TTL Load Over the Rated Temperature Range

•Supply Voltage Range = 3.0 Vdc to 18 Vdc

MC14043B

MC14044B

L SUFFIX

CERAMIC

CASE 620

P SUFFIX

PLASTIC

CASE 648

D SUFFIX

SOIC

CASE 751B

ORDERING INFORMATION

MC14XXXBCP Plastic MC14XXXBCL Ceramic MC14XXXBD SOIC

TA = ± 55° to 125°C for all packages.

|

MC14043B |

|

|

|

|

|

MC14044B |

|

|

|

|

4 |

2 |

|

|

|

|

4 |

13 |

|

|

|

|

S0 |

|

|

|

|

R0 |

|

|

|

|

||

|

Q0 |

|

|

|

|

|

Q0 |

|

|

|

|

3 |

|

|

|

|

|

3 |

|

|

|

|

|

R0 |

|

|

|

|

|

S0 |

|

|

|

|

|

6 |

9 |

|

|

|

|

6 |

9 |

|

|

|

|

S1 |

|

|

|

|

R1 |

|

|

|

|

||

|

Q1 |

|

|

|

|

|

Q1 |

|

|

|

|

7 |

|

|

VDD = PIN 16 |

7 |

|

|

VDD = PIN 16 |

||||

R1 |

|

|

S1 |

|

|

||||||

12 |

|

|

|

VSS = PIN 8 |

12 |

|

|

VSS = PIN 8 |

|||

10 |

|

|

NC = PIN 13 |

10 |

|

NC = PIN 2 |

|||||

S2 |

|

|

|

|

R2 |

|

|

|

|

||

|

Q2 |

|

|

|

|

|

Q2 |

|

|

|

|

11 |

|

|

|

|

|

11 |

|

|

|

|

|

R2 |

|

|

|

|

|

S2 |

|

|

|

|

|

14 |

1 |

|

TRUTH TABLE |

14 |

1 |

|

TRUTH TABLE |

||||

S3 |

|

R3 |

|

||||||||

|

Q3 |

S R E |

Q |

|

Q3 |

S R E |

Q |

||||

|

|

|

|

||||||||

|

|

X |

X |

0 |

High |

|

|

X |

X |

0 |

High |

15 |

|

|

|

|

Impedance |

15 |

|

|

|

|

Impedance |

|

|

|

|

|

|

|

|

|

|

||

R3 |

|

0 |

0 |

1 |

No Change |

S3 |

|

0 |

0 |

1 |

0 |

|

|

0 |

1 |

1 |

0 |

|

|

0 |

1 |

1 |

1 |

5 |

|

1 |

0 |

1 |

1 |

5 |

|

1 |

0 |

1 |

0 |

ENABLE |

|

1 |

1 |

1 |

1 |

ENABLE |

|

1 |

1 |

1 |

No Change |

|

X = Don't Care |

|

X = Don't Care |

||||||||

|

|

|

|

||||||||

REV 3 |

|

|

|

|

|

|

|

|

|

|

|

1/94 |

|

|

|

|

|

|

|

|

|

|

|

Motorola, Inc. 1995

ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS)

|

|

|

VDD |

± 55_C |

|

25_C |

|

125_C |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

|

Symbol |

Vdc |

Min |

Max |

Min |

Typ # |

Max |

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage |

ª0º Leve |

VOL |

5.0 |

Ð |

0.05 |

Ð |

0 |

0.05 |

Ð |

0.05 |

Vdc |

Vin = VDD or 0 |

|

|

10 |

Ð |

0.05 |

Ð |

0 |

0.05 |

Ð |

0.05 |

|

|

|

|

15 |

Ð |

0.05 |

Ð |

0 |

0.05 |

Ð |

0.05 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ª1º Leve |

VOH |

5.0 |

4.95 |

Ð |

4.95 |

5.0 |

Ð |

4.95 |

Ð |

Vdc |

Vin = 0 or VDD |

|

|

10 |

9.95 |

Ð |

9.95 |

10 |

Ð |

9.95 |

Ð |

|

|

|

|

15 |

14.95 |

Ð |

14.95 |

15 |

Ð |

14.95 |

Ð |

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltage |

ª0º Leve |

VIL |

|

|

|

|

|

|

|

|

Vdc |

(VO = 4.5 or 0.5 Vdc) |

|

|

5.0 |

Ð |

1.5 |

Ð |

2.25 |

1.5 |

Ð |

1.5 |

|

(VO = 9.0 or 1.0 Vdc) |

|

|

10 |

Ð |

3.0 |

Ð |

4.50 |

3.0 |

Ð |

3.0 |

|

(VO = 13.5 or 1.5 Vdc) |

|

|

15 |

Ð |

4.0 |

Ð |

6.75 |

4.0 |

Ð |

4.0 |

|

(VO = 0.5 or 4.5 Vdc) |

ª1º Leve |

VIH |

5.0 |

3.5 |

Ð |

3.5 |

2.75 |

Ð |

3.5 |

Ð |

Vdc |

|

|

|

|||||||||

(VO = 1.0 or 9.0 Vdc) |

|

|

10 |

7.0 |

Ð |

7.0 |

5.50 |

Ð |

7.0 |

Ð |

|

(VO = 1.5 or 13.5 Vdc) |

|

|

15 |

11 |

Ð |

11 |

8.25 |

Ð |

11 |

Ð |

|

Output Drive Current |

|

IOH |

|

|

|

|

|

|

|

|

mAdc |

(VOH = 2.5 Vdc) |

Source |

|

5.0 |

± 3.0 |

Ð |

± 2.4 |

± 4.2 |

Ð |

± 1.7 |

Ð |

|

(VOH = 4.6 Vdc) |

|

|

5.0 |

± 0.64 |

Ð |

± 0.51 |

± 0.88 |

Ð |

± 0.36 |

Ð |

|

(VOH = 9.5 Vdc) |

|

|

10 |

± 1.6 |

Ð |

± 1.3 |

± 2.25 |

Ð |

± 0.9 |

Ð |

|

(VOH = 13.5 Vdc) |

|

|

15 |

± 4.2 |

Ð |

± 3.4 |

± 8.8 |

Ð |

± 2.4 |

Ð |

|

(VOL = 0.4 Vdc) |

Sink |

IOL |

5.0 |

0.64 |

Ð |

0.51 |

0.88 |

Ð |

0.36 |

Ð |

mAdc |

(VOL = 0.5 Vdc) |

|

|

10 |

1.6 |

Ð |

1.3 |

2.25 |

Ð |

0.9 |

Ð |

|

(VOL = 1.5 Vdc) |

|

|

15 |

4.2 |

Ð |

3.4 |

8.8 |

Ð |

2.4 |

Ð |

|

Input Current |

|

Iin |

15 |

Ð |

± 0.1 |

Ð |

± 0.00001 |

± 0.1 |

Ð |

± 1.0 |

μAdc |

Input Capacitance |

|

Cin |

Ð |

Ð |

Ð |

Ð |

5.0 |

7.5 |

Ð |

Ð |

pF |

(Vin = 0) |

|

|

|

|

|

|

|

|

|

|

|

Quiescent Current |

|

IDD |

5.0 |

Ð |

1.0 |

Ð |

0.002 |

1.0 |

Ð |

30 |

μAdc |

(Per Package) |

|

|

10 |

Ð |

2.0 |

Ð |

0.004 |

2.0 |

Ð |

60 |

|

|

|

|

15 |

Ð |

4.0 |

Ð |

0.006 |

4.0 |

Ð |

120 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Total Supply Current**² |

|

IT |

5.0 |

|

|

IT = (0.58 μA/kHz) f + IDD |

|

|

μAdc |

||

(Dynamic plus Quiescent, |

|

10 |

|

|

IT = (1.15 μA/kHz) f + IDD |

|

|

|

|||

Per Package) |

|

|

15 |

|

|

IT = (1.73 μA/kHz) f + IDD |

|

|

|

||

(CL = 50 pF on all outputs all |

|

|

|

|

|

|

|

|

|

|

|

buffers switching) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Three±State Output Leakage |

ITL |

15 |

Ð |

± 0.1 |

Ð |

± 0.0001 |

± 0.1 |

Ð |

± 3.0 |

μAdc |

|

Current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

#Data labelled ªTypº is not to be used for design purposes but is intended as an indication of the IC's potential performance.

** The formulas given are for the typical characteristics only at 25_C.

²T o calculate total supply current at loads other than 50 pF:

IT(CL) = IT(50 pF) + (CL ± 50) Vfk

where: IT is in μA (per package), CL in pF, V = (VDD ± VSS) in volts, f in kHz is input frequency, and k = 0.004.

* Maximum Ratings are those values beyond which damage to the device may occur. ²Temperature Derating: Plastic ªP and D/DWº Packages: ± 7.0 mW/C From 65_C To 125_C

Ceramic ªLº Packages ± 12 mW/C From 100_C To 125_C

MOTOROLA CMOS LOGIC DATA |

MC14043B MC14044B |

|

163 |

Loading...

Loading...