Motorola MC12009P, MC12011P, MC12013P Datasheet

Dual Modulus Prescaler

These devices are two±modulus prescalers which will divide by 5 and 6, 8 and 9, and 10 and 11, respectively. A MECL±to±MTTL translator is provided to interface directly with the MC12014 Counter Control Logic. In addition, there is a buffered clock input and MECL bias voltage source.

•MC12009 480 MHz (B5/6), MC12011 550 MHz (B8/9), MC12013 550 MHz (B10/11)

•MECL to MTTL Translator on Chip

•MECL and MTTL Enable Inputs

•5.0 or ±5.2 V Operation*

•Buffered Clock Input Ð Series Input RC Typ, 20 Ohms and 4 pF

•VBB Reference Voltage

•310 Milliwatts (Typ)

*When using a 5.0 V supply, apply 5.0 V to Pin 1 (VCCO), Pin 6

(MTTL VCC), Pin 16 (VCC), and ground Pin 8 (VEE). When using

±5.2 V supply, ground Pin 1 (VCCO), Pin 6 (MTTL VCC), and

Pin 16 (VCC) and apply ±5.2 V to Pin 8 (VEE). If the translator is not required, Pin 6 may be left open to conserve dc power drain.

MAXIMUM RATINGS

Characteristic |

Symbol |

|

Rating |

|

Unit |

|

|

|

|

|

|

(Ratings above which device life may be impaired) |

|

|

|

||

|

|

|

|

|

|

Power Supply Voltage |

VEE |

|

±8.0 |

|

Vdc |

(VCC = 0) |

|

|

|

|

|

Input Voltage |

Vin |

|

0 to VEE |

|

Vdc |

(VCC = 0) |

|

|

|

|

|

Output Source Current |

IO |

|

|

|

mAdc |

Continuous |

|

|

t50 |

|

|

Surge |

|

|

t100 |

|

|

|

|

|

|

|

|

Storage Temperature Range |

Tstg |

|

±65 to +175 |

|

°C |

(Recommended Maximum Ratings above which performance may be |

|

||||

degraded) |

|

|

|

|

|

|

|

|

|

||

Operating Temperature Range |

TA |

|

±30 to +85 |

|

°C |

MC12009, MC12011, MC12013 |

|

|

|

|

|

|

|

|

|

|

|

DC Fan±Out (Note 1) |

n |

|

70 |

|

Ð |

(Gates and Flip±Flops) |

|

|

|

|

|

|

|

|

|

|

|

NOTES: 1. AC fan±out is limited by desired system performance. 2. ESD data available upon request.

Order this document by MC12009/D

MC12009

MC12011

MC12013

MECL PLL COMPONENTS DUAL MODULUS PRESCALER

SEMICONDUCTOR

TECHNICAL DATA

16

1

P SUFFIX

PLASTIC PACKAGE

CASE 648

PIN CONNECTIONS

|

|

|

|

|

|

|

|

|

VCC |

V |

1 |

|

|

|

|

16 |

|||

CCO |

|

|

|

|

|

|

Clock |

||

Q |

2 |

|

|

|

|

15 |

|||

|

|

|

|

|

|

|

|

|

|

|

Q |

|

3 |

|

|

|

|

14 |

VBB |

|

|

|

|

|

|

|

|

|

|

( ± ) |

4 |

|

|

|

|

13 |

E1 MECL |

||

|

|

|

|

|

|

|

|

|

E2 MECL |

( + ) |

|

5 |

|

|

|

|

12 |

||

|

|

|

|

|

|

|

|

|

E3 MECL |

MTTL VCC |

6 |

|

|

|

|

11 |

|||

|

|

|

|

|

|

|

|

|

E4 MECL |

MTTL Output |

7 |

|

|

|

|

10 |

|||

|

|

|

|

|

|

|

|

|

|

VEE |

8 |

|

|

|

|

9 |

E5 MECL |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Top View) |

|

||||

ORDERING INFORMATION

|

|

Operating |

|

Device |

Temperature Range |

Package |

|

|

|

|

|

MC12009P |

|

|

|

|

|

TA = ± 35° to +85°C |

Plastic |

MC12011P |

|

||

MC12013P |

|

|

|

|

|

|

|

Motorola, Inc. 1997 |

Rev 2 |

MC12009 MC12011 MC12013

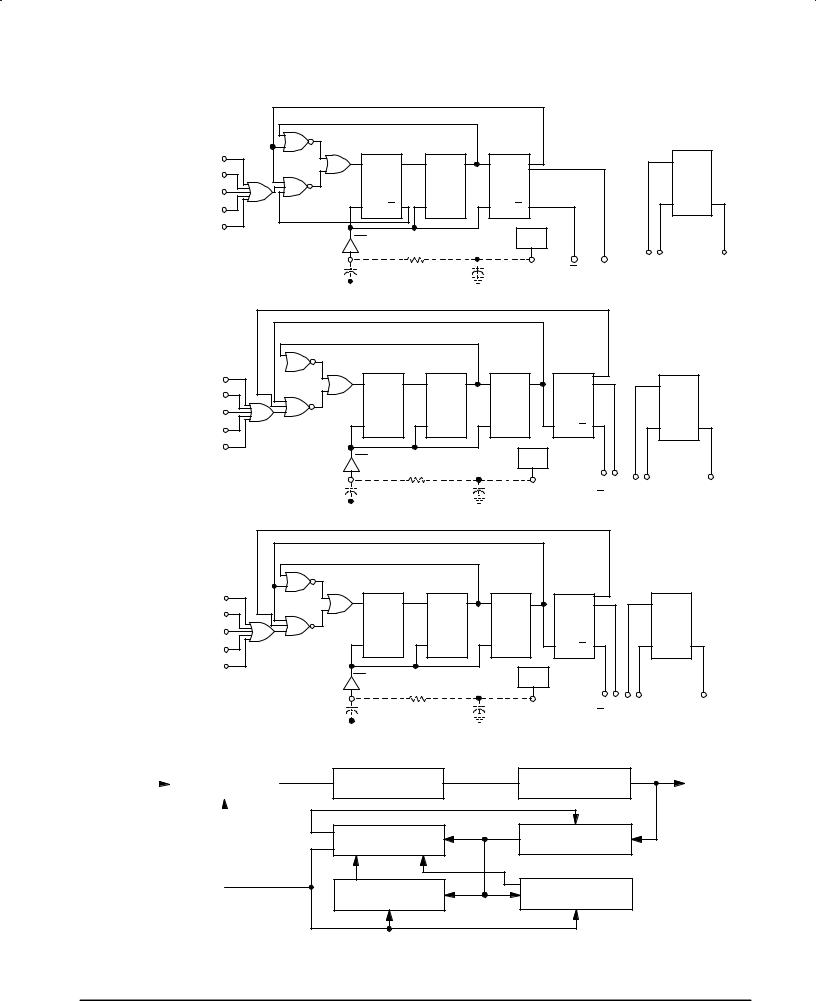

Figure 1. Logic Diagrams

MC12009

MTTL E5 9 |

D |

Q1 |

D |

Q2 |

D |

Q3 |

|

|

|

|

MECL |

MTTL E4 10 |

|

|

|

|

to |

||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

MTTL |

|

MECL E3 11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Trans± |

|

MECL E2 12 |

C |

Q1 |

C |

|

C |

Q3 |

|

|

|

|

lator |

|

|

|

|

|

|

||||||

MECL E1 13 |

Recommended Circuitry |

|

|

VBB |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||||

|

For ac coupled Inputs. |

|

|

|

|

|

|

|

7 |

||

|

15 |

|

|

|

|

14 |

3 |

2 |

5 |

4 |

|

|

|

|

|

0.1 μF |

MTTL |

||||||

|

1000 pF |

|

1 k |

|

|

Q3 |

Q3 |

+ |

± |

||

|

|

|

|

Out |

|||||||

|

Clock Input |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

MC12011 |

|

|

|

|

|

|

|

|

|

MTTL E5 |

9 |

D |

Q1 |

D |

Q2 |

D |

Q3 |

|

Q4 |

|

|

|

MECL |

MTTL E4 10 |

|

|

|

|

|

|

Toggle |

|

|

|

to |

||

|

|

|

|

|

|

|

Flip |

|

|

|

|||

MECL E3 11 |

|

|

|

|

|

|

|

|

|

|

MTTL |

||

|

|

|

|

|

|

|

Flop |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

Trans± |

|||

|

|

C |

|

C |

|

C |

|

C |

Q4 |

|

|

|

|

MECL E2 12 |

|

|

|

|

|

|

lator |

||||||

|

|

|

|

|

|

|

|

|

|

||||

MECL E1 13 |

Recommended Circuitry |

|

|

VBB |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||||

|

|

For ac coupled Inputs. |

|

|

|

|

|

|

|

|

7 |

||

|

|

15 |

|

|

|

|

14 |

|

3 |

2 |

5 |

4 |

|

|

|

1000 pF |

1 k |

|

0.1 μF |

|

|

MTTL |

|||||

|

|

|

|

|

Q4 Q4 |

||||||||

|

|

Clock Input |

|

|

|

|

|

+ |

± |

Out |

|||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

MC12013 |

|

|

|

|

|

|

|

|

|

|

10 for one or all |

|

|

|

|

|

|

|

|

|

|

|

|

|

E1 thru E5 high |

|

|

|

|

|

|

|

|

|

|

|

|

|

11 for all |

|

|

|

|

|

|

|

|

|

|

|

|

|

E1 thru E5 low |

|

|

|

|

|

|

|

|

|

|

|

|

|

Tie unused gate inputs low. |

|

|

|

|

|

|

|

|

|

|

|

|

|

MTTL E5 |

9 |

D |

Q1 |

D |

Q2 |

D |

Q3 |

|

Q4 |

|

|

|

MECL |

|

|

|

|

|

|

||||||||

MTTL E4 10 |

|

|

|

|

|

|

|

Toggle |

|

|

|

to |

|

MECL E3 11 |

|

|

|

|

|

|

|

Flip |

|

|

|

MTTL |

|

|

|

|

|

|

|

|

Flop |

|

|

|

Trans± |

||

|

|

C |

|

C |

|

C |

|

C |

|

|

|

||

MECL E2 12 |

|

|

|

Q4 |

|

|

|

lator |

|||||

MECL E1 13 |

Recommended Circuitry |

|

VBB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Pull±down resistors required on |

For ac coupled Inputs. |

|

|

|

|

|

|

7 |

|

15 |

|

|

14 |

|

|

|

|

||

Pins 2, 3 when not connected |

|

|

3 |

2 |

5 |

4 |

|||

|

0.1 μF |

MTTL |

|||||||

1000 pF |

1 k |

|

|||||||

to translator. |

Clock Input |

|

|

|

Q4 Q4 |

+ |

± |

Out |

|

Basic IC Capability: 10/11 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

Figure 2. Typical Frequency Synthesizer Application

fref |

|

Phase Detector |

|

|

MC4044 |

||

|

|

||

|

|

|

|

|

|

|

|

Low±Pass Filter |

Voltage±Controlled |

fout |

|

Oscillator MC1648 |

|||

|

|

||

Modulus Enable Line |

|

|

|

Counter Control Logic |

MC12009 |

|

|

MC12011 |

|

||

MC12014 |

|

||

MC12013 |

|

||

|

Zero Detect Line |

|

|

fout |

|

|

|

BNp Programmable |

BA Programmable |

|

|

Counter MC4016 |

Counter MC4016 |

|

|

Counter Reset Line |

|

|

2 |

MOTOROLA RF/IF DEVICE DATA |

MC12009 MC12011 MC12013

ELECTRICAL CHARACTERISTICS (Supply Voltage = ±5.2 V, unless otherwise noted.)

|

|

|

|

|

Test Limits |

|

|

|

|

|

|

Pin |

|

|

|

|

|

|

|

|

|

±30°C |

+25°C |

+85°C |

|

||||

|

|

Under |

|

||||||

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Test |

Min |

Max |

Min |

Max |

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

Power Supply Drain Current |

ICC1 |

8 |

±88 |

|

±80 |

|

±80 |

|

mAdc |

|

ICC2 |

6 |

|

5.2 |

|

5.2 |

|

5.2 |

mAdc |

Input Current |

IinH1 |

15 |

|

375 |

|

250 |

|

250 |

μAdc |

|

|

11 |

|

375 |

|

250 |

|

250 |

|

|

|

12 |

|

375 |

|

250 |

|

250 |

|

|

|

13 |

|

375 |

|

250 |

|

250 |

|

|

|

|

|

|

|

|

|

|

|

|

IinH2 |

4 |

1.7 |

6.0 |

2.0 |

6.0 |

2.0 |

6.4 |

mAdc |

|

|

5 |

1.7 |

6.0 |

2.0 |

6.0 |

2.0 |

6.4 |

|

|

|

|

|

|

|

|

|

|

|

|

IinH3 |

5 |

0.7 |

3.0 |

1.0 |

3.0 |

1.0 |

3.6 |

|

|

IinH4 |

9 |

|

100 |

|

100 |

|

100 |

μAdc |

|

|

10 |

|

100 |

|

100 |

|

100 |

|

|

|

|

|

|

|

|

|

|

|

Leakage Current |

IinL1 |

15 |

±10 |

|

±10 |

|

±10 |

|

μAdc |

|

|

11 |

±10 |

|

±10 |

|

±10 |

|

|

|

|

12 |

±10 |

|

±10 |

|

±10 |

|

|

|

|

13 |

±10 |

|

±10 |

|

±10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

IinL2 |

9 |

±1.6 |

|

±1.6 |

|

±1.6 |

|

mAdc |

|

|

10 |

±1.6 |

|

±1.6 |

|

±1.6 |

|

|

|

|

|

|

|

|

|

|

|

|

Reference Voltage |

VBB |

14 |

|

|

±1.360 |

±1.160 |

|

|

Vdc |

Logic `1' Output Voltage |

VOH1 |

2 |

±1.100 |

±0.890 |

±1.000 |

±0.810 |

±0.930 |

±0.700 |

Vdc |

|

(Note 1) |

3 |

±1.100 |

±0.890 |

±1.000 |

±0.810 |

±0.930 |

±0.700 |

|

|

|

|

|

|

|

|

|

|

|

|

VOH2 |

7 |

±2.8 |

|

±2.6 |

|

±2.4 |

|

|

Logic `0' Output Voltage |

VOL1 |

2 |

±1.990 |

±1.675 |

±1.950 |

±1.650 |

±1.925 |

±1.615 |

Vdc |

|

(Note 1) |

3 |

±1.990 |

±1.675 |

±1.950 |

±1.650 |

±1.925 |

±1.615 |

|

|

|

|

|

|

|

|

|

|

|

|

VOL2 |

7 |

|

±4.26 |

|

±4.40 |

|

±4.48 |

|

Logic `1' Threshold Voltage |

VOHA |

2 |

±1.120 |

|

±1.020 |

|

±0.950 |

|

Vdc |

|

(Note 2) |

3 |

±1.120 |

|

±1.020 |

|

±0.950 |

|

|

|

|

|

|

|

|

|

|

|

|

Logic `0' Threshold Voltage |

VOLA |

2 |

|

±1.655 |

|

±1.630 |

|

±1.595 |

Vdc |

|

(Note 3) |

3 |

|

±1.655 |

|

±1.630 |

|

±1.595 |

|

|

|

|

|

|

|

|

|

|

|

Short Circuit Current |

IOS |

7 |

±65 |

±20 |

±65 |

±20 |

±65 |

±20 |

mAdc |

1. Test outputs of the device must be tested by sequencing through the truth table. All input, power supply and |

Clock Input |

||||

ground voltages must be maintained between tests. The clock input is the waveform shown. |

|||||

|

|

|

|

||

|

|

|

|

||

2.In addition to meeting the output levels specified, the device must divide by 5, 8 or 10 during this test. The clock input is the waveform shown.

3.In addition to meeting the output levels specified, the device must divide by 6, 9 or 11 during this test. The clock input is the waveform shown.

VIHmax

VILmin

Each MECL 10,000 series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50 Ω resistor to ±2.0 V. Test procedures are shown for only one gate. The other gates are tested in the same manner.

MOTOROLA RF/IF DEVICE DATA |

3 |

|

MC12009 MC12011 MC12013

ELECTRICAL CHARACTERISTICS (Supply Voltage = ±5.2 V, unless otherwise noted.) (continued)

|

|

|

|

|

TEST VOLTAGE/CURRENT VALUES |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Volts |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

@ Test Temperature |

VIHmax |

VILmin |

VIHAmin |

|

VILAmax |

VIH |

|

VILH |

|

||

|

|

|

±30°C |

±0.890 |

±1.990 |

±1.205 |

|

±1.500 |

±2.8 |

|

±4.7 |

|

|

|

|

+25°C |

|

|

|

|

|

|

|

|

|

|

|

|

±0.810 |

±1.950 |

±1.105 |

|

±1.475 |

±2.8 |

|

±4.7 |

|

|

|

|

|

+85°C |

|

|

|

|

|

|

|

|

|

|

|

|

±0.700 |

±1.925 |

±1.035 |

|

±1.440 |

±2.8 |

|

±4.7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin |

TEST VOLTAGE APPLIED TO PINS LISTED BELOW |

|

|

||||||

Characteristic |

|

Symbol |

Under |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Test |

VIHmax |

VILmin |

VIHAmin |

|

VILAmax |

VIH |

|

VIL |

Gnd |

||

Power Supply Drain Current |

|

ICC1 |

8 |

|

|

|

|

|

|

|

|

1,16 |

|

|

ICC2 |

6 |

4 |

5 |

|

|

|

|

|

|

6 |

Input Current |

|

IinH1 |

15 |

15 |

|

|

|

|

|

|

|

1,16 |

|

|

|

11 |

11 |

|

|

|

|

|

|

|

1,16 |

|

|

|

12 |

12 |

|

|

|

|

|

|

|

1,16 |

|

|

|

13 |

13 |

|

|

|

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IinH2 |

4 |

5 |

4 |

|

|

|

|

|

|

6 |

|

|

|

5 |

5 |

4 |

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IinH3 |

5 |

4 |

5 |

|

|

|

|

|

|

6 |

|

|

IinH4 |

9 |

|

|

|

|

|

9 |

|

|

1,16 |

|

|

|

10 |

|

|

|

|

|

10 |

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Leakage Current |

|

IinL1 |

15 |

|

|

|

|

|

|

|

|

1,16 |

|

|

|

11 |

|

|

|

|

|

|

|

|

1,16 |

|

|

|

12 |

|

|

|

|

|

|

|

|

1,16 |

|

|

|

13 |

|

|

|

|

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IinL2 |

9 |

|

|

|

|

|

|

|

9 |

1,16 |

|

|

|

10 |

|

|

|

|

|

|

|

10 |

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Reference Voltage |

|

VBB |

14 |

|

|

|

|

|

|

|

|

1,16 |

Logic `1' Output Voltage |

|

VOH1 |

2 |

|

11,12,13 |

|

|

|

|

|

9,10 |

1,16 |

|

|

(Note 1.) |

3 |

|

11,12,13 |

|

|

|

|

|

9,10 |

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOH2 |

7 |

5 |

4 |

|

|

|

|

|

|

6 |

Logic `0' Output Voltage |

|

VOL1 |

2 |

|

11,12,13 |

|

|

|

|

|

9,10 |

1,16 |

|

|

(Note 1.) |

3 |

|

11,12,13 |

|

|

|

|

|

9,10 |

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOL2 |

7 |

4 |

5 |

|

|

|

|

|

|

6 |

Logic `1' Threshold Voltage |

|

VOHA |

2 |

|

|

11,12,13 |

|

|

|

|

|

1,16 |

|

|

(Note 2.) |

3 |

|

|

11,12,13 |

|

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Logic `0' Threshold Voltage |

|

VOLA |

2 |

|

|

|

|

11,12,13 |

|

|

|

1,16 |

|

|

(Note 3.) |

3 |

|

|

|

|

11,12,13 |

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Short Circuit Current |

|

IOS |

7 |

5 |

4 |

|

|

|

|

|

7 |

6 |

1. Test outputs of the device must be tested by sequencing through the truth table. All input, power supply and |

Clock Input |

||||

ground voltages must be maintained between tests. The clock input is the waveform shown. |

|||||

|

|

|

|

||

|

|

|

|

||

2.In addition to meeting the output levels specified, the device must divide by 5, 8 or 10 during this test. The clock input is the waveform shown.

3.In addition to meeting the output levels specified, the device must divide by 6, 9 or 11 during this test. The clock input is the waveform shown.

VIHmax

VILmin

4 |

MOTOROLA RF/IF DEVICE DATA |

MC12009 MC12011 MC12013

ELECTRICAL CHARACTERISTICS (Supply Voltage = ±5.2 V, unless otherwise noted.) (continued)

|

|

|

|

|

|

TEST VOLTAGE/CURRENT VALUES |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Volts |

|

|

mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

@ Test Temperature |

VIHT |

|

VILT |

VEE |

IL |

IOL |

|

IOH |

|

||

|

|

|

±30°C |

±3.2 |

|

±4.4 |

±5.2 |

±0.25 |

16 |

|

±0.40 |

|

|

|

|

+25°C |

|

|

|

|

|

|

|

|

|

|

|

|

±3.2 |

|

±4.4 |

±5.2 |

±0.25 |

16 |

|

±0.40 |

|

|

|

|

|

+85°C |

|

|

|

|

|

|

|

|

|

|

|

|

±3.2 |

|

±4.4 |

±5.2 |

±0.25 |

16 |

|

±0.40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin |

|

TEST VOLTAGE APPLIED TO PINS LISTED BELOW |

|

|

|||||

Characteristic |

|

Symbol |

Under |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Test |

VIHT |

|

VILT |

VEE |

IL |

IOL |

|

IOH |

Gnd |

||

Power Supply Drain Current |

|

ICC1 |

8 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

ICC2 |

6 |

|

|

|

8 |

|

|

|

|

6 |

Input Current |

|

IinH1 |

15 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

|

11 |

9,10 |

|

|

8 |

|

|

|

|

1,16 |

|

|

|

12 |

9,10 |

|

|

8 |

|

|

|

|

1,16 |

|

|

|

13 |

9,10 |

|

|

8 |

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IinH2 |

4 |

|

|

|

8 |

|

|

|

|

6 |

|

|

|

5 |

|

|

|

8 |

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IinH3 |

5 |

|

|

|

8 |

|

|

|

|

6 |

|

|

IinH4 |

9 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

|

10 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Leakage Current |

|

IinL1 |

15 |

|

|

|

8,15 |

|

|

|

|

1,16 |

|

|

|

11 |

|

|

|

8,11 |

|

|

|

|

1,16 |

|

|

|

12 |

|

|

|

8,12 |

|

|

|

|

1,16 |

|

|

|

13 |

|

|

|

8,13 |

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IinL2 |

9 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

|

10 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Reference Voltage |

|

VBB |

14 |

|

|

|

8 |

14 |

|

|

|

1,16 |

Logic `1' Output Voltage |

|

VOH1 |

2 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

(Note 1.) |

3 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOH2 |

7 |

|

|

|

8 |

|

|

|

7 |

6 |

Logic `0' Output Voltage |

|

VOL1 |

2 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

(Note 1.) |

3 |

|

|

|

8 |

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOL2 |

7 |

|

|

|

8 |

|

7 |

|

|

6 |

Logic `1' Threshold Voltage |

|

VOHA |

2 |

9,10 |

|

|

8 |

|

|

|

|

1,16 |

|

|

(Note 2.) |

3 |

9,10 |

|

|

8 |

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Logic `0' Threshold Voltage |

|

VOLA |

2 |

|

|

9,10 |

8 |

|

|

|

|

1,16 |

|

|

(Note 3.) |

3 |

|

|

9,10 |

8 |

|

|

|

|

1,16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Short Circuit Current |

|

IOS |

7 |

|

|

|

8 |

|

|

|

|

6 |

1. Test outputs of the device must be tested by sequencing through the truth table. All input, power supply and |

Clock Input |

||||

ground voltages must be maintained between tests. The clock input is the waveform shown. |

|||||

|

|

|

|

||

|

|

|

|

||

2.In addition to meeting the output levels specified, the device must divide by 5, 8 or 10 during this test. The clock input is the waveform shown.

3.In addition to meeting the output levels specified, the device must divide by 6, 9 or 11 during this test. The clock input is the waveform shown.

VIHmax

VILmin

MOTOROLA RF/IF DEVICE DATA |

5 |

|

Loading...

Loading...