Motorola MC74F568DW, MC74F568N, MC74F569DW, MC74F569N, MC54F568J Datasheet

...

4-BIT BIDIRECTIONAL COUNTERS (WITH 3-STATE OUTPUTS)

The MC54/74F568 and MC54/74F569 are fully synchronous, reversible counters with 3-state outputs. The F568 is a BCD decade counter; the F569 is a binary counter. They feature preset capability for programmable opera-

tion, carry lookahead for easy cascading, and a U/D input to control the direction of counting. For maximum flexibility there are both synchronous and mas-

ter asynchronous reset inputs as well as both Clocked Carry (CC) and Terminal Count (TC) outputs. All state changes except Master Reset are initiated by the rising edge of the clock. A HIGH signal on the Output Enable (OE) input forces the output buffers into the high impedance state but does not prevent counting, resetting or parallel loading.

•4-Bit Bidirectional Counting

F568 Decade Counter

F569 Binary Counter

•Synchronous Counting and Loading

•Lookahead Carry Capability for Easy Cascading

•Preset Capability for Programmable Operation

•3-State Outputs for Bus Organized Systems

•Master Reset (MR) Overrides All Other Inputs

•Synchronous Reset (SR) Overrides Counting and Parallel Loading

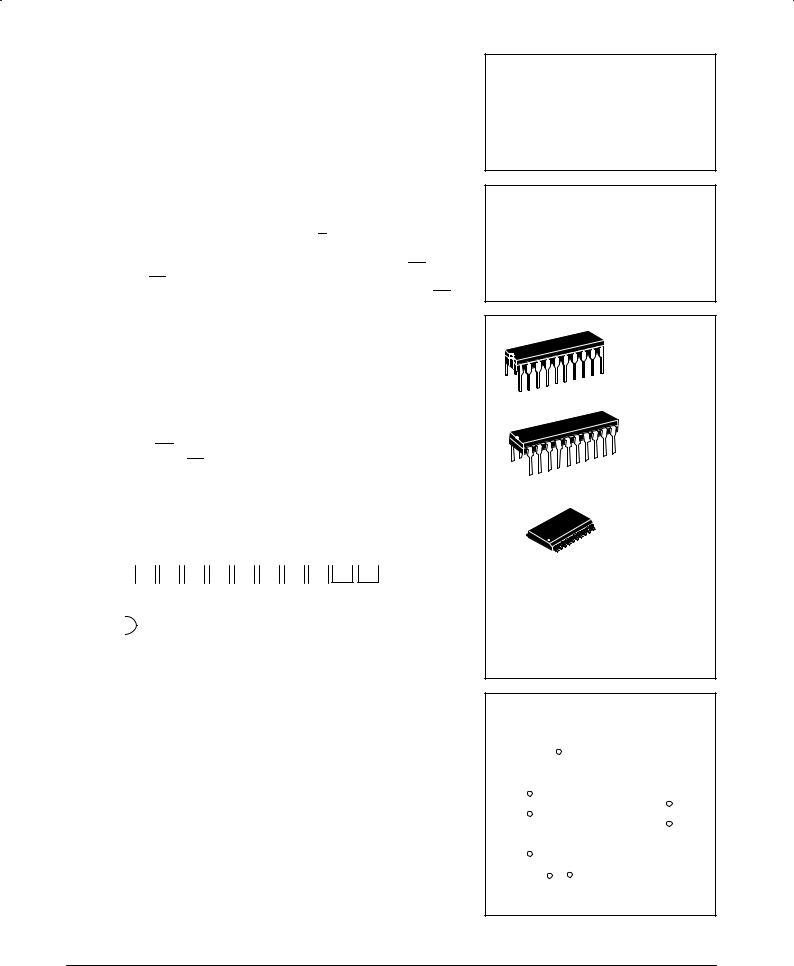

CONNECTION DIAGRAM

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

TC |

|

CC |

|

OE |

|

O0 |

|

O1 |

|

O2 |

|

O3 |

|

CET |

|

|

PE |

|||||||

20 |

19 |

|

|

18 |

|

17 |

|

16 |

15 |

14 |

13 |

12 |

|

11 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

|

9 |

|

|

10 |

|

|||

|

|

|

|

|

|

|

P0 |

|

P1 |

|

P2 |

P3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U/D |

|

|

CP |

|

|

|

|

CEP |

|

MR |

|

|

SR |

GND |

|

||||||||||

MC54/74F568

MC54/74F569

4-BIT

BIDIRECTIONAL

COUNTERS

(WITH 3-STATE OUTPUTS)

FAST SCHOTTKY TTL

|

J SUFFIX |

|

|

CERAMIC |

|

20 |

CASE 732-03 |

|

|

||

1 |

|

|

|

N SUFFIX |

|

|

PLASTIC |

|

20 |

CASE 738-03 |

|

|

||

1 |

|

|

|

DW SUFFIX |

|

20 |

SOIC |

|

CASE 751D-03 |

||

|

||

|

1 |

ORDERING INFORMATION

MC54FXXXJ Ceramic

MC74FXXXN Plastic

MC74FXXXDW SOIC

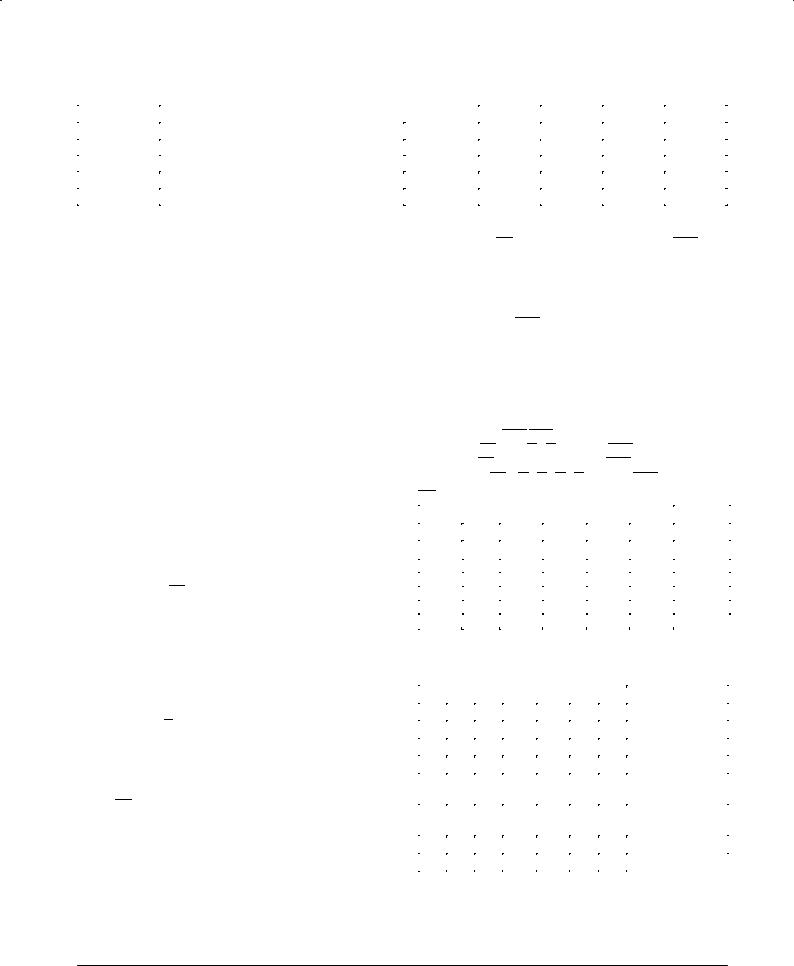

LOGIC SYMBOL

|

|

11 |

|

3 |

|

4 |

|

5 |

|

6 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

PE |

P0 |

P1 |

P2 |

P3 |

|

|

||||||||||

|

U/D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

7 |

|

CEP |

|

|

|

|

|

|

|

|

|

|

|

|

CC |

|

18 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

12 |

|

CET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

TC |

|

19 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

2 |

|

CP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

17 |

|

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

MR |

SR O0 O1 O2 O3 |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

8 |

|

9 |

16 |

15 |

14 |

13 |

|

|

||||||||||

FAST AND LS TTL DATA

4-220

MC54/74F568 •MC54/74F569

Symbol |

Parameter |

|

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

VCC |

Supply Voltage |

54, 74 |

4.5 |

5.0 |

5.5 |

V |

|

TA |

Operating Ambient Temperature Range |

54 |

± 55 |

25 |

125 |

°C |

|

|

|

|

|

||||

74 |

0 |

25 |

70 |

||||

|

|

|

|||||

|

|

|

|

|

|

|

|

IOH |

Output Current Ð High |

54, 74 |

|

|

± 3.0 |

mA |

|

IOL |

Output Current Ð Low |

54, 74 |

|

|

24 |

mA |

FUNCTIONAL DESCRIPTION

The F568 counts modulo-10 in the BCD (8421) sequence. From state 9 (HLLH) it will increment to 0 (LLLL) in the Up mode; in Down mode it will decrement from 0 to 9.The F569 counts in the modulo-16 binary sequence. From state 15 it will increment to state 0 in the Up mode; in the Down mode it will decrement from 0 to 15. The clock inputs of all flip-flops are driven in parallel through a clock buffer. All state changes (except due to Master Reset) occur synchronously with the LOW- to-HIGH transition of the Clock Pulse (CP) input signal.

The circuits have five fundamental modes of operation, in order of precedence: asynchronous reset, synchronous reset, parallel load, count and hold. Five control inputs Ð Master Re - set (MR), Synchronous Reset (SR), Parallel Enable (PE), Count Enable Parallel (CEP) and Count Enable Trickle (CET) Ð plus the Up/Down (U/D ) input, determine the mode of op- eration, as shown in the Mode Select Table. A LOW signal on MR overrides all other inputs and asynchronously forces the flip-flop Q outputs LOW. A LOW signal on SR overrides counting and parallel loading and allows the Q outputs to go LOW on the next rising edge of CP. A LOW signal on PE overrides counting and allows information on the Parallel Data (Pn) inputs to be loaded into the flip-flops on the next rising edge of CP. With MR, SR and PE HIGH, CEP and CET permit counting when both are LOW. Conversely, a HIGH signal on either CEP or CET inhibits counting.

The F568 and F569 use edge-triggered flip-flops and changing the SR, PE, CEP , CET or U/D inputs when the CP is in either state does not cause errors, provided that the recommended setup and hold times, with respect to the rising edge of CP, are observed.

Two types of outputs are provided as overflow/underflow indicators. The Terminal Count (TC) output is normally HIGH and goes LOW providing CET is LOW, when the counter reaches zero in the Down mode, or reaches maximum (9 for the F568,15 for the F569) in the Up mode. TC will then remain LOW until a state change occurs, whether by counting or presetting, or until U/D or CET is changed. To implement synchro- nous multistage counters, the connections between the TC output and the CEP and CET inputs can provide either slow or fast carry propagation. Figure A shows the connections for simple ripple carry, in which the clock period must be longer than the CP to TC delay of the first stage, plus the cumulative CET to TC delays of the intermediate stages, plus the CET to CP setup time of the last stage. This total delay plus setup time sets the upper limit on clock frequency. For faster clock rates, the carry lookahead connections shown in Figure B are recommended. In this scheme the ripple delay through the intermediate stages commences with the same clock that causes the first stage to tick over from max to min in the Up mode, or min to max in the Down mode, to start its final cycle. Since this final cycle takes 10 (F568) or 16 (F569) clocks to complete, there is plenty of time for the ripple to progress through the intermediate stages. The critical timing that limits the clock peri-

od is the CP to TC delay of the first stage plus the CEP to CP setup time of the last stage. The TC output is subject to decoding spikes due to internal race conditions and is therefore not recommended for use as a clock or asynchronous reset for flip-flops, registers or counters. For such applications, the Clocked Carry (CC) output is provided. The CC output is normally HIGH. When CEP, CET, and TC are LOW, the CC output will go LOW when the clock next goes LOW and will stay LOW until the clock goes HIGH again, as shown in the CC Truth Table. When the Output Enable (OE) is LOW, the parallel data outputs O0±O3 are active and follow the flip-flop Q outputs. A HIGH signal on OE forces O0±O3 to the High Z state but does not prevent counting, loading or resetting.

LOGIC EQUATIONS:

Count Enable = CEP CET PE

Up ('F568): TC = Q0 Q1 Q2 Q3 (Up) CET

('F569): TC = Q0 Q1 Q2 Q3 (Up) CET

Down (Both): TC = Q0 Q1 Q2 Q3 (Down) CET

CC TRUTH TABLE

|

|

|

|

|

|

|

Inputs |

|

|

|

|

|

|

|

|

Output |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CP |

|

|

|

|

|

|

|||

|

SR |

PE |

CEP |

CET |

TC* |

CC |

|||||||||||||||||||

|

L |

|

X |

|

X |

|

X |

|

X |

|

|

X |

|

|

|

H |

|||||||||

|

X |

|

L |

|

X |

|

X |

|

X |

|

|

X |

|

|

|

H |

|||||||||

|

X |

|

X |

|

H |

|

X |

|

X |

|

|

X |

|

|

|

H |

|||||||||

|

X |

|

X |

|

X |

|

H |

|

X |

|

|

X |

|

|

|

H |

|||||||||

|

X |

|

X |

|

X |

|

X |

|

H |

|

|

X |

|

|

|

H |

|||||||||

|

H |

|

H |

|

L |

|

L |

|

L |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

* = TC is generated internally |

|

|

|

|

|

|

X = Don't Care |

|||||||||||||||

L = LOW Voltage Level |

|

|

|

|

|

|

|

|

|

= Low Pulse |

||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||

H = HIGH Voltage Level |

|

|

|

|

|

|

|

|

|

|

||||||||||||

FUNCTION TABLE |

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Inputs |

|

|

|

|

|

|

|

|

|

Operating Mode |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

|

|

SR |

|

|

PE |

|

|

CEP |

|

|

CET |

|

U/D |

|

|

CP |

|

|

||

|

L |

|

X |

|

|

X |

|

X |

|

X |

X |

|

X |

Asynchronous reset |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

h |

|

l |

|

|

X |

|

X |

|

X |

X |

|

↑ |

Synchronous reset |

||||||||

|

h |

|

h |

|

|

l |

|

X |

|

X |

X |

|

↑ |

Parallel load |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

h |

|

h |

|

|

h |

|

l |

|

l |

h |

|

↑ |

Count up |

||||||||

|

|

|

|

|

|

|

(increment) |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

h |

|

h |

|

|

h |

|

l |

|

l |

l |

|

↑ |

Count down |

||||||||

|

|

|

|

|

|

|

(decrement) |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

h |

|

H |

|

|

H |

|

H |

|

X |

X |

|

X |

Hold (do nothing) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

h |

|

H |

|

|

H |

|

X |

|

H |

X |

|

X |

|||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H = HIGH voltage level

h = HIGH voltage level one setup prior to the Low-to-High Clock transition L = LOW voltage level

l = LOW voltage level one setup prior to the Low-to-High clock transition X = Don't care

↑ = Low-to-High clock transition

FAST AND LS TTL DATA

4-221

Loading...

Loading...