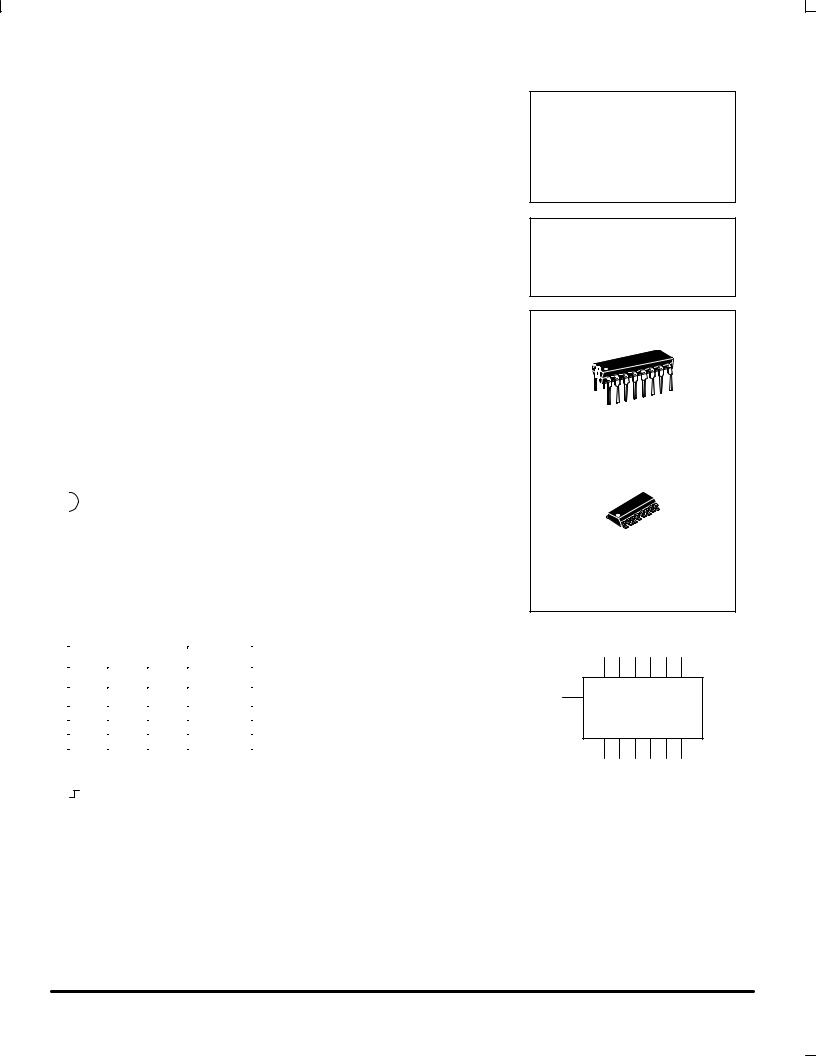

Motorola MC74ACT174N, MC74ACT174D, MC74AC174D, MC74AC174N Datasheet

Hex D Flip Flop with Master Reset

The MC74AC174/74ACT174 is a high-speed hex D flip-flop. The device is used primarily as a 6-bit edge-triggered storage register. The information on the D inputs is transferred to storage during the LOW-to-HIGH clock transition. The device has a Master Reset to simultaneously clear all flip-flops.

•Outputs Source/Sink 24 mA

•′ACT174 Has TTL Compatible Inputs

VCC |

Q5 |

|

D5 |

|

D4 |

|

Q4 |

|

D3 |

Q3 |

|

CP |

|

|

||||

|

16 |

|

15 |

|

14 |

|

13 |

|

12 |

|

11 |

|

10 |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN NAMES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0±D5 |

Data Inputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CP |

Clock Pulse Input |

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

MR |

Master Reset Input |

|

MR |

Q0 |

|

D0 |

|

D1 |

|

Q1 |

|

D2 |

Q2 |

GND |

Q0±Q5 |

Outputs |

||||

TRUTH TABLE

|

|

Inputs |

|

Output |

|||

|

|

|

|

|

|

|

|

MR |

CP |

D |

Q |

||||

|

|

|

|

|

|

|

|

|

L |

|

X |

X |

L |

||

|

H |

|

|

|

|

H |

H |

|

|

|

|

|

|||

|

H |

|

|

|

|

L |

L |

|

|

|

|

|

|||

|

H |

|

L |

X |

Q |

||

|

|

|

|

|

|

|

|

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

= LOW-to-HIGH Transition of Clock

MC74AC174

MC74ACT174

HEX D FLIP-FLOP

WITH MASTER RESET

N SUFFIX

CASE 648-08

PLASTIC

D SUFFIX

CASE 751B-05

PLASTIC

LOGIC SYMBOL

CPD0 D1 D2 D3 D4 D5

MR

MR

Q0 Q1 Q2 Q3 Q4 Q5

FACT DATA

5-1

MC74AC174 MC74ACT174

FUNCTIONAL DESCRIPTION

The MC74AC174/74ACT174 consists of six edge-triggered D flip-flops with individual D inputs and Q outputs. The Clock (CP) and Master Reset (MR) are common to all flip-flops. Each D input's state is transferred to the corresponding flip-flop's output following the LOW-to-HIGH Clock (CP) transition. A

LOW input to the Master Reset (MR) will force all outputs LOW independent of Clock or Data inputs. The MC74AC174/ 74ACT174 is useful for applications where the true output only is required and the Clock and Master Reset are common to all storage elements.

|

|

LOGIC DIAGRAM |

|

|

|

|

MR CP D5 |

D4 |

D3 |

D2 |

D1 |

|

D0 |

D Q |

D Q |

|

D Q |

D Q |

D Q |

D Q |

CP |

CP |

|

CP |

CP |

CP |

CP |

CD |

CD |

|

CD |

CD |

CD |

CD |

Q5 |

Q4 |

|

Q3 |

Q2 |

Q1 |

Q0 |

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

MAXIMUM RATINGS*

Symbol |

Parameter |

Value |

Unit |

|

|

|

|

VCC |

DC Supply Voltage (Referenced to GND) |

±0.5 to +7.0 |

V |

Vin |

DC Input Voltage (Referenced to GND) |

±0.5 to VCC +0.5 |

V |

Vout |

DC Output Voltage (Referenced to GND) |

±0.5 to VCC +0.5 |

V |

Iin |

DC Input Current, per Pin |

±20 |

mA |

Iout |

DC Output Sink/Source Current, per Pin |

±50 |

mA |

ICC |

DC VCC or GND Current per Output Pin |

±50 |

mA |

Tstg |

Storage Temperature |

±65 to +150 |

°C |

*Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

FACT DATA

5-2

MC74AC174 MC74ACT174

RECOMMENDED OPERATING CONDITIONS

Symbol |

Parameter |

|

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

VCC |

Supply Voltage |

′AC |

2.0 |

5.0 |

6.0 |

V |

|

|

|

|

|

||||

′ACT |

4.5 |

5.0 |

5.5 |

||||

|

|

|

|||||

|

|

|

|

|

|

|

|

Vin, Vout |

DC Input Voltage, Output Voltage (Ref. to GND) |

|

0 |

|

VCC |

V |

|

|

Input Rise and Fall Time (Note 1) |

VCC @ 3.0 V |

|

150 |

|

|

|

tr, tf |

VCC @ 4.5 V |

|

40 |

|

ns/V |

||

′AC Devices except Schmitt Inputs |

|

|

|||||

|

|

VCC @ 5.5 V |

|

25 |

|

|

|

tr, tf |

Input Rise and Fall Time (Note 2) |

VCC @ 4.5 V |

|

10 |

|

ns/V |

|

′ACT Devices except Schmitt Inputs |

VCC @ 5.5 V |

|

8.0 |

|

|||

|

|

|

|

|

|||

TJ |

Junction Temperature (PDIP) |

|

|

|

140 |

°C |

|

TA |

Operating Ambient Temperature Range |

|

±40 |

25 |

85 |

°C |

|

IOH |

Output Current Ð High |

|

|

|

±24 |

mA |

|

IOL |

Output Current Ð Low |

|

|

|

24 |

mA |

1.Vin from 30% to 70% VCC; see individual Data Sheets for devices that differ from the typical input rise and fall times.

2.Vin from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.

DC CHARACTERISTICS

|

|

|

74AC |

74AC |

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Parameter |

VCC |

TA = +25°C |

TA = |

Unit |

|

Conditions |

|

(V) |

±40°C to +85°C |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

Typ |

Guaranteed Limits |

|

|

|

|

|

|

|

|

|

|

|

|

|

VIH |

Minimum High Level |

3.0 |

1.5 |

2.1 |

2.1 |

|

VOUT = 0.1 V |

|

|

Input Voltage |

4.5 |

2.25 |

3.15 |

3.15 |

V |

or VCC ± 0.1 V |

|

|

|

5.5 |

2.75 |

3.85 |

3.85 |

|

|

|

|

|

|

|

|

|

|

|

|

VIL |

Maximum Low Level |

3.0 |

1.5 |

0.9 |

0.9 |

|

VOUT = 0.1 V |

|

|

Input Voltage |

4.5 |

2.25 |

1.35 |

1.35 |

V |

or VCC ± 0.1 V |

|

|

|

5.5 |

2.75 |

1.65 |

1.65 |

|

|

|

|

|

|

|

|

|

|

|

|

VOH |

Minimum High Level |

3.0 |

2.99 |

2.9 |

2.9 |

|

IOUT = ±50 mA |

|

|

Output Voltage |

4.5 |

4.49 |

4.4 |

4.4 |

V |

|

|

|

|

5.5 |

5.49 |

5.4 |

5.4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

*VIN = VIL or VIH |

|

|

|

3.0 |

|

2.56 |

2.46 |

V |

|

±12 mA |

|

|

4.5 |

|

3.86 |

3.76 |

IOH |

±24 mA |

|

|

|

|

|

|||||

|

|

5.5 |

|

4.86 |

4.76 |

|

|

±24 mA |

|

|

|

|

|

|

|

|

|

VOL |

Maximum Low Level |

3.0 |

0.002 |

0.1 |

0.1 |

|

IOUT = 50 mA |

|

|

Output Voltage |

4.5 |

0.001 |

0.1 |

0.1 |

V |

|

|

|

|

5.5 |

0.001 |

0.1 |

0.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

*VIN = VIL or VIH |

|

|

|

3.0 |

|

0.36 |

0.44 |

V |

|

12 mA |

|

|

4.5 |

|

0.36 |

0.44 |

IOL |

24 mA |

|

|

|

|

|

|||||

|

|

5.5 |

|

0.36 |

0.44 |

|

|

24 mA |

|

|

|

|

|

|

|

|

|

IIN |

Maximum Input |

|

|

± |

± |

μ |

|

|

|

Leakage Current |

5.5 |

|

0.1 |

1.0 |

A |

VI = VCC, GND |

|

IOLD |

²Minimum Dynamic |

5.5 |

|

|

75 |

mA |

VOLD = 1.65 V Max |

|

|

Output Current |

|

|

|

|

|

|

|

IOHD |

5.5 |

|

|

±75 |

mA |

VOHD = 3.85 V Min |

||

|

|

|

||||||

ICC |

Maximum Quiescent |

|

|

|

|

μ |

|

|

|

Supply Current |

5.5 |

|

8.0 |

80 |

A |

VIN = VCC or GND |

|

* All outputs loaded; thresholds on input associated with output under test. ² Maximum test duration 2.0 ms, one output loaded at a time.

Note: IIN and ICC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V VCC.

FACT DATA

5-3

Loading...

Loading...