Microchip Technology Inc 93LC76-SN, 93LC76-P, 93LC86T-I-SN, 93LC86T-I-P, 93LC86T-SN Datasheet

...

93LC76/86

8K/16K 2.5V Microwire Serial EEPROM

FEATURES

•Single supply with programming operation down to 2.5V

•Low power CMOS technology

-1 mA active current typical

-5 A standby current (typical) at 3.0V

•ORG pin selectable memory configuration 1024 x 8 or 512 x 16 bit organization (93LC76) 2048 x 8 or 1024 x 16 bit organization (93LC86)

•Self-timed ERASE and WRITE cycles (including auto-erase)

•Automatic ERAL before WRAL

•Power on/off data protection circuitry

•Industry standard 3-wire serial I/O

•Device status signal during ERASE/WRITE cycles

•Sequential READ function

•10,000,000 ERASE/WRITE cycles guaranteed

•Data retention > 200 years

•8-pin PDIP/SOIC package

•Temperature ranges available

- |

Commercial (C) |

0°C |

to |

+70°C |

- |

Industrial (I) |

-40°C |

to |

+85°C |

DESCRIPTION

The Microchip Technology Inc. 93LC76/86 are 8K and 16K low voltage serial Electrically Erasable PROMs. The device memory is configured as x8 or x16 bits depending on the ORG pin setup. Advanced CMOS technology makes these devices ideal for low power non-volatile memory applications. These devices also have a Program Enable (PE) pin to allow the user to write protect the entire contents of the memory array. The 93LC76/86 is available in standard 8-pin DIP and 8-pin surface mount SOIC packages.

PACKAGE TYPES

DIP Package

CS |

|

1 |

93LC76/86 |

8 |

|

VCC |

|

|

|||||

|

|

|||||

DO |

|

4 |

5 |

|

VSS |

|

CLK |

|

2 |

|

7 |

|

PE |

|

|

|

||||

DI |

|

3 |

|

6 |

|

ORG |

|

|

|

||||

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SOIC Package

|

|

|

1 |

93LC76/86 |

8 |

|

|

VSS |

DO |

|

|

4 |

5 |

|

|

||

CS |

|

|

2 |

|

7 |

|

|

VCC |

CLK |

|

|

|

|

|

PE |

||

|

|

3 |

|

6 |

|

|

ORG |

|

DI |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

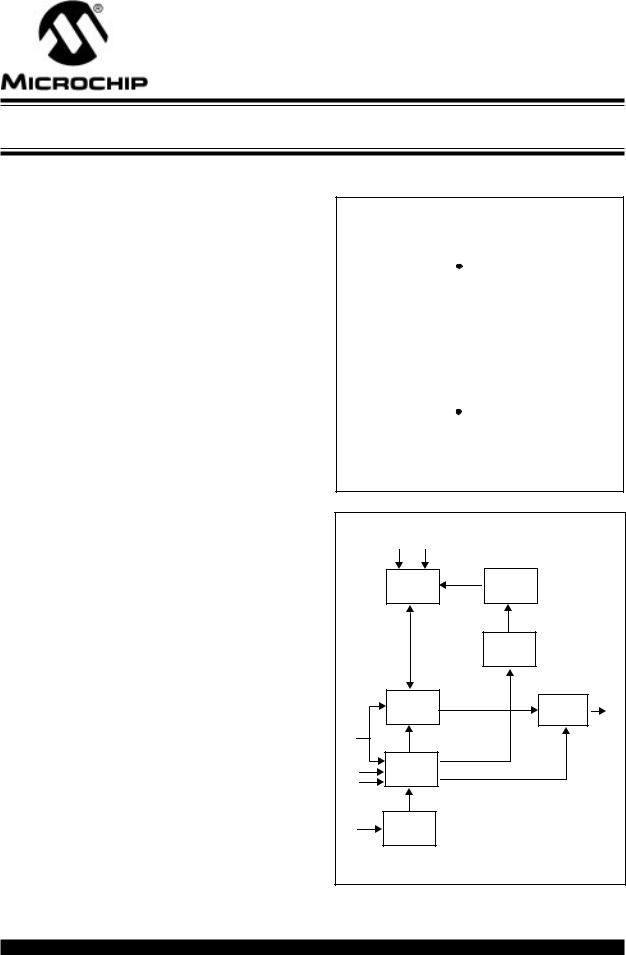

BLOCK DIAGRAM

|

VCC VSS |

|

|

|

Memory |

Address |

|

|

Array |

Decoder |

|

|

|

Address |

|

|

|

Counter |

|

|

Data |

Output |

|

|

Register |

DO |

|

|

Buffer |

||

|

|

|

|

DI |

|

|

|

|

Mode |

|

|

PE |

Decode |

|

|

Logic |

|

|

|

CS |

|

|

|

|

|

|

|

CLK |

Clock |

|

|

Generator |

|

|

|

|

|

|

Microwire is a registered trademark of National Semiconductor Incorporated.

1996 Microchip Technology Inc. |

Preliminary |

DS21131C-page 1 |

93LC76/86

1.0ELECTRICAL CHARACTERISTICS

1.1Maximum Ratings*

VCC ................................................................................... |

|

7.0V |

All inputs and outputs w.r.t. VSS ............... |

-0.6V to Vcc +1.0V |

|

Storage temperature ..................................... |

|

-65˚C to +150˚C |

Ambient temp. with power applied................. |

|

-65˚C to +125˚C |

Soldering temperature of leads (10 seconds) |

............. +300˚C |

|

ESD protection on all pins................................................ |

|

4 kV |

*Notice: Stresses above those listed under “Maximum ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability

TABLE 1-1: PIN FUNCTION TABLE

Name |

Function |

|

|

|

|

CS |

Chip Select |

CLK |

Serial Data Clock |

DI |

Serial Data Input |

DO |

Serial Data Output |

VSS |

Ground |

ORG |

Memory Configuration |

PE |

Program Enable |

VCC |

Power Supply |

|

|

TABLE 1-2: |

DC CHARACTERISTICS |

1.2AC Test Conditions

AC Waveform: |

|

VLO = 2.0V |

|

VHI = Vcc - 0.2V |

(Note 1) |

VHI = 4.0V for |

(Note 2) |

Timing Measurement Reference Level

Input |

0.5 VCC |

|

Output |

0.5 VCC |

|

Note 1: |

For VCC ≤ 4.0V |

|

2: |

For VCC > 4.0V |

|

Applicable over recommended operating ranges shown below unless otherwise noted:

VCC = +2.5V to +6.0V |

|

|

|

|

|

|

|

Commercial (C): Tamb = |

0˚C to +70˚C |

|

|

|

|

||

Industrial (I): |

Tamb = -40˚C to +85˚C |

|

|

|

|

||

Parameter |

|

|

Symbol |

Min. |

Max. |

Units |

Conditions |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

High level input voltage |

|

VIH1 |

2.0 |

VCC +1 |

V |

VCC ≥ 2.7V |

|

|

|

|

VIH2 |

0.7 VCC |

VCC +1 |

V |

VCC < 2.7V |

Low level input voltage |

|

VIL1 |

-0.3 |

0.8 |

V |

VCC ≥ 2.7V |

|

|

|

|

VIL2 |

-0.3 |

0.2 VCC |

V |

VCC < 2.7V |

Low level output voltage |

|

VOL1 |

— |

0.4 |

V |

I OL = 2.1 mA; VCC = 4.5V |

|

|

|

|

VOL2 |

— |

0.2 |

V |

I OL =100 A; VCC = VCC Min. |

High level output voltage |

|

VOH1 |

2.4 |

— |

V |

I OH = -400 A; VCC = 4.5V |

|

|

|

|

VOH2 |

VCC-0.2 |

— |

V |

I OH = -100 A; VCC = VCC Min. |

Input leakage current |

|

ILI |

-10 |

10 |

A |

VIN = 0.1V to VCC |

|

Output leakage current |

|

ILO |

-10 |

10 |

A |

VOUT = 0.1V to VCC |

|

Pin capacitance |

|

|

CINT |

— |

7 |

pF |

(Note Note:) |

(all inputs/outputs) |

|

|

|

|

|

Tamb = +25˚C, FCLK = 1 MHz |

|

Operating current |

|

ICC write |

— |

3 |

mA |

V CC = 5.5V |

|

|

|

|

ICC read |

— |

1 |

mA |

FCLK = 3 MHz; VCC = 5.5V |

|

|

|

|

|

500 |

A |

FCLK = 1 MHz; VCC = 3.0V |

Standby current |

|

|

ICCS |

— |

100 |

A |

CLK = CS = 0V; VCC = 5.5V |

|

|

|

|

|

30 |

A |

CLK = CS = 0V; VCC = 3.0V |

Note: This parameter is periodically sampled and not 100% tested.

DS21131C-page 2 |

Preliminary |

1996 Microchip Technology Inc. |

93LC76/86

TABLE 1-3: |

AC CHARACTERISTICS |

|

|

|

|

|||

|

|

|

|

|

|

|||

Applicable over recommended operating ranges shown below unless otherwise noted: |

||||||||

VCC = +2.5V to +6.0V |

|

|

|

|

|

|

|

|

Commercial (C): Tamb = |

0˚C to +70˚C |

|

|

|

|

|

||

Industrial (I): |

Tamb = -40˚C to +85˚C |

|

|

|

|

|

||

Parameter |

|

|

Symbol |

Min. |

Max. |

Units |

Conditions |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Clock frequency |

|

|

FCLK |

— |

3 |

MHz |

4.5V |

≤ VCC ≤ 6.0V |

|

|

|

|

|

2 |

MHz |

2.5V |

≤ VCC < 4.5V |

Clock high time |

|

|

TCKH |

200 |

— |

ns |

4.5V |

≤ VCC ≤ 6.0V |

|

|

|

|

300 |

|

ns |

2.5V |

≤ VCC < 4.5V |

Clock low time |

|

|

TCKL |

100 |

— |

ns |

4.5V |

≥ VCC ≤ 6.0V |

|

|

|

|

200 |

|

ns |

2.5V |

≤ VCC < 4.5V |

Chip select setup time |

|

TCSS |

50 |

— |

ns |

4.5V |

≤ VCC ≤ 6.0V, Relative to CLK |

|

|

|

|

|

100 |

|

ns |

2.5V |

≤ VCC < 4.5V, Relative to CLK |

Chip select hold time |

|

TCSH |

0 |

— |

ns |

|

|

|

Chip select low time |

|

TCSL |

250 |

— |

ns |

Relative to CLK |

||

Data input setup time |

|

TDIS |

50 |

— |

ns |

4.5V |

≤ VCC ≤ 6.0V, Relative to CLK |

|

|

|

|

|

100 |

|

ns |

2.5V |

≤ VCC <4.5V, Relative to CLK |

Data input hold time |

|

TDIH |

50 |

— |

ns |

4.5V |

≤ VCC ≤ 6.0V, Relative to CLK |

|

|

|

|

|

100 |

|

ns |

2.5V |

≤ VCC < 4.5V, Relative to CLK |

Data output delay time |

|

TPD |

— |

100 |

ns |

4.5V |

≤ VCC ≤ 6.0V, CL = 100 pF |

|

|

|

|

|

|

250 |

ns |

2.5V |

≤ VCC < 4.5V, CL = 100 pF |

Data output disable time |

|

TCZ |

— |

100 |

ns |

4.5V |

≤ VCC ≤ 6.0V |

|

|

|

|

|

|

500 |

ns |

2.5V |

≤ VCC < 4.5V (Note 1) |

Status valid time |

|

|

TSV |

— |

200 |

ns |

4.5V |

≥ VCC ≤ 6.0V, CL = 100 pF |

|

|

|

|

|

300 |

ns |

2.5V |

≤ VCC <4.5V, CL = 100 pF |

Program cycle time |

|

TWC |

— |

5 |

ms |

ERASE/WRITE mode |

||

|

|

|

TEC |

— |

15 |

ms |

ERAL mode |

|

|

|

|

TWL |

— |

30 |

ms |

WRAL mode |

|

Endurance |

|

|

— |

10M |

— |

cycles |

25 °C, Vcc = 5.0V, Block Mode |

|

|

|

|

|

|

|

|

(Note 2) |

|

Note 1: This parameter is periodically sampled and not 100% tested.

2:This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be found on our BBS or website.

1996 Microchip Technology Inc. |

Preliminary |

DS21131C-page 3 |

93LC76/86

TABLE 1-4: |

INSTRUCTION SET FOR 93LC76: ORG=1 (1X16 ORGANIZATION) |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Instruction |

SB |

Opcode |

|

|

|

|

Address |

|

|

|

|

|

Data In |

|

Data Out |

|

Req. CLK |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Cycles |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

READ |

1 |

10 |

|

X |

A8 A7 A6 A5 A4 A3 A2 A1 A0 |

|

|

|

— |

|

D15 - D0 |

|

29 |

||||||||||||

EWEN |

1 |

00 |

|

1 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

High-Z |

|

13 |

||||

ERASE |

1 |

11 |

|

X |

A8 A7 A6 A5 A4 A3 A2 A1 A0 |

|

|

|

— |

|

(RDY/BSY) |

|

13 |

||||||||||||

ERAL |

1 |

00 |

|

1 |

0 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

(RD Y/BSY) |

|

13 |

||||

WRITE |

1 |

01 |

|

X |

A8 A7 A6 A5 A4 A3 A2 A1 A0 |

|

D15 - D0 |

(RDY/BSY) |

|

29 |

|||||||||||||||

WRAL |

1 |

00 |

|

0 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

|

D15 - D0 |

(RDY/BSY) |

|

29 |

|||||||

EWDS |

1 |

00 |

|

0 0 X X X X X X X X |

|

|

|

— |

|

High-Z |

|

13 |

|||||||||||||

TABLE 1-5: |

INSTRUCTION SET FOR 93LC76: ORG=0 (X8 ORGANIZATIONI |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Instruction |

SB |

Opcode |

|

|

|

|

Address |

|

|

|

|

|

|

|

Data In |

|

|

Data Out |

|

Req. CLK |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cycles |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

READ |

1 |

10 |

|

X |

A9 A8 A7 A6 A5 A4 A3 A2 A1 |

A0 |

|

|

— |

|

|

D7 - D0 |

|

22 |

|||||||||||

EWEN |

1 |

00 |

|

1 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

|

|

High-Z |

|

14 |

||

ERASE |

1 |

11 |

|

X |

A9 A8 A7 A6 A5 A4 A3 A2 A1 |

A0 |

|

|

— |

|

|

(RDY/BSY) |

|

14 |

|||||||||||

ERAL |

1 |

00 |

|

1 |

0 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

|

(RD Y/BSY) |

|

14 |

|||

WRITE |

1 |

01 |

|

X |

A9 A8 A7 A6 A5 A4 A3 A2 A1 |

A0 |

|

|

D7 - D0 |

|

(RDY/BSY) |

|

22 |

||||||||||||

WRAL |

1 |

00 |

|

0 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

D7 - D0 |

|

|

(RDY/BSY) |

|

22 |

|||

EWDS |

1 |

00 |

|

0 0 X X X X X X X X |

|

|

|

— |

|

|

|

High-Z |

|

14 |

|||||||||||

TABLE 1-6: |

INSTRUCTION SET FOR 93LC86: ORG=1 (X16 ORGANIZATION) |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Instruction |

SB |

Opcode |

|

|

|

|

Address |

|

|

|

|

|

Data In |

|

Data Out |

|

Req. CLK |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Cycles |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

READ |

1 |

10 |

|

A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 |

|

|

|

— |

|

D15 - D0 |

|

29 |

|||||||||||||

EWEN |

1 |

00 |

|

1 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

High-Z |

|

13 |

||||

ERASE |

1 |

11 |

|

A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 |

|

|

|

— |

|

(RDY/BSY) |

|

13 |

|||||||||||||

ERAL |

1 |

00 |

|

1 |

0 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

(RD Y/BSY) |

|

13 |

||||

WRITE |

1 |

01 |

|

A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 |

|

D15 - D0 |

(RDY/BSY) |

|

29 |

||||||||||||||||

WRAL |

1 |

00 |

|

0 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

|

D15 - D0 |

(RDY/BSY) |

|

29 |

|||||||

EWDS |

1 |

00 |

|

0 0 X X X X X X X X |

|

|

|

— |

|

High-Z |

|

13 |

|||||||||||||

TABLE 1-7: |

INSTRUCTION SET FOR 93LC86: ORG=0 (X8 ORGANIZATION) |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Instruction |

SB |

Opcode |

|

|

|

|

|

Address |

|

|

|

|

|

|

|

Data In |

|

|

Data Out |

|

Req. CLK |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cycles |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

READ |

1 |

10 |

|

A10 |

A9 |

A8 A7 A6 A5 A4 A3 A2 A1 |

A0 |

|

— |

|

|

|

D7 - D0 |

22 |

|||||||||||

EWEN |

1 |

00 |

|

1 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

|

|

High-Z |

14 |

|||

ERASE |

1 |

11 |

|

A10 |

A9 |

A8 A7 A6 A5 A4 A3 A2 A1 |

A0 |

|

— |

|

|

|

(RDY/BSY) |

14 |

|||||||||||

ERAL |

1 |

00 |

|

1 |

0 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

|

|

(RD Y/BSY) |

14 |

|||

WRITE |

1 |

01 |

|

A10 |

A9 |

A8 A7 A6 A5 A4 A3 A2 A1 |

A0 |

|

D7 - D0 |

(RDY/BSY) |

22 |

||||||||||||||

WRAL |

1 |

00 |

|

0 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

D7 - D0 |

|

|

(RDY/BSY) |

22 |

||||

EWDS |

1 |

00 |

|

0 |

0 |

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

— |

|

|

|

High-Z |

14 |

|||

DS21131C-page 4 |

Preliminary |

1996 Microchip Technology Inc.

Loading...

Loading...