Microchip Technology Inc 24C01CT-I-SN, 24C01CT-I-P, 24C01CT-E-ST, 24C01CT-E-SN, 24C01CT-E-P Datasheet

...

M |

24C01C |

|

1K 5.0V I2C™ Serial EEPROM |

|

|

FEATURES

•Single supply with operation from 4.5 to 5.5V

•Low power CMOS technology

-1 mA active current typical

-10 A standby current typical at 5.5V

•Organized as a single block of 128 bytes (128 x 8)

•2-wire serial interface bus, I2C compatible

•100kHz and 400 kHz compatibility

•Page-write buffer for up to 16 bytes

•Self-timed write cycle (including auto-erase)

•Fast 1 mS write cycle time for byte or page mode

•Address lines allow up to eight devices on bus

•1,000,000 erase/write cycles guaranteed

•ESD protection > 4,000V

•Data retention > 200 years

•8-pin PDIP, SOIC or TSSOP packages

•Available for extended temperature ranges

- |

Commercial (C): |

0°C to |

+70°C |

|

- |

Industrial (I): |

-40°C |

to |

+85°C |

- |

Automotive (E) |

-40°C |

to |

+125°C |

DESCRIPTION

The Microchip Technology Inc. 24C01C is a 1K bit Serial Electrically Erasable PROM with a voltage range of 4.5V to 5.5V. The device is organized as a single block of 128 x 8-bit memory with a 2-wire serial interface. Low current design permits operation with typical standby and active currents of only 10 A and 1 mA respectively. The device has a page-write capability for up to 16 bytes of data and has fast write cycle times of only 1 mS for both byte and page writes. Functional address lines allow the connection of up to eight 24C01C devices on the same bus for up to 8K bits of contiguous EEPROM memory. The device is available in the standard 8-pin PDIP, 8-pin SOIC (150 mil), and TSSOP packages.

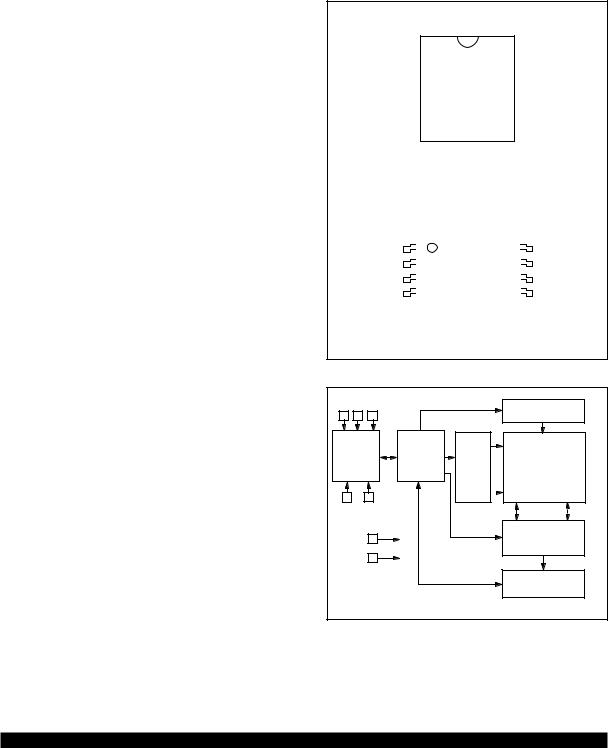

PACKAGE TYPES

PDIP/SOIC

A0 |

|

|

1 |

8 |

|

Vcc |

|

|

|

|

24C01C |

7 |

|

TEST |

A1 |

|

|

2 |

|

|||

|

|

|

|||||

|

|

|

|

6 |

|

SCL |

|

A2 |

|

|

3 |

|

|

||

|

|

|

|

5 |

|

SDA |

|

Vss |

|

|

4 |

|

|

||

TSSOP

A0 |

1 |

24C01C |

8 |

VCC |

|

|

|

||||

A1 |

2 |

7 |

TEST |

||

|

|||||

A2 |

3 |

|

6 |

SCL |

|

VSS |

4 |

|

5 |

SDA |

|

|

|

|

|

|

BLOCK DIAGRAM

A0 A1 A2 |

|

HV Generator |

|

|

|

||

I/O |

Memory |

|

|

Control |

Control |

EEPROM |

|

Logic |

|||

Logic |

|||

XDEC |

|||

|

|||

|

|

Array |

|

SDA SCL |

|

|

|

Vcc |

|

YDEC |

|

Vss |

|

|

|

|

|

SENSE AMP |

|

|

|

R/W CONTROL |

I2C is a trademark of Philips Corporation.

1997 Microchip Technology Inc. |

Preliminary |

DS21201A-page 1 |

24C01C

1.0ELECTRICAL CHARACTERISTICS

1.1Maximum Ratings*

VCC........................................................................ |

7.0V |

All inputs and outputs w.r.t. VSS...... |

-0.6V to VCC +1.0V |

Storage temperature ........................... |

-65˚C to +150˚C |

Ambient temp. with power applied....... |

-65˚C to +125˚C |

Soldering temperature of leads (10 seconds) ... |

+300˚C |

ESD protection on all pins ...................................... |

≥ 4 kV |

*Notice: Stresses above those listed under “Maximum ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 1-1: PIN FUNCTION TABLE

Name |

Function |

|

|

|

|

VSS |

Ground |

SDA |

Serial Data |

SCL |

Serial Clock |

VCC |

+4.5V to 5.5V Power Supply |

A0, A1, A2 |

Chip Selects |

Test |

Test Pin: may be tied high, low or |

|

left floating |

|

|

TABLE 1-2: |

DC CHARACTERISTICS |

|

|

|

|

||

All parameters apply across the speci- |

VCC = +4.5V to +5.5V |

Tamb = 0°C to +70°C |

|||||

fied operating ranges unless otherwise |

Commercial (C): |

||||||

noted. |

|

Industrial (I): |

|

Tamb = -40°C to +85°C |

|||

|

|

Automotive (E): |

Tamb = -40°C to +125°C |

||||

|

|

|

|

|

|

|

|

|

Parameter |

Symbol |

|

Min. |

Max. |

Units |

Conditions |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCL and SDA pins: |

|

|

|

|

|

|

|

High level input voltage |

VIH |

|

0.7 VCC |

|

V |

|

|

Low level input voltage |

VIL |

|

|

.3 VCC |

V |

|

|

Hysteresis of Schmitt trigger inputs |

VHYS |

|

0.05 VCC |

— |

V |

(Note) |

|

Low level output voltage |

VOL |

|

|

.40 |

V |

IOL = 3.0 mA, VCC = 4.5V |

|

|

|

|

|

|

|

|

|

Input leakage current |

ILI |

|

-10 |

10 |

A |

VIN = 0.1V to 5.5V, WP = Vss |

|

Output leakage current |

ILO |

|

-10 |

10 |

A |

VOUT = 0.1V to 5.5V |

|

|

|

|

|

|

|

|

|

Pin capacitance (all inputs/outputs) |

CIN, COUT |

|

— |

10 |

pF |

VCC = 5.0V (Note) |

|

|

|

|

|

|

Tamb = 25°C, f = 1 MHz |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Operating current |

ICC Read |

|

— |

1 |

mA |

VCC = 5.5V, SCL = 400 kHz |

|

|

|

|

|

|

|

||

ICC Write |

|

— |

3 |

mA |

VCC = 5.5V |

||

|

|

|

|||||

|

|

|

|

|

|

|

|

Standby current |

ICCS |

|

— |

50 |

A |

VCC = 5.5V, SDA = SCL = VCC |

|

|

|

|

|

|

|

|

|

Note: This parameter is periodically sampled and not 100% tested.

DS21201A-page 2 |

Preliminary |

1997 Microchip Technology Inc. |

|

|

|

|

|

|

|

|

24C01C |

|

|

|

|

|

|

|

|

|

|

|

TABLE 1-3: |

AC CHARACTERISTICS |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

All parameters apply across the specified oper- |

Vcc = 4.5V to 5.5V |

Tamb = 0°C to +70°C |

|||||||

ating ranges unless otherwise noted. |

|

Commercial (C): |

|||||||

|

|

|

|

Industrial (I): |

Tamb = -40°C to +85°C |

||||

|

|

|

|

Automotive (E): |

Tamb = -40°C to +125°C |

||||

|

|

|

|

|

|

|

|

|

|

Parameter |

Symbol |

Tamb > +85°C |

-40°C ≤ Tamb ≤ +85°C |

Units |

Remarks |

||||

|

|

|

|

||||||

Min. |

Max. |

Min. |

Max. |

||||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Clock frequency |

|

FCLK |

— |

100 |

— |

400 |

kHz |

|

|

Clock high time |

|

THIGH |

4000 |

— |

600 |

— |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

Clock low time |

|

TLOW |

4700 |

— |

1300 |

— |

ns |

|

|

|

|

|

|

|

|

|

|

||

SDA and SCL rise time |

TR |

— |

1000 |

— |

300 |

ns |

(Note 1) |

||

|

|

|

|

|

|

|

|

||

SDA and SCL fall time |

TF |

— |

300 |

— |

300 |

ns |

(Note 1) |

||

|

|

|

|

|

|

|

|

||

START condition hold time |

THD:STA |

4000 |

— |

600 |

— |

ns |

After this period the first |

||

|

|

|

|

|

|

|

|

clock pulse is generated |

|

|

|

|

|

|

|

|

|

||

START condition setup time |

TSU:STA |

4700 |

— |

600 |

— |

ns |

Only relevant for repeated |

||

|

|

|

|

|

|

|

|

START condition |

|

|

|

|

|

|

|

|

|

||

Data input hold time |

THD:DAT |

0 |

— |

0 |

— |

ns |

(Note 2) |

||

|

|

|

|

|

|

|

|

||

Data input setup time |

TSU:DAT |

250 |

— |

100 |

— |

ns |

|

||

|

|

|

|

|

|

|

|

||

STOP condition setup time |

TSU:STO |

4000 |

— |

600 |

— |

ns |

|

||

|

|

|

|

|

|

|

|

||

Output valid from clock |

TAA |

— |

3500 |

— |

900 |

ns |

(Note 2) |

||

|

|

|

|

|

|

|

|

|

|

Bus free time |

|

TBUF |

4700 |

— |

1300 |

— |

ns |

Time the bus must be free |

|

|

|

|

|

|

|

|

|

before a new transmission |

|

|

|

|

|

|

|

|

|

can start |

|

|

|

|

|

|

|

|

|

||

Output fall time from VIH |

TOF |

— |

250 |

20 +0.1 CB |

250 |

ns |

(Note 1), CB ≤ 100 pF |

||

minimum to VIL maximum |

|

|

|

|

|

|

|

||

Input filter spike suppression |

TSP |

— |

50 |

— |

50 |

ns |

(Note 3) |

||

(SDA and SCL pins) |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Write cycle time |

|

TWR |

— |

1.5 |

— |

1 |

ms |

Byte or Page mode |

|

|

|

|

|

|

|

|

|

|

|

Endurance |

|

|

1M |

— |

1M |

— |

cycles |

25°C, VCC = 5.0V, Block |

|

|

|

|

|

|

|

|

|

Mode (Note 4) |

|

|

|

|

|

|

|

|

|

|

|

Note 1: Not 100% tested. CB = total capacitance of one bus line in pF.

2:As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

3:The combined TSP and VHYS specifications are due to Schmitt trigger inputs which provide improved noise spike suppression. This eliminates the need for a TI specification for standard operation.

4:This parameter is not tested but guaranteed by characterization. For endurance estimates in a specifi application, please consult the Total Endurance Model which can be obtained on our BBS or website.

FIGURE 1-1: BUS TIMING DATA

|

TF |

THIGH |

|

TR |

|

|

|

||

|

|

|

|

|

SCL |

TSU:STA |

|

|

|

|

|

|

|

|

|

TLOW |

THD:DAT |

TSU:DAT |

TSU:STO |

SDA |

THD:STA |

|

|

|

IN |

|

|

|

|

TSP |

|

|

|

|

|

|

|

TAA |

TBUF |

|

|

|

|

|

SDA |

|

|

|

|

OUT |

|

|

|

|

1997 Microchip Technology Inc. |

Preliminary |

DS21201A-page 3 |

24C01C

2.0PIN DESCRIPTIONS

2.1SDA Serial Data

This is a bi-directional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pull-up resistor to VCC (typical 10 kΩ for 100 kHz, 2 kΩ for 400 kHz).

For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

2.2SCL Serial Clock

This input is used to synchronize the data transfer from and to the device.

2.3A0, A1, A2

The levels on these inputs are compared with the corresponding bits in the slave address. The chip is selected if the compare is true.

Up to eight 24C01C devices may be connected to the same bus by using different chip select bit combinations. These inputs must be connected to either VCC or VSS.

2.4Test

This pin is utilized for testing purposes only. It may be tied high, tied low or left floating.

2.5Noise Protection

The 24C01C employs a VCC threshold detector circuit which disables the internal erase/write logic if the VCC is below 3.8 volts at nominal conditions.

The SCL and SDA inputs have Schmitt trigger and filter circuits which suppress noise spikes to assure proper device operation even on a noisy bus.

3.0FUNCTIONAL DESCRIPTION

The 24C01C supports a bi-directional 2-wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions, while the 24C01C works as slave. Both master and slave can operate as transmitter or receiver but the master device determines which mode is activated.

DS21201A-page 4 |

Preliminary |

1997 Microchip Technology Inc. |

Loading...

Loading...