Microchip Technology Inc 28C17AT-20-L, 28C17AT-15I-SO, 28C17AT-15I-L, 28C17AT-15-SO, 28C17AT-15-L Datasheet

...

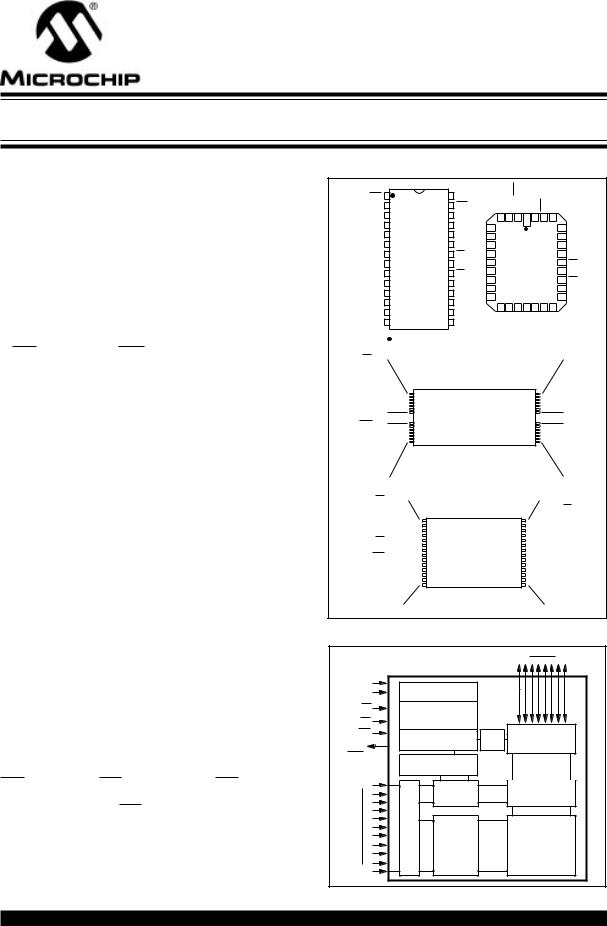

28C17A

16K (2K x 8) CMOS EEPROM

FEATURES

•Fast Read Access Time—150 ns

•CMOS Technology for Low Power Dissipation

-30 mA Active

-100 A Standby

• Fast Byte Write Time—200 s or 1 ms

•Data Retention >200 years

•High Endurance - Minimum 104 Erase/Write Cycles

•Automatic Write Operation

-Internal Control Timer

-Auto-Clear Before Write Operation

-On-Chip Address and Data Latches

•Data Polling; Ready/Busy

•Chip Clear Operation

•Enhanced Data Protection

-VCC Detector

-Pulse Filter

-Write Inhibit

•Electronic Signature for Device Identification

•5-Volt-Only Operation

•Organized 2Kx8 JEDEC Standard Pinout

-28 Pin Dual-In-Line Package

-32-Pin PLCC Package

-28-Pin Thin Small Outline Package (TSOP) 8x20mm

-28-Pin Very Small Outline Package (VSOP) 8x13.4mm

•Available for Extended Temperature Ranges:

-Commercial: 0˚C to +70˚C

-Industrial: -40˚C to +85˚C

DESCRIPTION

PACKAGE TYPES

RDY/BSY |

• 1 |

|

28 |

Vcc |

|

|

|

RDY/BSY2 |

|

32 Vcc |

31 WE 30 NC |

|

|

||

|

NC |

2 |

|

27 |

WE |

|

4 A7 |

3 NC |

1 NU |

|

|

||||

|

A7 |

3 |

|

26 |

NC |

|

|

|

|||||||

|

A6 |

4 |

DIP/SOIC |

25 |

A8 |

A6 |

5 |

|

|

|

|

|

29 |

A8 |

|

|

A5 |

5 |

24 |

A9 |

|

|

|

|

|

|

|||||

|

A5 |

6 |

|

|

|

|

|

28 |

A9 |

|

|||||

|

A4 |

6 |

23 |

NC |

A4 7 |

|

|

PLCC |

|

27 |

NC |

|

|||

|

A3 |

7 |

22 |

OE |

A3 8 |

|

|

|

26 |

NC |

|

||||

|

A2 |

8 |

21 |

A10 |

A2 9 |

|

|

|

25 |

OE |

|

||||

|

A1 |

9 |

20 |

CE |

A1 |

10 |

|

|

|

24 |

A10 |

|

|||

|

A0 |

11 |

|

|

|

23 |

CE |

|

|||||||

|

A0 |

10 |

19 |

I/O7 |

|

|

|

|

|||||||

|

|

NC |

12 |

|

|

|

|

|

22 |

I/O7 |

|

||||

I/O0 |

11 |

|

18 |

I/O6 |

|

|

|

|

|

|

|||||

|

I/O0 |

13 |

|

|

|

|

|

21 |

I/O6 |

|

|||||

I/O1 |

12 |

|

17 |

I/O5 |

|

14 |

15 |

16 |

17 |

18 |

19 |

20 |

|

|

|

I/O2 |

13 |

|

16 |

I/O4 |

|

|

|

||||||||

|

|

I/O1 |

I/O2 |

Vss |

NU |

I/O3 |

I/O4 |

I/O5 |

|

|

|||||

|

VSS |

14 |

|

15 |

I/O3 |

|

|

|

|||||||

|

|

• Pin 1 indicator on PLCC on top of package |

|

|

|||||||||||

OE |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

28 |

A10 |

NC |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

27 |

CE |

A9 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

26 |

I/07 |

A8 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

25 |

I/06 |

NC |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

24 |

I/05 |

WE |

6 |

|

|

|

|

TSOP |

|

|

|

|

|

|

|

23 |

I/04 |

Vcc |

7 |

|

|

|

|

|

|

|

|

|

|

|

22 |

I/03 |

|

RDY/BSY |

8 |

|

|

|

|

|

|

|

|

|

|

|

21 |

Vss |

|

NC |

9 |

|

|

|

|

|

|

|

|

|

|

|

20 |

I/02 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

A7 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

19 |

I/01 |

A6 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

18 |

I/00 |

A5 |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

17 |

A0 |

A4 |

13 |

|

|

|

|

|

|

|

|

|

|

|

|

16 |

A1 |

A3 |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

15 |

A2 |

|

OE |

22 |

|

|

|

|

|

|

|

|

|

21 |

A10 |

|

|

|

NC |

23 |

|

|

|

|

|

|

|

|

|

20 |

CE |

|

|

|

A9 |

24 |

|

|

|

|

|

|

|

|

|

19 |

I/O7 |

|

|

|

A8 |

25 |

|

|

|

|

|

|

|

|

|

18 |

I/O6 |

|

|

|

NC |

26 |

|

|

|

VSOP |

|

|

|

|

|

17 |

I/O5 |

|

|

|

WE |

27 |

|

|

|

|

|

|

|

|

16 |

I/O4 |

|

||

|

VCC |

28 |

|

|

|

|

|

|

|

|

15 |

I/O3 |

|

||

RDY/BSY |

1 |

|

|

|

|

|

|

|

|

14 |

VSS |

|

|||

|

NC |

2 |

|

|

|

|

|

|

|

|

13 |

I/O2 |

|

||

|

A7 |

3 |

|

|

|

|

|

|

|

|

|

12 |

I/O1 |

|

|

|

A6 |

4 |

|

|

|

|

|

|

|

|

|

11 |

I/O0 |

|

|

|

A5 |

5 |

|

|

|

|

|

|

|

|

|

10 |

A0 |

|

|

|

A4 |

6 |

|

|

|

|

|

|

|

|

|

9 |

A1 |

|

|

|

A3 |

7 |

|

|

|

|

|

|

|

|

|

8 |

A2 |

|

|

The Microchip Technology Inc. 28C17A is a CMOS 16K non- |

BLOCK DIAGRAM |

|

|

|

|||||

|

|

|

|

I/O0 |

I/O7 |

||||

volatile electrically Erasable PROM. |

The 28C17A |

is |

|

|

|

|

|||

|

|

|

|

|

|

||||

accessed like a static RAM for the read or write cycles without |

VSS |

|

|

|

|

|

|||

the need of external components. During a “byte write”, the |

|

Data Protection |

|

|

|

||||

VCC |

|

|

|

|

|||||

address and data are latched internally, freeing the micropro- |

|

|

Circuitry |

|

|

|

|||

CE |

|

Chip Enable/ |

|

|

|

||||

cessor address and data bus for other operations. Following |

|

|

|

|

|||||

OE |

|

Output Enable |

|

|

|

||||

the initiation of write cycle, the device will go to a busy state |

|

Control Logic |

|

|

|

||||

WE |

Auto Erase/Write |

Data |

Input/Output |

||||||

and automatically clear and write the latched data using an |

|||||||||

Rdy/ |

|

Timing |

Poll |

Buffers |

|

||||

internal control timer. To determine when the write cycle is |

Busy |

Program Voltage |

|

|

|

||||

complete, the user has a choice of monitoring the Ready/ |

|

|

|

|

|||||

|

|

Generation |

|

|

|

||||

Busy output or using Data polling. The Ready/Busy pin is an |

A0 |

|

Y |

|

Y Gating |

|

|||

open drain output, which allows easy configuration in wired- |

|

|

|

|

|||||

|

|

Decoder |

|

|

|||||

|

L |

|

|

|

|||||

or systems. Alternatively, Data polling allows the user to read |

|

|

|

|

|

||||

|

a |

|

|

|

|

||||

the location last written to when the write operation is com- |

|

t |

|

|

|

|

|||

|

c |

|

|

|

|

||||

plete. CMOS design and processing enables this part to be |

|

h |

X |

|

16K bit |

|

|||

|

e |

|

|

||||||

used in systems where reduced power consumption and reli- |

|

s |

Decoder |

|

Cell Matrix |

|

|||

ability are required. A complete family of packages is offered |

A10 |

|

|

|

|

|

|||

to provide the utmost flexibility in applications. |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||

1996 Microchip Technology Inc. |

|

|

|

|

|

|

DS11127G-page 1 |

||

28C17A

1.0ELECTRICAL CHARACTERISTICS

1.1MAXIMUM RATINGS*

VCC and input voltages w.r.t. VSS ....... |

-0.6V to + 6.25V |

||

Voltage on |

|

w.r.t. VSS |

-0.6V to +13.5V |

OE |

|||

Voltage on A9 w.r.t. VSS ...................... |

-0.6V to +13.5V |

||

Output Voltage w.r.t. VSS ................ |

-0.6V to VCC+0.6V |

||

Storage temperature .......................... |

-65˚C to +125˚C |

||

Ambient temp. with power applied ....... |

-50˚C to +95˚C |

||

*Notice: Stresses above those listed under “Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 1-1: PIN FUNCTION TABLE

Name |

|

|

Function |

||||||||

|

|

||||||||||

|

|

||||||||||

A0 - A10 |

Address Inputs |

||||||||||

|

|

|

|

|

|

|

|

|

Chip Enable |

||

CE |

|||||||||||

|

|

|

|

|

|

|

Output Enable |

||||

OE |

|||||||||||

|

|

|

|

|

Write Enable |

||||||

|

WE |

||||||||||

I/O0 - I/O7 |

Data Inputs/Outputs |

||||||||||

|

|

|

|

|

|

||||||

RDY/Busy |

Ready/Busy |

|

|||||||||

VCC |

+5V Power Supply |

||||||||||

VSS |

Ground |

||||||||||

|

|

NC |

No Connect; No Internal Connec- |

||||||||

|

|

|

|

|

|

|

|

|

tion |

||

|

|

NU |

Not Used; No External Connection |

||||||||

|

|

|

|

|

|

|

|

|

is Allowed |

||

|

|

|

|

|

|

|

|

|

|

|

|

TABLE 1-2: |

READ/WRITE OPERATION DC CHARACTERISTICS |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC = +5V ±10% |

|

|

|

|

|

|

|

|

|

|

|

Commercial (C): Tamb = 0˚C to +70˚C |

||||||

|

|

|

|

|

Industrial |

(I): Tamb = -40˚C to +85˚C |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

Status |

Symbol |

Min |

Max |

Units |

|

|

|

|

Conditions |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltages |

|

Logic ‘1’ |

VIH |

2.0 |

Vcc+1 |

V |

|

|

|

|

|

|

|

Logic ‘0’ |

VIL |

-0.1 |

0.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Input Leakage |

|

— |

I LI |

-10 |

10 |

A |

|

|

VIN = -0.1V to Vcc +1 |

||

|

|

|

|

|

|

|

|||||

Input Capacitance |

— |

C IN |

— |

10 |

pF |

V IN = 0V; Tamb = 25˚C; |

|||||

|

|

|

|

|

|

|

|

f = 1 MHz |

|||

|

|

|

|

|

|

|

|

|

|||

Output Voltages |

|

Logic ‘1’ |

VOH |

2.4 |

|

V |

|

IOH = -400 A |

|||

|

|

Logic ‘0’ |

VOL |

|

0.45 |

V |

IOL = 2.1 mA |

||||

|

|

|

|

|

|

|

|

|

|

||

Output Leakage |

|

— |

I LO |

-10 |

10 |

A |

|

|

VOUT = -0.1V to VCC |

||

|

|

|

|

|

|

|

|

+0.1V |

|||

|

|

|

|

|

|

|

|||||

Output Capacitance |

— |

C OUT |

— |

12 |

pF |

V IN = 0V; Tamb = 25˚C; |

|||||

|

|

|

|

|

|

|

|

f = 1 MHz |

|||

|

|

|

|

|

|

|

|||||

Power Supply Current, Active |

TTL input |

ICC |

— |

30 |

mA |

f = 5 MHz (Note 1) |

|||||

|

|

|

|

|

|

|

|

VCC = 5.5V; |

|||

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Current, Standby |

TTL input |

ICC(S)TTL |

— |

2 |

mA |

|

|

|

|

= VIH (0˚C to +70˚C) |

|

|

|

CE |

|||||||||

|

|

TTL input |

ICC(S)TTL |

|

3 |

mA |

|

|

CE |

= VIH (-40˚C to +85˚C) |

|

|

|

CMOS input |

ICC(S)CMOS |

|

100 |

A |

|

|

= VCC-0.3 to Vcc +1 |

||

|

|

|

|

CE |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

Note 1: AC power supply current above 5MHz: 1mA/MHz.

DS11127G-page 2 |

1996 Microchip Technology Inc. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

28C17A |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TABLE 1-3: |

READ OPERATION AC CHARACTERISTICS |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

AC Testing Waveform: |

VIH = 2.4V; VIL = 0.45V; VOH = 2.0V; VOL = 0.8V |

|||||||||||||||

|

|

|

|

|

|

|

|

Output Load: |

|

1 TTL Load + 100 pF |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

Input Rise and Fall Times: |

20 ns |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Ambient Temperature: |

Commercial (C): |

|

Tamb |

= |

0˚C to +70˚C |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

Industrial |

|

(I): |

|

Tamb |

= |

-40˚C to +85˚C |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

Symbol |

28C17A-15 |

28C17A-20 |

|

28C17A-25 |

Units |

|

|

Conditions |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

Min |

Max |

Min |

Max |

|

Min |

|

Max |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Address to Output Delay |

tACC |

— |

150 |

— |

200 |

|

— |

|

250 |

ns |

OE |

|

|

= |

|

= VIL |

|||||||

|

|

CE |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

to Output Delay |

tCE |

— |

150 |

— |

200 |

|

— |

|

250 |

ns |

OE |

|

|

= VIL |

||||||

|

CE |

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

to Output Delay |

tOE |

— |

70 |

— |

80 |

|

— |

|

100 |

ns |

CE |

|

|

= VIL |

||||||

|

OE |

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

or |

|

High to Output |

tOFF |

0 |

50 |

0 |

55 |

|

0 |

|

70 |

ns |

|

|

|

|

|||||

|

CE |

OE |

|

|

|

|

||||||||||||||||||

|

Float |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Output Hold from Address, |

tOH |

0 |

— |

0 |

— |

|

0 |

|

— |

ns |

|

|

|

|

|

|

|

||||||

|

|

or |

|

whichever occurs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

CE |

OE, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

first. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

Endurance |

|

— |

1M |

— |

1M |

— |

|

1M |

|

— cycles |

25 |

|

|

°C, Vcc = |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.0V, Block |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Mode (Note) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be obtained on our BBS or website.

FIGURE 1-1: READ WAVEFORMS

Address |

VIH |

Address Valid |

|

||||

|

|

||||||

|

VIL |

|

|

|

|

|

|

|

VIH |

|

|

|

|

|

|

CE |

VIL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCE(2) |

|

|

||

|

VIH |

|

|

|

|

|

|

OE |

|

|

|

|

|

|

tOFF(1,3) |

|

VIL |

|

|

|

|

|

|

|

|

|

|

|

tOE(2) |

tOH |

|

|

VOH |

|

|

|

|

|

High Z |

Data |

High Z |

|

|

|

|

|

|

VOL |

|

|

|

|

|

Valid Output |

|

|

|

|

|

|

|

|

|

|

|

tACC |

|

|

|

|

|

VIH

WE

VOL

Notes: (1) tOFF is specified for OE or CE, whichever occurs first

(2)OE may be delayed up to tCE - tOE after the falling edge of CE without impact on tCE

(3)This parameter is sampled and is not 100% tested

1996 Microchip Technology Inc. |

DS11127G-page 3 |

Loading...

Loading...