Microchip Technology Inc 27LV64-30I-P, 27LV64-30I-L, 27LV64-30-SO, 27LV64-30-P, 27LV64-25I-SO Datasheet

...

27LV64

64K (8K x 8) Low-Voltage CMOS EPROM

FEATURES

•Wide voltage range 3.0V to 5.5V

•High speed performance

-200 ns access time available at 3.0V

•CMOS Technology for low power consumption

-8 mA active current at 3.0V

-20 mA active current at 5.5V

-100 A standby current

•Factory programming available

•Auto-insertion-compatible plastic packages

•Auto ID aids automated programming

•Separate chip enable and output enable controls

•High speed “express” programming algorithm

•Organized 8K x 8: JEDEC standard pinouts

-28-pin Dual-in-line package

-32-pin PLCC Package

-28-pin SOIC package

-Tape and reel

•Available for the following temperature ranges:

- |

Commercial: |

0˚C to +70˚C |

- |

Industrial: |

-40˚C to +85˚C |

DESCRIPTION

The Microchip Technology Inc. 27LV64 is a low-voltage (3.0 volt) CMOS EPROM designed for battery powered applications. The device is organized as 8K x 8 (8KByte) non-volatile memory product. The 27LV64 consumes only 8mA maximum of active current during a 3.0 volt read operation therefore improving battery performance. This device is designed for very low voltage applications where conventional 5.0 volt only EPROMs can not be used. Accessing individual bytes from an address transition or from power-up (chip enable pin going low) is accomplished in less than 200 ns at 3.0V.This device allows system designers the ability to use low voltage non-volatile memory with today’s low voltage microprocessors and peripherals in battery powered applications.

A complete family of packages is offered to provide the most flexibility in applications. For surface mount applications, PLCC or SOIC packaging is available. Tape and reel packaging is also available for PLCC or SOIC packages.

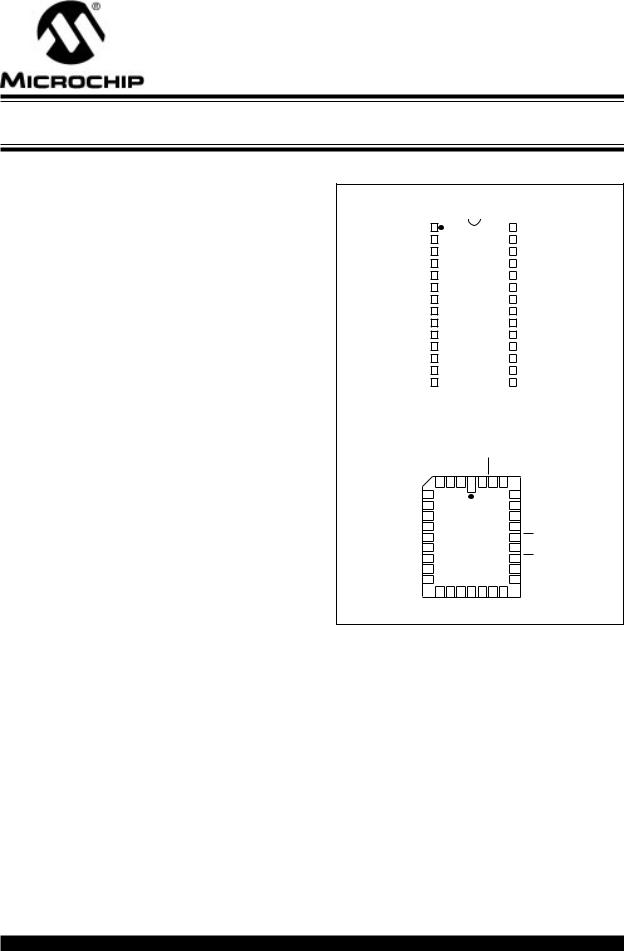

PACKAGE TYPES

DIP/SOIC

VPP |

• 1 |

|

28 |

|

VCC |

||

A12 |

2 |

|

27 |

|

|

||

|

|

PGM |

|

||||

A7 |

3 |

|

26 |

|

NC |

||

A6 |

4 |

|

25 |

|

A8 |

||

A5 |

5 |

27LV64 |

24 |

|

A9 |

||

A4 |

6 |

23 |

|

A11 |

|||

|

|

||||||

A3 |

7 |

|

22 |

|

|

|

|

|

|

OE |

|||||

A2 |

8 |

|

21 |

|

A10 |

||

A1 |

9 |

|

20 |

|

|

|

|

|

|

CE |

|||||

A0 |

10 |

|

19 |

|

O7 |

||

O0 |

11 |

|

18 |

|

O6 |

||

O1 |

12 |

|

17 |

|

O5 |

||

O2 |

13 |

|

16 |

|

O4 |

||

VSS |

14 |

|

15 |

|

O3 |

||

|

|

|

|

|

|

|

|

PLCC

|

A7 |

A12 |

VPP |

NU |

Vcc |

PGM |

NC |

|

|

4 |

3 |

2 |

1 |

32 |

31 |

30 |

|

A6 |

5 |

|

|

|

|

|

29 |

A8 |

A5 |

6 |

|

|

|

|

|

28 |

A9 |

A4 |

7 |

|

|

27LV64 |

|

|

27 |

A11 |

A3 |

8 |

|

|

|

|

26 |

NC |

|

A2 |

9 |

|

|

|

|

25 |

OE |

|

A1 |

10 |

|

|

|

|

24 |

A10 |

|

A0 |

11 |

|

|

|

|

23 |

CE |

|

|

|

|

|

|

||||

NC |

12 |

|

|

|

|

|

22 |

O7 |

O0 |

13 |

|

|

|

|

|

21 |

O6 |

|

14 |

15 |

16 |

17 |

18 |

19 |

20 |

|

|

O1 |

O2 |

VSS |

NU |

O3 |

O4 |

O5 |

|

1996 Microchip Technology Inc. |

DS11024E-page 1 |

27LV64

1.0ELECTRICAL CHARACTERISTICS

1.1Maximum Ratings*

VCC and input voltages w.r.t. VSS ....... |

-0.6V to + 7.25V |

VPP voltage w.r.t. VSS during |

|

programming .......................................... |

-0.6V to +14V |

Voltage on A9 w.r.t. VSS ...................... |

-0.6V to +13.5V |

Output voltage w.r.t. VSS ............... |

-0.6V to VCC +1.0V |

Storage temperature .......................... |

-65˚C to +150˚C |

Ambient temp. with power applied ..... |

-65˚C to +125˚C |

*Notice: Stresses above those listed under “Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 1-1: PIN FUNCTION TABLE

Name |

Function |

|||||

|

|

|||||

|

|

|||||

A0-A12 |

Address Inputs |

|||||

|

|

|

|

|

|

Chip Enable |

|

|

CE |

||||

|

|

|

|

|

Output Enable |

|

|

|

OE |

||||

|

|

|

Program Enable |

|||

PGM |

||||||

|

VPP |

Programming Voltage |

||||

O0 - O7 |

Data Output |

|||||

|

VCC |

+5V Or +3V Power Supply |

||||

|

VSS |

Ground |

||||

|

|

NC |

No Connection; No Internal Connec- |

|||

|

|

|

|

|

|

tions |

|

|

NU |

Not Used; No External Connection Is |

|||

|

|

|

|

|

|

Allowed |

|

|

|

|

|

|

|

TABLE 1-2: |

READ OPERATION DC CHARACTERISTICS |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

VCC = 3.0V to 5.5V unless otherwise specified |

||||||||||

|

|

|

|

Commercial: |

|

Tamb = 0˚C to +70˚C |

||||||||

|

|

|

|

Industrial: |

|

Tamb = -40˚C to +85˚C |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Parameter |

Part* |

Status |

Symbol |

Min. |

|

Max. |

Units |

|

|

|

|

Conditions |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltages |

|

all |

Logic "1" |

VIH |

2.0 |

|

VCC+1 |

V |

|

|

|

|

|

|

|

|

|

Logic "0" |

VIL |

-0.5 |

|

0.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Input Leakage |

|

all |

— |

I LI |

-10 |

|

10 |

A |

VIN = 0 to VCC |

|||||

|

|

|

|

|

|

|

|

|

|

|||||

Output Voltages |

|

all |

Logic "1" |

VOH |

2.4 |

|

|

V |

IOH = -400 A |

|||||

|

|

|

Logic "0" |

VOL |

|

|

0.45 |

V |

|

IOL = 2.1 mA |

||||

|

|

|

|

|

|

|

|

|

|

|||||

Output Leakage |

|

all |

— |

I LO |

-10 |

|

10 |

A |

VOUT = 0V to VCC |

|||||

|

|

|

|

|

|

|

|

|

||||||

Input Capacitance |

all |

— |

C IN |

— |

|

6 |

pF |

V IN = 0V; Tamb = 25°C; |

||||||

|

|

|

|

|

|

|

|

|

|

f = 1 MHz |

||||

|

|

|

|

|

|

|

|

|

||||||

Output Capacitance |

all |

— |

C OUT |

— |

|

12 |

pF |

V OUT = 0V; Tamb = 25°C; |

||||||

|

|

|

|

|

|

|

|

|

f = 1 MHz |

|||||

|

|

|

|

|

|

|

|

|

|

|||||

Power Supply Current, |

C |

TTL input |

ICC1 |

— |

|

20 @ 5.0V |

mA |

|

VCC = 5.5V; VPP = VCC |

|||||

Active |

|

|

|

|

|

|

8 @ 3.0V |

mA |

|

f = 1 MHz; |

||||

|

|

I |

TTL input |

ICC2 |

— |

|

25 @ 5.0V |

mA |

|

|

|

= |

|

= VIL; |

|

|

|

OE |

CE |

||||||||||

|

|

|

|

|

|

|

10 @ 3.0V |

mA |

|

IOUT = 0 mA; |

||||

|

|

|

|

|

|

|

|

|

|

VIL = -0.1 to 0.8V; |

||||

|

|

|

|

|

|

|

|

|

|

VIH = 2.0 to VCC; |

||||

|

|

|

|

|

|

|

|

|

|

Note 1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Current, |

C |

TTL input |

ICC(S) |

— |

|

1 @ 3.0V |

mA |

|

|

|

|

|

|

|

Standby |

|

I |

TTL input |

|

|

|

2@ 3.0V |

mA |

|

|

|

|

|

|

|

|

all |

CMOS input |

|

|

|

100 @ 3.0V |

A |

|

|

= VCC ± 0.2V |

|||

|

|

|

|

|

CE |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

* Parts: C=Commercial Temperature Range; I=Industrial Temperature Range

Note 1: Typical active current increases .5 mA per MHz up to operating frequency for all temperature ranges.

DS11024E-page 2 |

1996 Microchip Technology Inc. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

27LV64 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TABLE 1-3: |

READ OPERATION AC CHARACTERISTICS |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

AC Testing Waveform: |

|

|

|

VIH = 2.4V and VIL = 0.45V; VOH = 2.0V VOL = 0.8V |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

Output Load: |

|

|

|

|

|

|

1 TTL Load + 100 pF |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

Input Rise and Fall Times: |

10 ns |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

Ambient Temperature: |

|

|

|

Commercial: |

|

|

|

Tamb = 0˚C to +70˚C |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Industrial: |

|

|

|

|

Tamb = -40˚C to +85˚C |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Parameter |

Sym |

27LV64-20 |

|

|

27LV64-25 |

27LV64-30 |

Units |

|

|

Conditions |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

Min. |

Max. |

|

Min. |

Max. |

Min. |

Max. |

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

Address to Output Delay |

tACC |

— |

200 |

|

|

|

— |

|

|

250 |

— |

|

|

300 |

ns |

CE |

|

= |

|

= VIL |

|||||||||||

|

|

OE |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

to Output Delay |

tCE |

— |

200 |

|

|

|

— |

|

|

250 |

— |

|

|

300 |

ns |

OE |

|

|

= VIL |

||||||||||

|

CE |

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

to Output Delay |

tOE |

— |

100 |

|

|

|

— |

|

|

125 |

— |

|

|

125 |

ns |

CE |

|

|

= VIL |

||||||||||

|

OE |

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

or |

|

to O/P High |

tOFF |

0 |

50 |

|

|

0 |

|

|

50 |

|

0 |

|

50 |

|

ns |

|

|

|

|

|||||||||

|

CE |

OE |

|

|

|

|

|

|

||||||||||||||||||||||||

|

Impedance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Output Hold from Address |

|

or |

tOH |

0 |

|

— |

|

0 |

|

|

— |

0 |

|

|

— |

ns |

|

|

|

|

|

|

|

||||||||

|

CE |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

OE, |

whichever goes first |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

FIGURE 1-1: READ WAVEFORMS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

Address |

VIH |

|

|

|

|

|

|

|

Address Valid |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

VIL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CE |

VIL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCE(2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

VIH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

VIL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tOFF(1,3) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tOE(2) |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tOH |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Outputs |

VOH |

|

High Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

High Z |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Valid Output |

|

|

|

|

|

|

|||||||||||

|

O0 - O7 |

VOL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

tACC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Notes: (1) tOFF is specified for OE or CE, whichever occurs first

(2)OE may be delayed up to tCE - t OE after the falling edge of CE without impact on tCE

(3)This parameter is sampled and is not 100% tested.

1996 Microchip Technology Inc. |

DS11024E-page 3 |

27LV64

TABLE 1-4: PROGRAMMING DC CHARACTERISTICS

|

|

|

Ambient Temperature: Tamb = 25°C ± 5°C |

|||

|

|

|

VCC = 6.5V ± 0.25V, VPP = VH = 13.0V ± 0.25V |

|||

|

|

|

|

|

|

|

Parameter |

Status |

Symbol |

Min. |

Max. |

Units |

Conditions |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltages |

Logic”1” |

VIH |

2.0 |

VCC+1 |

V |

|

|

Logic”0” |

VIL |

-0.1 |

0.8 |

V |

|

|

|

|

|

|

|

|

Input Leakage |

— |

I LI |

-10 |

10 |

A |

VIN = 0V to VCC |

|

|

|

|

|

|

|

Output Voltages |

Logic”1” |

VOH |

2.4 |

|

V |

IOH = -400 A |

|

Logic”0” |

VOL |

|

0.45 |

V |

IOL = 2.1 mA |

|

|

|

|

|

|

|

VCC Current, program & verify |

— |

I CC2 |

— |

20 |

mA |

Note 1 |

|

|

|

|

|

|

|

VPP Current, program |

— |

I PP2 |

— |

25 |

mA |

Note 1 |

|

|

|

|

|

|

|

A9 Product Identification |

— |

VH |

11.5 |

12.5 |

V |

|

|

|

|

|

|

|

|

Note 1: VCC must be applied simultaneously or before VPP and removed simultaneously or after VPP.

TABLE 1-5: |

PROGRAMMING AC CHARACTERISTICS |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|||||

|

for Program, Program Verify |

AC Testing Waveform: |

VIH=2.4V and VIL=0.45V; VOH=2.0V; VOL=0.8V |

||||||||||

|

and Program Inhibit Modes |

Ambient Temperature: |

Tamb=25°C ± 5°C |

|

|

||||||||

|

|

|

|

|

|

|

VCC= 6.5V ± 0.25V, VPP = VH = 13.0V ± 0.25V |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

Min. |

Max. |

Units |

Remarks |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||

|

Address Set-Up Time |

|

tAS |

2 |

— |

s |

|

||||||

|

|

|

|

|

|

|

|

||||||

|

Data Set-Up Time |

|

tDS |

2 |

— |

s |

|

||||||

|

|

|

|

|

|

|

|

|

|

||||

|

Data Hold Time |

|

|

|

tDH |

2 |

— |

s |

|

||||

|

|

|

|

|

|

|

|

||||||

|

Address Hold Time |

|

tAH |

0 |

— |

s |

|

||||||

|

|

|

|

|

|

|

|

|

|

||||

|

Float Delay (2) |

|

|

|

tDF |

0 |

130 |

ns |

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

VCC Set-Up Time |

|

|

|

tVCS |

2 |

— |

s |

|

||||

|

|

|

|

|

|

|

|

||||||

|

Program Pulse Width (1) |

|

tPW |

95 |

105 |

s |

100 s typical |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Set-Up Time |

|

|

|

tCES |

2 |

— |

s |

|

||

CE |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Set-Up Time |

|

|

|

tOES |

2 |

— |

s |

|

||

|

OE |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

||||

|

VPP Set-Up Time |

|

|

|

tVPS |

2 |

— |

s |

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

Data Valid from |

|

|

|

|

tOE |

|

100 |

ns |

|

|||

|

OE |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 1: For express algorithm, initial programming width tolerance is 100 s ±5%.

Note 2: This parameter is only sampled and not 100% tested. Output float is defined as the point where data is no longer driven (see timing diagram).

DS11024E-page 4 |

1996 Microchip Technology Inc. |

Loading...

Loading...