Fairchild Semiconductor DM74ALS165MX, DM74ALS165M, DM74ALS165N Datasheet

January 1986

Revised February 2000

DM74ALS165

8-Bit Parallel In/Serial Out Shift Register

General Description

The DM74ALS165 is an 8-bit serial register that, when clocked, shifts the data toward serial output, QH. Parallel-in access to each stage is provided by eight individual direct data inputs that are enabled by a low level at the SH/LD input. The DM74ALS165 also features a clock inhibit function and a complemented serial output, QH.

Clocking is accomplished by a LOW-to-HIGH transition of the CLK input while SH/LD is held HIGH and CLK INH is held LOW. The functions of the CLK and CLK INH (clock inhibit) inputs are interchangeable. Since a LOW CLK input and a LOW-to-HIGH transition of CLK INH will also accomplish clocking, CLK INH should be changed to the high level only while the CLK input is HIGH. Parallel loading is inhibited when SH/LD is held HIGH. The parallel inputs to the register are enabled while SH/LD is LOW independently of the levels of CLK, CLK INH, or SER inputs.

Features

■Complementary outputs

■Direct overriding load (data) inputs

■Gated clock inputs

■Parallel-to-serial data conversion

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74ALS165M |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|

|

|

DM74ALS165N |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

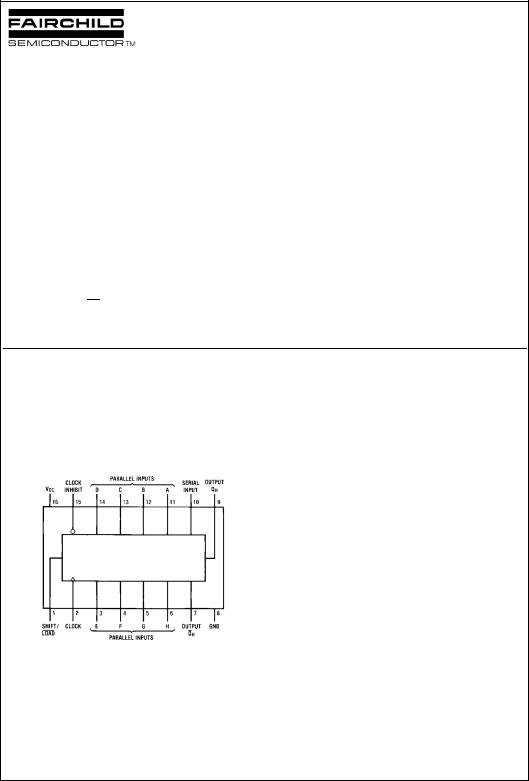

Connection Diagram |

Function Table |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Inputs |

|

|

Internal |

|

||

|

|

|

|

|

Outputs |

Output |

|||

|

Shift/ |

Clock |

Clock |

Serial |

Parallel |

||||

|

|

|

|

|

|

|

|

|

QH |

|

Load |

Inhibit |

|

|

|

A...H |

QA |

QB |

|

|

L |

X |

X |

|

X |

a...h |

a |

b |

h |

|

H |

L |

L |

|

X |

X |

QA0 |

QB0 |

QH0 |

|

H |

L |

− |

|

H |

X |

H |

QAn |

QGn |

|

H |

L |

− |

|

L |

X |

L |

QAn |

QGn |

|

H |

− |

L |

|

H |

X |

H |

QAn |

QGn |

|

H |

− |

L |

|

L |

X |

L |

QAn |

QGn |

|

H |

H |

X |

|

X |

X |

QA0 |

QB0 |

QH0 |

|

H = HIGH Level (steady-state), |

|

|

|

|

|

|||

|

L = LOW Level (steady-state) |

|

|

|

|

|

|||

|

X = Don't Care (any input, including transitions) |

|

|

|

|||||

− = Transition from LOW-to-HIGH level

a...h = The level of steady-state input at inputs A through H, respectively QA0, QB0, QH0 = The level of QA, QB, or QH, respectively, before the

indicated steady-state input conditions were established

QAn, QGn = The level of QA or QG, respectively, before the most recent

− transition of the clock

Register Shift Out In/Serial Parallel Bit-8 DM74ALS165

© 2000 Fairchild Semiconductor Corporation |

DS006712 |

www.fairchildsemi.com |

DM74ALS165

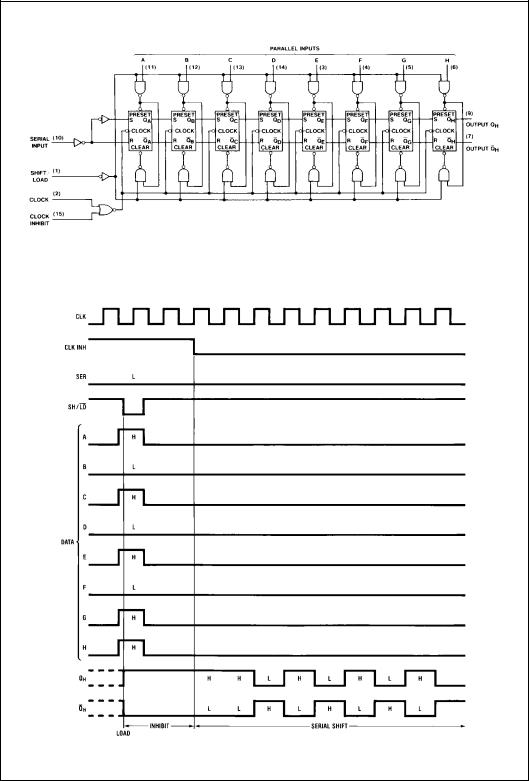

Logic Diagram

Timing Diagram

Typical Shift, Load, and Inhibit Sequences

www.fairchildsemi.com |

2 |

Loading...

Loading...