SGS Thomson Microelectronics M29W800AT90N6T, M29W800AT90N6, M29W800AT90N1T, M29W800AB90N1T, M29W800AB90N1 Datasheet

...

M29W800AT

M29W800AB

8 Mbit (1Mb x8 or 512Kb x16, Boot Block) Low Voltage Single Supply Flash Memory

■2.7V to 3.6V SUPPLY VOLTAGE for PROGRAM, ERASE and READ OPERATIONS

■ACCESS TIME: 80ns

■PROGRAMMING TIME: 10μs typical

■PROGRAM/ERASE CONTROLLER (P/E.C.)

±Program Byte-by-Byte or Word-by-Word

±Status Register bits and Ready/Busy Output

■SECURITY PROTECTION MEMORY AREA

■INSTRUCTION ADDRESS CODING: 3 digits

■MEMORY BLOCKS

±Boot Block (Top or Bottom location)

±Parameter and Main blocks

■BLOCK, MULTI-BLOCK and CHIP ERASE

■MULTI BLOCK PROTECTION/TEMPORARY UNPROTECTION MODES

■ERASE SUSPEND and RESUME MODES

±Read and Program another Block during Erase Suspend

■LOW POWER CONSUMPTION

±Stand-by and Automatic Stand-by

■100,000 PROGRAM/ERASE CYCLES per BLOCK

■20 YEARS DATA RETENTION

±Defectivity below 1ppm/year

■ELECTRONIC SIGNATURE

±Manufacturer Code: 20h

±Top Device Code, M29W800AT: D7h

±Bottom Device Code, M29W800AB: 5Bh

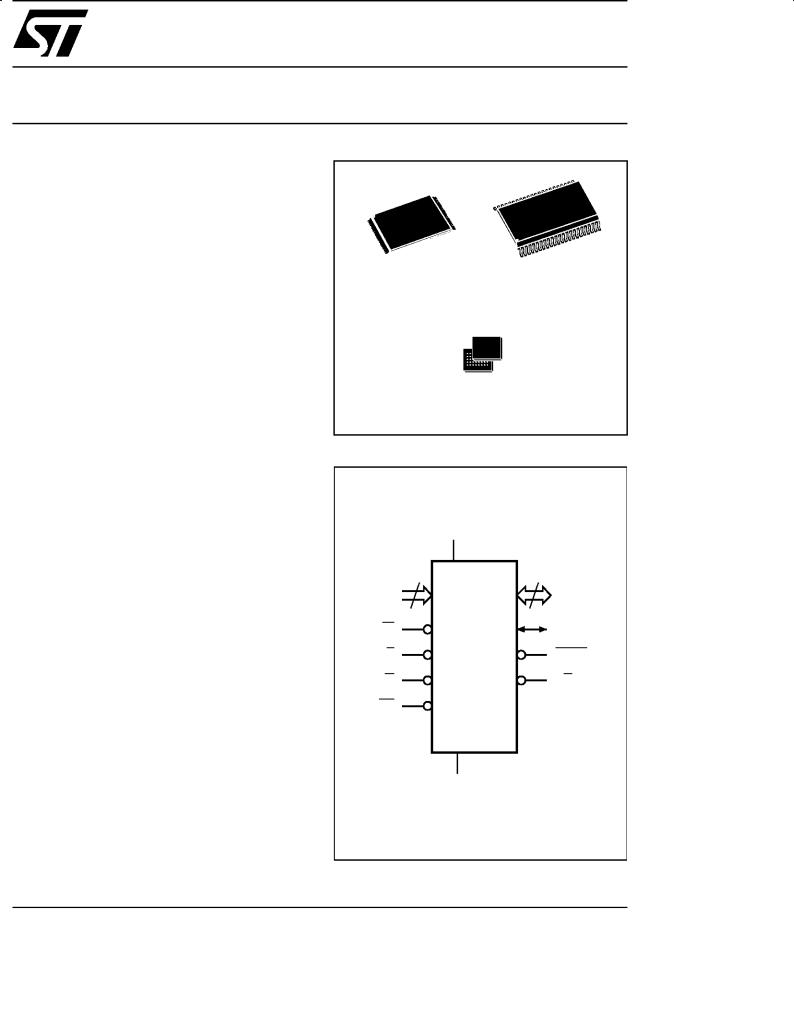

44

|

1 |

TSOP48 (N) |

SO44 (M) |

12 x 20mm |

|

FBGA

LFBGA48 (ZA) 8 x 6 solder balls

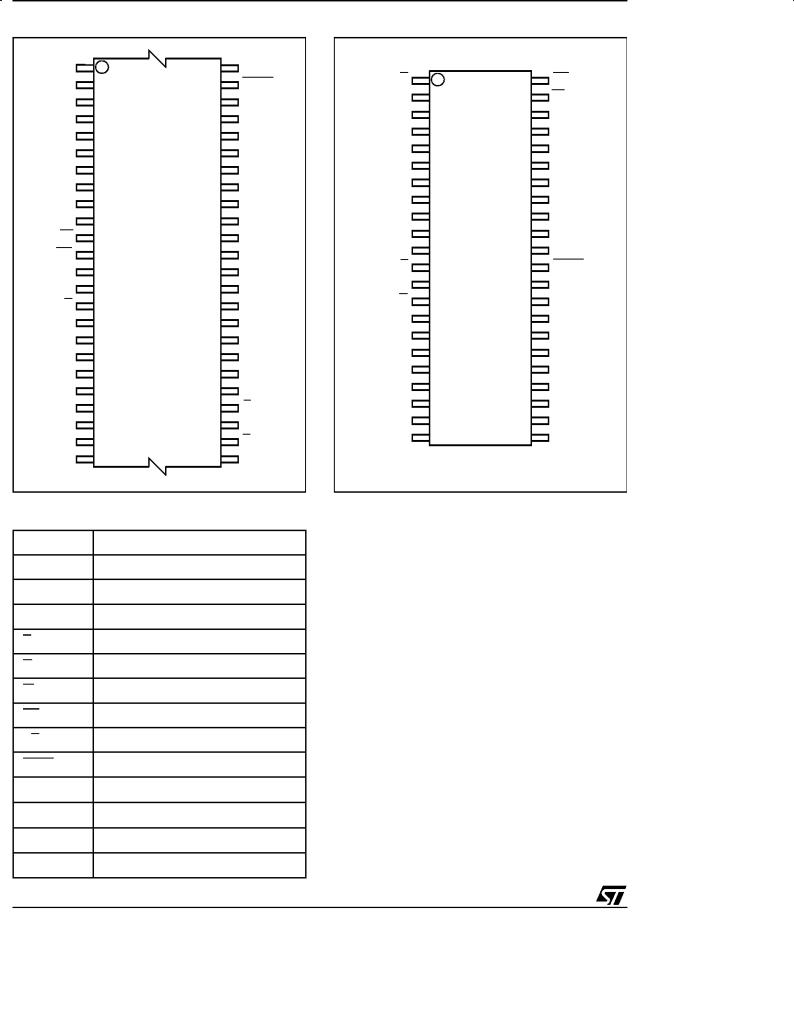

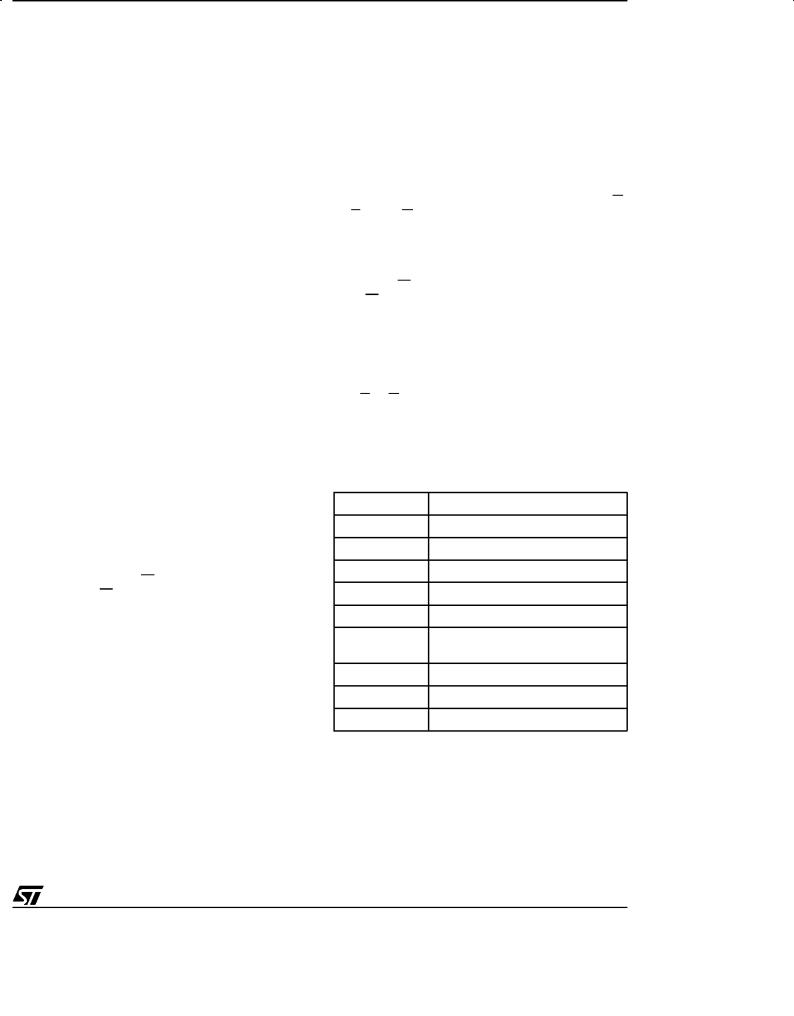

Figure 1. Logic Diagram

|

VCC |

|

|

19 |

|

15 |

|

A0-A18 |

|

DQ0-DQ14 |

|

W |

|

DQ15A±1 |

|

E |

M29W800AT |

BYTE |

|

M29W800AB |

|||

|

|

||

G |

|

RB |

|

RP |

|

|

VSS

AI02599

March 2000 |

1/33 |

M29W800AT, M29W800AB

Figure 2. TSOP Connections

A15 |

1 |

|

48 |

A16 |

A14 |

|

|

|

BYTE |

A13 |

|

|

|

VSS |

A12 |

|

|

|

DQ15A±1 |

A11 |

|

|

|

DQ7 |

A10 |

|

|

|

DQ14 |

A9 |

|

|

|

DQ6 |

A8 |

|

|

|

DQ13 |

NC |

|

|

|

DQ5 |

NC |

|

|

|

DQ12 |

W |

|

|

|

DQ4 |

RP |

12 |

M29W800T |

37 |

VCC |

NC |

13 |

M29W800B |

36 |

DQ11 |

NC |

|

|

|

DQ3 |

RB |

|

|

|

DQ10 |

A18 |

|

|

|

DQ2 |

A17 |

|

|

|

DQ9 |

A7 |

|

|

|

DQ1 |

A6 |

|

|

|

DQ8 |

A5 |

|

|

|

DQ0 |

A4 |

|

|

|

G |

A3 |

|

|

|

VSS |

A2 |

|

|

|

E |

A1 |

24 |

|

25 |

A0 |

|

|

|

AI02179 |

|

Table 1. Signal Names

A0-A18 |

Address Inputs |

DQ0-DQ7 |

Data Input/Outputs, Command Inputs |

DQ8-DQ14 |

Data Input/Outputs |

DQ15A±1 |

Data Input/Output or Address Input |

E |

Chip Enable |

G |

Output Enable |

W |

Write Enable |

RP |

Reset/Block Temporary Unprotect |

RB |

Ready/Busy Output |

BYTE |

Byte/Word Organization |

VCC |

Supply Voltage |

VSS |

Ground |

NC |

Not Connected Internally |

DU |

Don't Use as Internally Connected |

Figure 3. SO Connections

RB |

1 |

44 |

RP |

A18 |

2 |

43 |

W |

A17 |

3 |

42 |

A8 |

A7 |

4 |

41 |

A9 |

A6 |

5 |

40 |

A10 |

A5 |

6 |

39 |

A11 |

A4 |

7 |

38 |

A12 |

A3 |

8 |

37 |

A13 |

A2 |

9 |

36 |

A14 |

A1 |

10 |

35 |

A15 |

A0 |

11 M29W800T 34 |

A16 |

|

E |

12 M29W800B 33 |

BYTE |

|

VSS |

13 |

32 |

VSS |

G |

14 |

31 |

DQ15A±1 |

DQ0 |

15 |

30 |

DQ7 |

DQ8 |

16 |

29 |

DQ14 |

DQ1 |

17 |

28 |

DQ6 |

DQ9 |

18 |

27 |

DQ13 |

DQ2 |

19 |

26 |

DQ5 |

DQ10 |

20 |

25 |

DQ12 |

DQ3 |

21 |

24 |

DQ4 |

DQ11 |

22 |

23 |

VCC |

|

|

AI02181 |

|

DESCRIPTION

The M29W800A is a non-volatile memory that may be erased electrically at the block or chip level and programmed in-system on a Byte-by-Byte or Word-by-Word basis using only a single 2.7V to 3.6V VCC supply. For Program and Erase operations the necessary high voltages are generated internally. The device can also be programmed in standard programmers.

The array matrix organisation allows each block to be erased and reprogrammed without affecting other blocks. Blocks can be protected against programing and erase on programming equipment, and temporarily unprotected to make changes in the application. Each block can be programmed and erased over 100,000 cycles.

Instructions for Read/Reset, Auto Select for reading the Electronic Signature or Block Protection status, Programming, Block and Chip Erase, Erase Suspend and Resume are written to the device in cycles of commands to a Command Interface using standard microprocessor write timings.

The device is offered in TSOP48 (12 x 20mm), SO44 and LFBGA48 0.8 mm ball pitch packages.

2/33

M29W800AT, M29W800AB

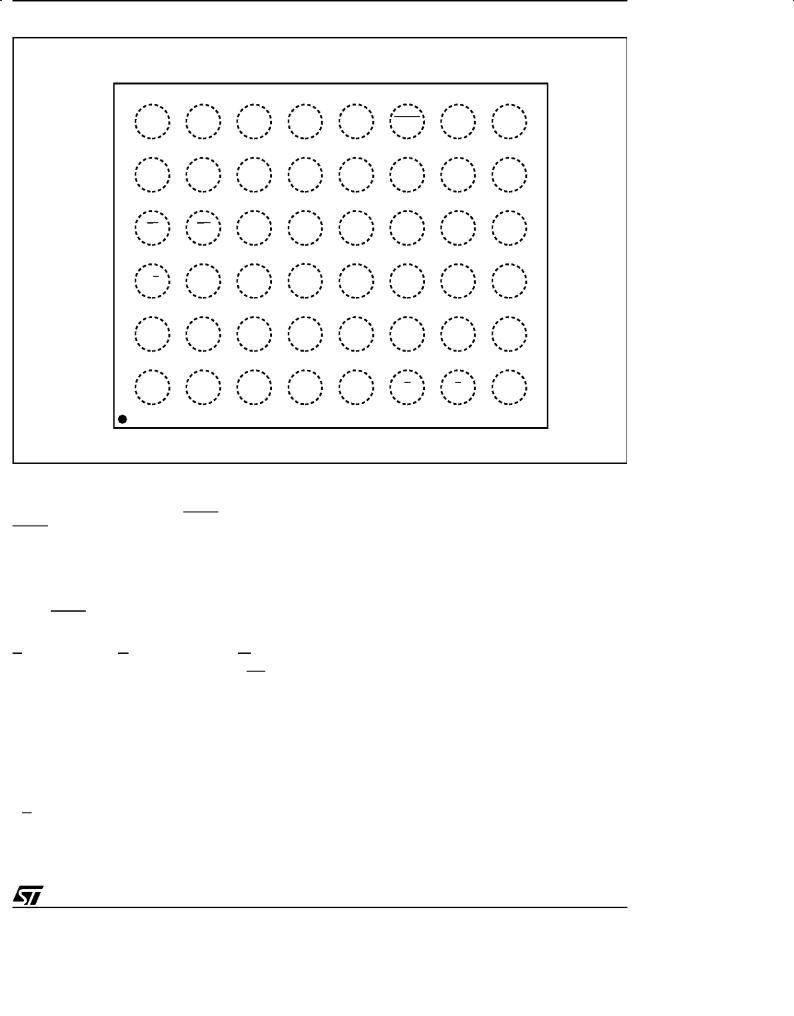

Figure 4. LFBGA Connections (Top view through package)

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

F |

A13 |

A12 |

A14 |

A15 |

A16 |

BYTE |

DQ15 |

VSS |

|

A±1 |

|||||||||

|

|

|

|

|

|

|

|

||

E |

A9 |

A8 |

A10 |

A11 |

DQ7 |

DQ14 |

DQ13 |

DQ6 |

|

D |

W |

RP |

DU |

DU |

DQ5 |

DQ12 |

VCC |

DQ4 |

|

C |

RB |

DU |

A18 |

DU |

DQ2 |

DQ10 |

DQ11 |

DQ3 |

|

B |

A7 |

A17 |

A6 |

A5 |

DQ0 |

DQ8 |

DQ9 |

DQ1 |

|

A |

A3 |

A4 |

A2 |

A1 |

A0 |

E |

G |

VSS |

AI00656

Organisation |

Memory Blocks |

The M29W800A is organised as 1M x8 or 512K x16 bits selectable by the BYTE signal. When BYTE is Low the Byte-wide x8 organisation is selected and the address lines are DQ15A±1 and A0-A18. The Data Input/Output signal DQ15A±1 acts as address line A±1 which selects the lower or upper Byte of the memory word for output on DQ0-DQ7, DQ8-DQ14 remain at High impedance. When BYTE is High the memory uses the address inputs A0-A18 and the Data Input/Outputs DQ0DQ15. Memory control is provided by Chip Enable E, Output Enable G and Write Enable W inputs.

A Reset/Block Temporary Unprotection RP tri-lev- el input provides a hardware reset when pulled Low, and when held High (at VID) temporarily unprotects blocks previously protected allowing them to be programed and erased. Erase and Program operations are controlled by an internal Program/ Erase Controller (P/E.C.). Status Register data output on DQ7 provides a Data Polling signal, and DQ6 and DQ2 provide Toggle signals to indicate the state of the P/E.C operations. A Ready/Busy RB output indicates the completion of the internal algorithms.

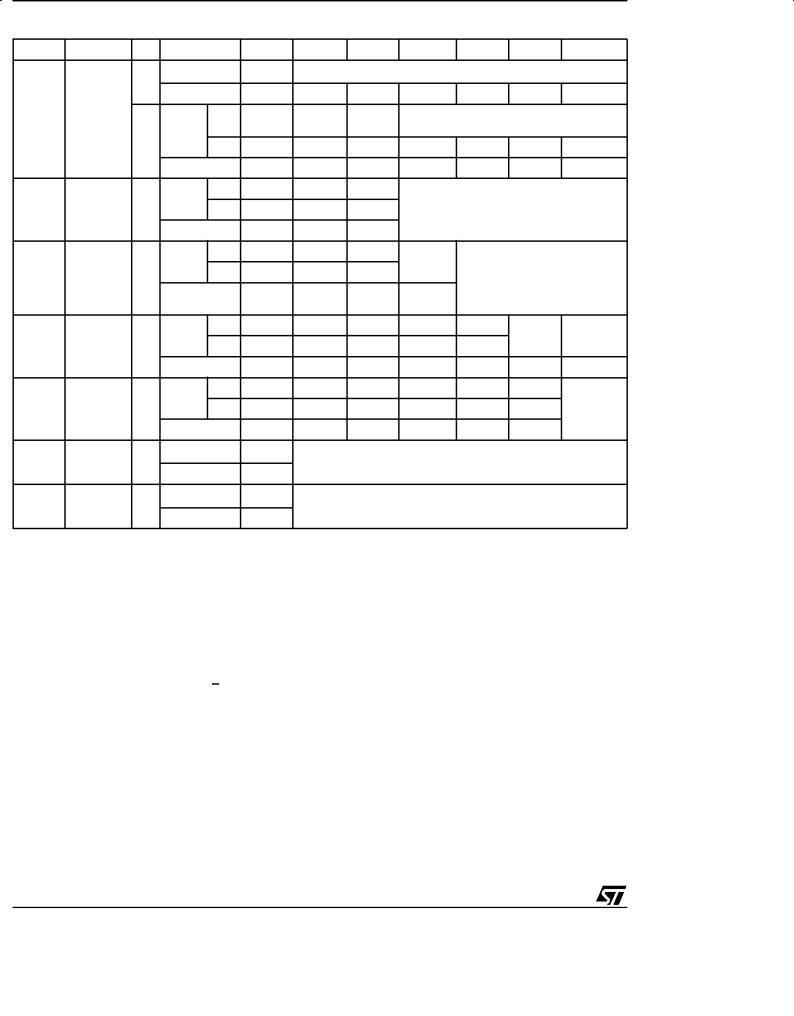

The devices feature asymmetrically blocked architecture providing system memory integration. Both M29W800AT and M29W800AB devices have an array of 19 blocks, one Boot Block of 16 KBytes or 8 KWords, two Parameter Blocks of 8 KBytes or 4 KWords, one Main Block of 32 KBytes or 16 KWords and fifteen Main Blocks of 64 KBytes or 32 KWords. The M29W800AT has the Boot Block at the top of the memory address space and the M29W800AB locates the Boot Block starting at the bottom. The memory maps are showed in Figure 5.

Each block can be erased separately, any combination of blocks can be specified for multi-block erase or the entire chip may be erased. The Erase operations are managed automatically by the P/ E.C. The block erase operation can be suspended in order to read from or program to any block not being erased, and then resumed.

Block protection provides additional data security. Each block can be separately protected or unprotected against Program or Erase on programming equipment. All previously protected blocks can be temporarily unprotected in the application.

3/33

M29W800AT, M29W800AB

Table 2. Absolute Maximum Ratings (1)

Symbol |

Parameter |

Value |

Unit |

TA |

Ambient Operating Temperature (3) |

±40 to 85 |

°C |

T |

Temperature Under Bias |

±50 to 125 |

° |

BIAS |

C |

||

TSTG |

Storage Temperature |

±65 to 150 |

°C |

(2) |

Input or Output Voltage |

±0.6 to 5 |

V |

VIO |

|||

VCC |

Supply Voltage |

±0.6 to 5 |

V |

V(A9, E, G, RP) (2) |

A9, E, G, RP Voltage |

±0.6 to 13.5 |

V |

Note: 1. Except for the rating ºOperating Temperature Rangeº, stresses above those listed in the Table ºAbsolute Maximum Ratingsº may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

2.Minimum Voltage may undershoot to ±2V during transition and for less than 20ns during transitions.

3.Depends on range.

Bus Operations

The following operations can be performed using the appropriate bus cycles: Read (Array, Electronic Signature, Block Protection Status), Write command, Output Disable, Stan-by, Reset, Block Protection, Unprotection, Protection Verify, Unprotection Verify and Block Temporary Unprotection. See Tables 5 and 6.

Command Interface

Instructions, made up of commands written in cycles, can be given to the Program/Erase Controller through a Command Interface (C.I.). For added data protection, program or erase execution starts after 4 or 6 cycles. The first, second, fourth and fifth cycles are used to input Coded cycles to the C.I. This Coded sequence is the same for all Program/Erase Controller instructions. The 'Command' itself and its confirmation, when applicable, are given on the third, fourth or sixth cycles. Any incorrect command or any improper command sequence will reset the device to Read Array mode.

Instructions

Seven instructions are defined to perform Read Array, Auto Select (to read the Electronic Signature or Block Protection Status), Program, Block Erase, Chip Erase, Erase Suspend and Erase Resume.

The internal P/E.C. automatically handles all timing and verification of the Program and Erase operations. The Status Register Data Polling, Toggle, Error bits and the RB output may be read at any time, during programming or erase, to monitor the progress of the operation.

Instructions are composed of up to six cycles. The first two cycles input a Coded sequence to the Command Interface which is common to all instructions (see Table 9).

The third cycle inputs the instruction set-up command. Subsequent cycles output the addressed data, Electronic Signature or Block Protection Status for Read operations. In order to give additional data protection, the instructions for Program and Block or Chip Erase require further command inputs. For a Program instruction, the fourth command cycle inputs the address and data to be programmed. For an Erase instruction (Block or Chip), the fourth and fifth cycles input a further Coded sequence before the Erase confirm command on the sixth cycle. Erasure of a memory block may be suspended, in order to read data from another block or to program data in another block, and then resumed. When power is first applied or if VCC falls below VLKO, the command interface is reset to Read Array.

4/33

M29W800AT, M29W800AB

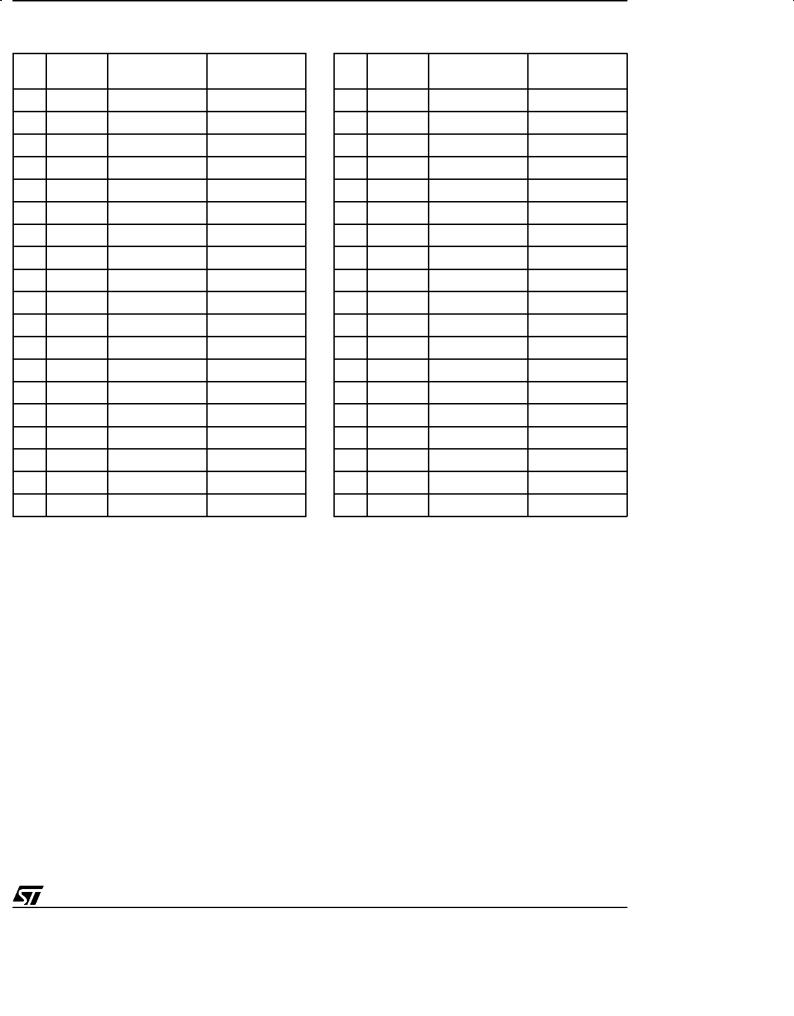

Table 3. Top Boot Block Addresses,

M29W800AT

Table 4. Bottom Boot Block Addresses,

M29W800AB

# |

Size |

Address Range |

Address Range |

# |

Size |

Address Range |

Address Range |

|

(Kbytes) |

(x8) |

(x16) |

(Kbytes) |

(x8) |

(x16) |

|||

|

|

|||||||

18 |

16 |

FC000h-FFFFFh 7E000h-7FFFFh |

18 |

64 |

F0000h-FFFFFh 78000h-7FFFFh |

|||

17 |

8 |

FA000h-FBFFFh 7D000h-7DFFFh |

17 |

64 |

E0000h-EFFFFh 70000h-77FFFh |

|||

16 |

8 |

F8000h-F9FFFh 7C000h-7CFFFh |

16 |

64 |

D0000h-DFFFFh 68000h-6FFFFh |

|||

15 |

32 |

F0000h-F7FFFh 78000h-7BFFFh |

15 |

64 |

C0000h-CFFFFh 60000h-67FFFh |

|||

14 |

64 |

E0000h-EFFFFh 70000h-77FFFh |

14 |

64 |

B0000h-BFFFFh 58000h-5FFFFh |

|||

13 |

64 |

D0000h-DFFFFh 68000h-6FFFFh |

13 |

64 |

A0000h-AFFFFh 50000h-57FFFh |

|||

12 |

64 |

C0000h-CFFFFh 60000h-67FFFh |

12 |

64 |

90000h-9FFFFh 48000h-4FFFFh |

|||

11 |

64 |

B0000h-BFFFFh 58000h-5FFFFh |

11 |

64 |

80000h-8FFFFh 40000h-47FFFh |

|||

10 |

64 |

A0000h-AFFFFh 50000h-57FFFh |

10 |

64 |

70000h-7FFFFh 38000h-3FFFFh |

|||

9 |

64 |

90000h-9FFFFh 48000h-4FFFFh |

9 |

64 |

60000h-6FFFFh 30000h-37FFFh |

|||

8 |

64 |

80000h-8FFFFh 40000h-47FFFh |

8 |

64 |

50000h-5FFFFh 28000h-2FFFFh |

|||

7 |

64 |

70000h-7FFFFh 38000h-3FFFFh |

7 |

64 |

40000h-4FFFFh 20000h-27FFFh |

|||

6 |

64 |

60000h-6FFFFh 30000h-37FFFh |

6 |

64 |

30000h-3FFFFh 18000h-1FFFFh |

|||

5 |

64 |

50000h-5FFFFh 28000h-2FFFFh |

5 |

64 |

20000h-2FFFFh 10000h-17FFFh |

|||

4 |

64 |

40000h-4FFFFh 20000h-27FFFh |

4 |

64 |

10000h-1FFFFh 08000h-0FFFFh |

|||

3 |

64 |

30000h-3FFFFh 18000h-1FFFFh |

3 |

32 |

08000h-0FFFFh 04000h-07FFFh |

|||

2 |

64 |

20000h-2FFFFh 10000h-17FFFh |

2 |

8 |

06000h-07FFFh 03000h-03FFFh |

|||

1 |

64 |

10000h-1FFFFh 08000h-0FFFFh |

1 |

8 |

04000h-05FFFh 02000h-02FFFh |

|||

0 |

64 |

00000h-0FFFFh |

00000h-07FFFh |

0 |

16 |

00000h-03FFFh |

00000h-01FFFh |

|

5/33

M29W800AT, M29W800AB

SIGNAL DESCRIPTIONS

See Figure 1 and Table 1.

Address Inputs (A0-A18). The address inputs for the memory array are latched during a write operation on the falling edge at Chip Enable E or Write Enable W. In Word-wide organisation the address lines are A0-A18, in Byte-wide organisation DQ15A±1 acts as an additional LSB address line. When A9 is raised to VID, either a Read Electronic Signature Manufacturer or Device Code, Block Protection Status or a Write Block Protection or Block Unprotection is enabled depending on the combination of levels on A0, A1, A6, A12 and A15.

Data Input/Outputs (DQ0-DQ7). These Inputs/ Outputs are used in the Byte-wide and Word-wide organisations. The input is data to be programmed in the memory array or a command to be written to the C.I. Both are latched on the rising edge of Chip Enable E or Write Enable W. The output is data from the Memory Array, the Electronic Signature Manufacturer or Device codes, the Block Protection Status or the Status register Data Polling bit DQ7, the Toggle Bits DQ6 and DQ2, the Error bit DQ5 or the Erase Timer bit DQ3. Outputs are valid when Chip Enable E and Output Enable G are active. The output is high impedance when the chip is deselected or the outputs are disabled and when RP is at a Low level.

Data Input/Outputs (DQ8-DQ14 and DQ15A± 1). These Inputs/Outputs are additionally used in the Word-wide organisation. When BYTE is High DQ8-DQ14 and DQ15A±1 act as the MSB of the Data Input or Output, functioning as described for DQ0-DQ7 above, and DQ8-DQ15 are 'don't care' for command inputs or status outputs. When BYTE is Low, DQ0-DQ14 are high impedance, DQ15A±1 is the Address A±1 input.

Chip Enable (E). The Chip Enable input activates the memory control logic, input buffers, decoders and sense amplifiers. E High deselects the memory and reduces the power consumption to the stan-by level. E can also be used to control writing to the command register and to the memory array, while W remains at a low level. The Chip Enable must be forced to VID during the Block Unprotection operation.

Output Enable (G). The Output Enable gates the outputs through the data buffers during a read operation. When G is High the outputs are High impedance. G must be forced to VID level during Block Protection and Unprotection operations.

Write Enable (W). This input controls writing to the Command Register and Address and Data latches.

Byte/Word Organization Select (BYTE). The BYTE input selects the output configuration for the device: Byte-wide (x8) mode or Word-wide (x16) mode. When BYTE is Low, the Byte-wide mode is selected and the data is read and programmed on DQ0-DQ7. In this mode, DQ8-DQ14 are at high impedance and DQ15A±1 is the LSB address. When BYTE is High, the Word-wide mode is selected and the data is read and programmed on DQ0-DQ15.

Ready/Busy Output (RB). Ready/Busy is an open-drain output and gives the internal state of the P/E.C. of the device. When RB is Low, the device is Busy with a Program or Erase operation and it will not accept any additional program or erase instructions except the Erase Suspend instruction. When RB is High, the device is ready for any Read, Program or Erase operation. The RB will also be High when the memory is put in Erase Suspend or Stan-by modes.

Reset/Block Temporary Unprotect Input (RP).

The RP Input provides hardware reset and protected block(s) temporary unprotection functions. Reset of the memory is achieved by pulling RP to

VIL for at least tPLPX. When the reset pulse is given, if the memory is in Read or Stan-by modes, it

will be available for new operations in tPHEL after the rising edge of RP. If the memory is in Erase, Erase Suspend or Program modes the reset will

take tPLYH during which the RB signal will be held at VIL. The end of the memory reset will be indicat-

ed by the rising edge of RB. A hardware reset during an Erase or Program operation will corrupt the data being programmed or the sector(s) being erased. See Tables 15, 16, and Figure 11.

Temporary block unprotection is made by holding RP at VID. In this condition previously protected blocks can be programmed or erased. The transition of RP from VIH to VID must slower than tPHPHH. See Tables 17, 18, and Figure 11. When RP is returned from VID to VIH all blocks temporarily unprotected will be again protected.

VCC Supply Voltage. The power supply for all operations (Read, Program and Erase).

VSS Ground. VSS is the reference for all voltage measurements.

6/33

DEVICE OPERATIONS

See Tables 5, 6 and 7.

Read. Read operations are used to output the contents of the Memory Array, the Electronic Signature, the Status Register or the Block Protection Status. Both Chip Enable E and Output Enable G must be low in order to read the output of the memory. A new operation is initiated either on the following edge of Chip Enable E or on any address transition with E at VIL.

Write. Write operations are used to give Instruction Commands to the memory or to latch input data to be programmed. A write operation is initiated when Chip Enable E is Low and Write Enable W is Low with Output Enable G High. Addresses are latched on the falling edge of W or E whichever occurs last. Commands and Input Data are latched on the rising edge of W or E whichever occurs first.

Output Disable. The data outputs are high impedance when the Output Enable G is High with Write Enable W High.

Stan-by. The memory is in stan-by when Chip Enable E is High and the P/E.C. is idle. The power consumption is reduced to the stan-by level and the outputs are high impedance, independent of the Output Enable G or Write Enable W inputs.

Automatic Stan-by. After 150ns of bus inactivity (no address transition, CE = VIL) and when CMOS levels are driving the addresses, the chip automatically enters a pseudo-stan-by mode where consumption is reduced to the CMOS stan-by value, while outputs still drive the bus (if G = VIL).

Electronic Signature. Two codes identifying the manufacturer and the device can be read from the memory. The manufacturer's code for STMicroelectronics is 20h, the device code is D7h for the M29W800AT (Top Boot) and 5Bh for the M29W800AB (Bottom Boot). These codes allow programming equipment or applications to automatically match their interface to the characteristics of the M29W800A. The Electronic Signature is output by a Read operation when the voltage applied to A9 is at VID and address inputs A1 is Low. The manufacturer code is output when the Address input A0 is Low and the device code when this input is High. Other Address inputs are ignored. The codes are output on DQ0-DQ7.

M29W800AT, M29W800AB

The Electronic Signature can also be read, without raising A9 to VID, by giving the memory the Instruction AS. If the Byte-wide configuration is selected the codes are output on DQ0-DQ7 with DQ8-DQ14 at High impedance; if the Word-wide configuration is selected the codes are output on DQ0-DQ7 with DQ8-DQ15 at 00h.

Block Protection. Each block can be separately protected against Program or Erase on programming equipment. Block protection provides additional data security, as it disables all program or erase operations. This mode is activated when both A9 and G are raised to VID and an address in the block is applied on A12-A18. Block protection is initiated on the edge of W falling to VIL. Then after a delay of 100μs, the edge of W rising to VIH ends the protection operations. Block protection verify is achieved by bringing G, E, A0 and A6 to

VIL and A1 to VIH, while W is at VIH and A9 at VID. Under these conditions, reading the data output will yield 01h if the block defined by the inputs on A12-A18 is protected. Any attempt to program or erase a protected block will be ignored by the device.

Block Temporary Unprotection. Any previously protected block can be temporarily unprotected in order to change stored data. The temporary unprotection mode is activated by bringing RP to VID. During the temporary unprotection mode the previously protected blocks are unprotected. A block can be selected and data can be modified by executing the Erase or Program instruction with the

RP signal held at VID. When RP is returned to VIH, all the previously protected blocks are again pro-

tected.

Block Unprotection. All protected blocks can be unprotected on programming equipment to allow updating of bit contents. All blocks must first be protected before the unprotection operation. Block unprotection is activated when A9, G and E are at VID and A12, A15 at VIH. Unprotection is initiated by the edge of W falling to VIL. After a delay of 10ms, the unprotection operation will end. Unprotection verify is achieved by bringing G and E to

VIL while A0 is at VIL, A6 and A1 are at VIH and A9 remains at VID. In these conditions, reading the

output data will yield 00h if the block defined by the inputs A12-A18 has been successfully unprotected. Each block must be separately verified by giving its address in order to ensure that it has been unprotected.

7/33

M29W800AT, M29W800AB

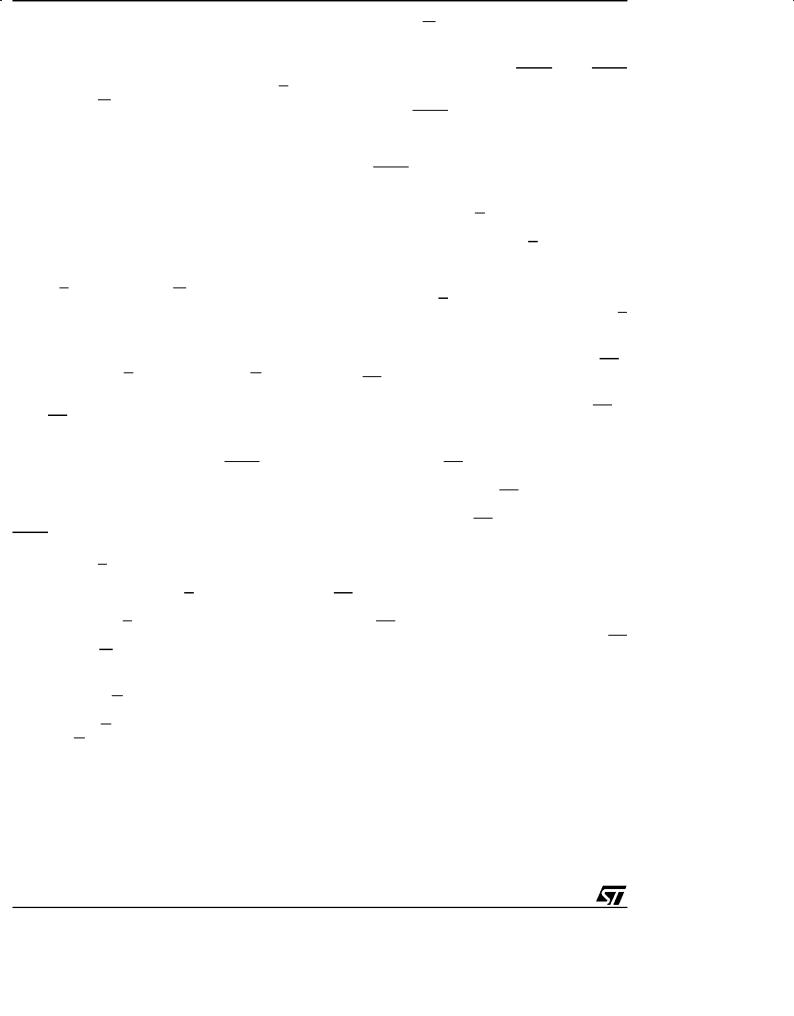

Table 5. User Bus Operations (1)

Operation |

|

E |

G |

W |

RP |

BYTE |

A0 |

A1 |

A6 |

A9 |

A12 |

A15 |

|

Read Word |

|

VIL |

VIL |

VIH |

VIH |

VIH |

A0 |

A1 |

A6 |

A9 |

A12 |

A15 |

|

Read Byte |

|

VIL |

VIL |

VIH |

VIH |

VIL |

A0 |

A1 |

A6 |

A9 |

A12 |

A15 |

|

Write Word |

|

VIL |

VIH |

VIL |

VIH |

VIH |

A0 |

A1 |

A6 |

A9 |

A12 |

A15 |

|

Write Byte |

|

VIL |

VIH |

VIL |

VIH |

VIL |

A0 |

A1 |

A6 |

A9 |

A12 |

A15 |

|

Output Disable |

VIL |

VIH |

VIH |

VIH |

X |

X |

X |

X |

X |

X |

X |

||

Stan-by |

|

VIH |

X |

X |

VIH |

X |

X |

X |

X |

X |

X |

X |

|

Reset |

|

X |

X |

X |

VIL |

X |

X |

X |

X |

X |

X |

X |

|

Block |

|

VIL |

VID |

VIL Pulse |

VIH |

X |

X |

X |

X |

VID |

X |

X |

|

Protection (2,4) |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||

Blocks |

|

VID |

VID |

VIL Pulse |

VIH |

X |

X |

X |

X |

VID |

VIH |

VIH |

|

Unprotection |

(4) |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

Block |

|

|

|

|

|

|

|

|

|

|

|

|

|

Protection |

|

VIL |

VIL |

VIH |

VIH |

X |

VIL |

VIH |

VIL |

VID |

A12 |

A15 |

|

Verify (2,4) |

|

|

|

|

|

|

|

|

|

|

|

|

|

Block |

|

|

|

|

|

|

|

|

|

|

|

|

|

Unprotection |

|

VIL |

VIL |

VIH |

VIH |

X |

VIL |

VIH |

VIH |

VID |

A12 |

A15 |

|

Verify (2,4) |

|

|

|

|

|

|

|

|

|

|

|

|

|

Block |

|

|

|

|

VID |

|

|

|

|

|

|

|

|

Temporary |

|

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

||

Unprotection |

|

|

|

|

|

|

|

|

|

|

|

|

|

Note: 1. X = VIL or VIH.

2.Block Address must be given an A12-A18 bits.

3.See Table 7.

4.Operation performed on programming equipment.

DQ0- |

DQ8- |

DQ15 |

|

DQ7 |

DQ14 |

A±1 |

|

Data |

Data |

Data |

|

Output |

Output |

Output |

|

Data |

Hi-Z |

Address |

|

Output |

Input |

||

|

|||

Data |

Data |

Data |

|

Input |

Input |

Input |

|

Data |

Hi-Z |

Address |

|

Input |

Input |

||

|

|||

Hi-Z |

Hi-Z |

Hi-Z |

|

Hi-Z |

Hi-Z |

Hi-Z |

|

Hi-Z |

Hi-Z |

Hi-Z |

|

X |

X |

X |

|

X |

X |

X |

|

Block |

|

|

|

Protect |

X |

X |

|

Status(3) |

|

|

|

Block |

|

|

|

Protect |

X |

X |

|

Status(3) |

|

|

|

X |

X |

X |

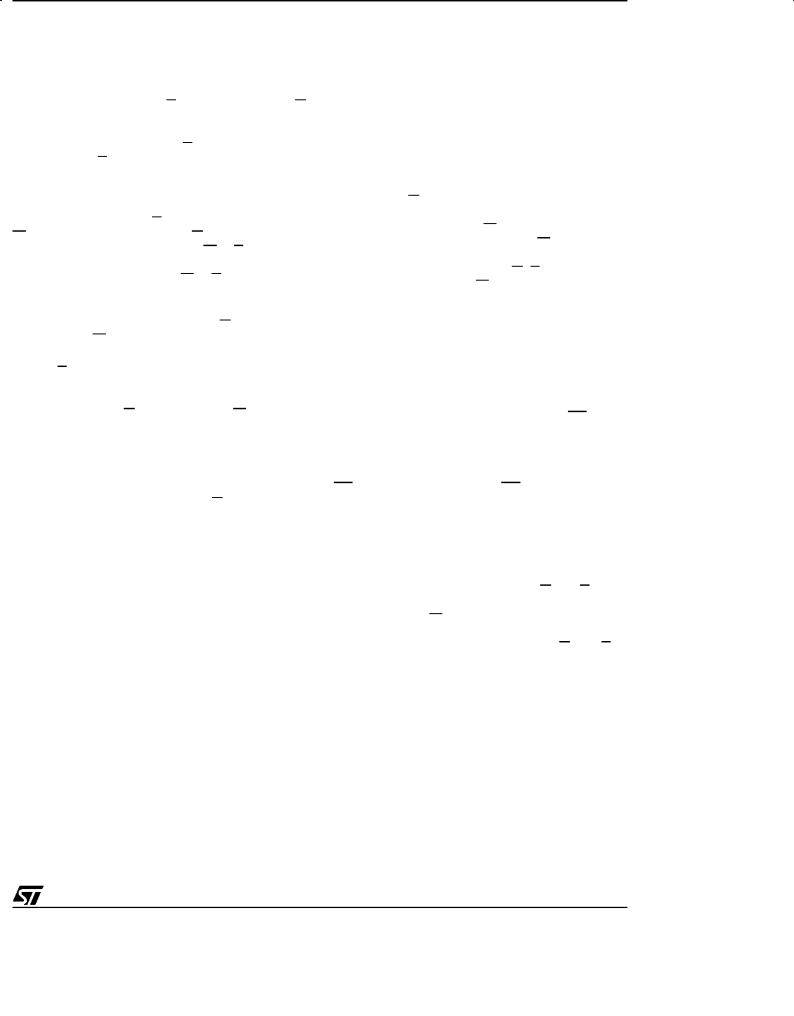

Table 6. Read Electronic Signature (following AS instruction or with A9 = VID)

Org. |

Code |

Device |

E |

G |

W |

BYTE |

A0 |

A1 |

Other |

DQ0- |

DQ8- |

DQ15 |

|

Addresses |

DQ7 |

DQ14 |

A±1 |

||||||||||

|

|

|

|

|

|

|

|

|

|||||

|

Manufact. |

|

VIL |

VIL |

VIH |

VIH |

VIL |

VIL |

Don't Care |

20h |

00h |

0 |

|

|

Code |

|

|||||||||||

Word- |

|

|

|

|

|

|

|

|

|

|

|

||

|

M29W800AT |

VIL |

VIL |

VIH |

VIH |

VIH |

VIL |

Don't Care |

D7h |

00h |

0 |

||

wide |

Device |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Code |

M29W800AB |

VIL |

VIL |

VIH |

VIH |

VIH |

VIL |

Don't Care |

5Bh |

00h |

0 |

|

|

|

Table 7. Read Block Protection with AS Instruction

Code |

E |

G |

W |

A0 |

A1 |

A12-A18 |

Other |

DQ0-DQ7 |

|

Addresses |

|||||||||

|

|

|

|

|

|

|

|

||

Protected Block |

VIL |

VIL |

VIH |

VIL |

VIH |

Block Address |

Don't Care |

01h |

|

Unprotected Block |

VIL |

VIL |

VIH |

VIL |

VIH |

Block Address |

Don't Care |

00h |

8/33

INSTRUCTIONS AND COMMANDS

The Command Interface latches commands written to the memory. Instructions are made up from one or more commands to perform Read Memory Array, Read Electronic Signature, Read Block Protection, Program, Block Erase, Chip Erase, Erase Suspend and Erase Resume. Commands are made of address and data sequences. The instructions require from 1 to 6 cycles, the first or first three of which are always write operations used to initiate the instruction. They are followed by either further write cycles to confirm the first command or execute the command immediately. Command sequencing must be followed exactly. Any invalid combination of commands will reset the device to Read Array. The increased number of cycles has been chosen to assure maximum data security. Instructions are initialised by two initial Coded cycles which unlock the Command Interface. In addition, for Erase, instruction confirmation is again preceded by the two Coded cycles.

Status Register Bits

P/E.C. status is indicated during execution by Data Polling on DQ7, detection of Toggle on DQ6 and DQ2, or Error on DQ5 and Erase Timer DQ3 bits. Any read attempt during Program or Erase command execution will automatically output these five Status Register bits. The P/E.C. automatically sets bits DQ2, DQ3, DQ5, DQ6 and DQ7. Other bits (DQ0, DQ1 and DQ4) are reserved for future use and should be masked. See Tables 10 and 11.

Data Polling Bit (DQ7). When Programming operations are in progress, this bit outputs the complement of the bit being programmed on DQ7. During Erase operation, it outputs a '0'. After completion of the operation, DQ7 will output the bit last programmed or a '1' after erasing. Data Polling is valid and only effective during P/E.C. operation, that is after the fourth W pulse for programming or after the sixth W pulse for erase. It must be performed at the address being programmed or at an address within the block being erased. If all the blocks selected for erasure are protected, DQ7 will be set to '0' for about 100μs, and then return to the previous addressed memory data value. See Figure 13 for the Data Polling flowchart and Figure 12 for the Data Polling waveforms. DQ7 will also flag the Erase Suspend mode by switching from '0' to '1' at the start of the Erase Suspend. In order to

M29W800AT, M29W800AB

monitor DQ7 in the Erase Suspend mode an address within a block being erased must be provided. For a Read Operation in Erase Suspend mode, DQ7 will output '1' if the read is attempted on a block being erased and the data value on other blocks. During Program operation in Erase Suspend Mode, DQ7 will have the same behavior as in the normal program execution outside of the suspend mode.

Toggle Bit (DQ6). When Programming or Erasing operations are in progress, successive attempts to read DQ6 will output complementary data. DQ6 will toggle following toggling of either G, or E when G is low. The operation is completed when two successive reads yield the same output data. The next read will output the bit last programmed or a '1' after erasing. The toggle bit DQ6 is valid only during P/E.C. operations, that is after the fourth W pulse for programming or after the sixth W pulse for Erase. If the blocks selected for erasure are protected, DQ6 will toggle for about 100μs and then return back to Read. DQ6 will be set to '1' if a Read operation is attempted on an Erase Suspend block. When erase is suspended DQ6 will toggle during programming operations in a block different to the block in Erase Suspend. Either E or G toggling will cause DQ6 to toggle. See Figure 14 for Toggle Bit flowchart and Figure 15 for Toggle Bit waveforms.

Table 8. Commands

Hex Code |

Command |

|

00h |

Invalid/Reserved |

|

10h |

Chip Erase Confirm |

|

20h |

Reserved |

|

30h |

Block Erase Resume/Confirm |

|

80h |

Set-up Erase |

|

90h |

Read Electronic Signature/ |

|

Block Protection Status |

||

|

||

A0h |

Program |

|

B0h |

Erase Suspend |

|

F0h |

Read Array/Reset |

9/33

M29W800AT, M29W800AB

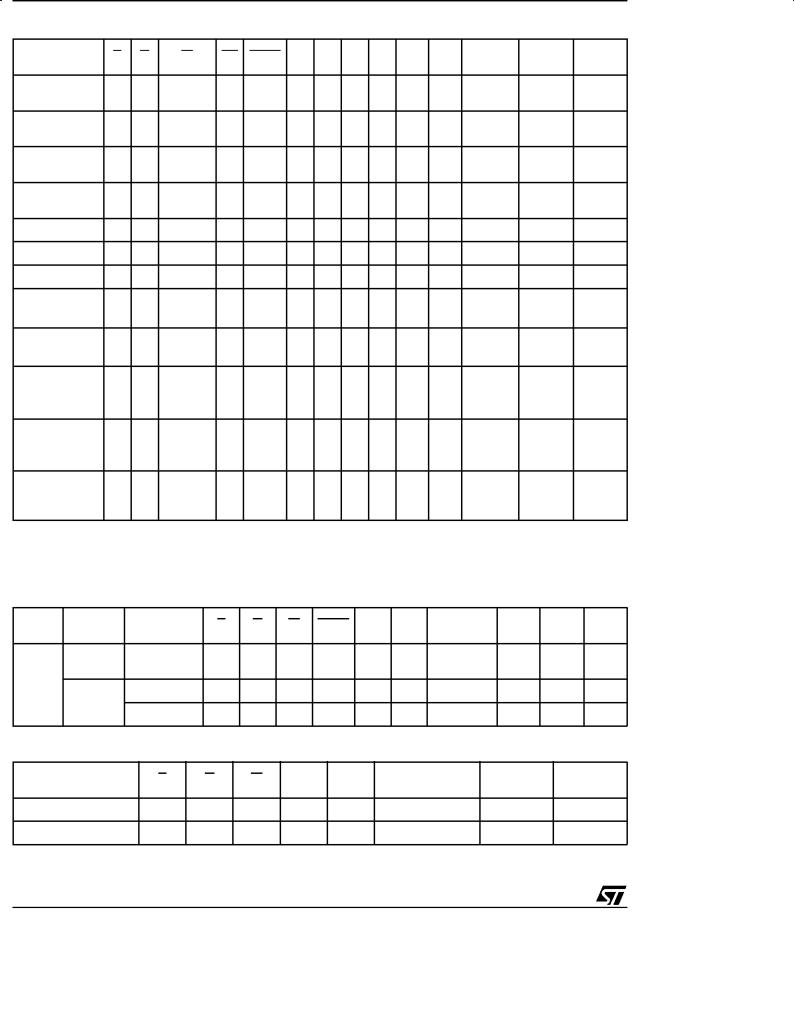

Table 9. Instructions (1)

Mne. |

Instr. |

Cyc. |

1st Cyc. |

2nd Cyc. 3rd Cyc. 4th Cyc. 5th Cyc. 6th Cyc. |

7th Cyc. |

|

|

Addr. (3,7) |

X |

Read Memory Array until a new write cycle is initiated. |

|

|

|

1+ |

|

|

|

|

|

|

Data |

F0h |

|

|

RD (2,4) |

Read/Reset |

|

Byte |

AAAh |

555h |

AAAh |

Memory Array |

|

|||||

|

|

Addr. (3,7) |

|

|

|

|

|

|

3+ |

|

|

|

|

|

|

Word |

555h |

2AAh |

555h |

|

|

|

|

||||

|

|

|

Data |

AAh |

55h |

F0h |

|

|

|

Byte |

AAAh |

555h |

AAAh |

AS (4) |

Auto Select |

3+ |

Addr. (3,7) |

|

|

|

Word |

555h |

2AAh |

555h |

|||

|

|

|

Data |

AAh |

55h |

90h |

|

|

|

Byte |

AAAh |

555h |

AAAh |

|

|

|

Addr. (3,7) |

|

|

|

PG |

Program |

4 |

Word |

555h |

2AAh |

555h |

|

|

|

|

|||

|

|

|

Data |

AAh |

55h |

A0h |

|

|

|

Byte |

AAAh |

555h |

AAAh |

BE |

Block Erase |

6 |

Addr. (3,7) |

|

|

|

Word |

555h |

2AAh |

555h |

|||

|

|

|

Data |

AAh |

55h |

80h |

|

|

|

Byte |

AAAh |

555h |

AAAh |

Read Memory Array until a new write cycle is initiated.

Read Electronic Signature or Block Protection Status until a new write cycle is initiated. See Note 5 and 6.

Program

Address Read Data Polling or Toggle Bit until

Program completes.

Program

Data

AAAh |

555h |

Block |

Additional |

|

|

||

555h |

2AAh |

Address |

Block (8) |

|

|

||

AAh |

55h |

30h |

30h |

AAAh |

555h |

AAAh |

|

CE |

Chip Erase |

6 |

Addr. (3,7) |

|

|

Word |

555h |

||||

|

|

|

Data |

AAh |

|

ES (10) |

Erase |

1 |

Addr. (3,7) |

X |

|

|

|

||||

Suspend |

Data |

B0h |

|||

|

|

||||

|

|

|

|||

ER |

Erase |

1 |

Addr. (3,7) |

X |

|

|

|

||||

Resume |

|

|

|||

|

|

Data |

30h |

||

|

|

|

2AAh |

555h |

555h |

2AAh |

555h |

Note 9 |

55h |

80h |

AAh |

55h |

10h |

|

Read until Toggle stops, then read all the data needed from any Block(s) not being erased then Resume Erase.

Read Data Polling or Toggle Bits until Erase completes or Erase is suspended another time.

Note: 1. Commands not interpreted in this table will default to read array mode.

2.A wait of tPLYH is necessary after a Read/Reset command if the memory was in an Erase or Program mode before starting any new operation (see Tables 15, 16 and Figure 11).

3.X = Don't Care.

4.The first cycles of the RD or AS instructions are followed by read operations. Any number of read cycles can occur after the command cycles.

5.Signature Address bits A0, A1, at VIL will output Manufacturer code (20h). Address bits A0 at VIH and A1, at VIL will output Device code.

6.Block Protection Address: A0, at VIL, A1 at VIH and A15-A18 within the Block will output the Block Protection status.

7.For Coded cycles address inputs A11-A18 are don't care.

8.Optional, additional Blocks addresses must be entered within the erase timeout delay after last write entry, timeout statuscan be verified through DQ3 value (see Erase Timer Bit DQ3 description). When full command is entered, read Data Polling or Toggle bit until Erase is completed or suspended.

9.Read Data Polling, Toggle bits or RB until Erase completes.

10.During Erase Suspend, Read and Data Program functions are allowed in blocks not being erased.

10/33

Loading...

Loading...