Analog Devices AD1671JQ, AD1671JP, AD1671AQ, AD1671AP, AD1671SQ Datasheet

...

a |

Complete 12-Bit 1.25 MSPS |

|

Monolithic A/D Converter |

||

|

|

AD1671 |

FEATURES

Conversion Time: 800 ns 1.25 MHz Throughput Rate

Complete: On-Chip Sample-and-Hold Amplifier and Voltage Reference

Low Power Dissipation: 570 mW

No Missing Codes Guaranteed Signal-to-Noise Plus Distortion Ratio

fIN = 100 kHz: 70 dB

Pin Configurable Input Voltage Ranges

Twos Complement or Offset Binary Output Data 28-Pin DIP and 28-Pin Surface Mount Package Out of Range Indicator

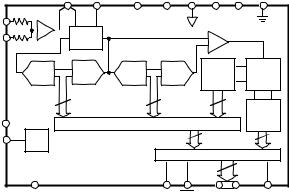

FUNCTIONAL BLOCK DIAGRAM

SHA

OUT UPO/BPO ENCODE VCC ACOM VEE VLOGIC DCOM

AIN1 |

5k |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AIN2 |

|

RANGE |

|

|

|

|

|

|

SELECT |

|

|

|

X4 |

|

|

|

5k |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

3-BIT |

DAC |

3-BIT |

|

|

COARSE |

8-BIT |

|

DAC |

4-BIT |

LADDER |

||||

|

FLASH |

FLASH |

|||||

|

|

|

|

FLASH |

MATRIX |

||

|

|

|

|

|

|

||

|

|

3 |

|

3 |

|

4 |

FINE |

|

|

|

|

|

|

|

4-BIT |

REF IN |

|

|

CORRECTION LOGIC |

|

FLASH |

||

REF OUT |

2.5V |

|

|

|

|

8 |

4 |

REF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD1671 |

|

|

|

LATCHES |

|

|

|

|

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

REF COM |

|

|

OTR |

MSB |

BIT 1 –12 |

DAV |

PRODUCT DESCRIPTION

The AD1671 is a monolithic 12-bit, 1.25 MSPS analog-to- digital converter with an on-board, high performance sample- and-hold amplifier (SHA) and voltage reference. The AD1671 guarantees no missing codes over the full operating temperature range. The combination of a merged high speed bipolar/ CMOS process and a novel architecture results in a combination of speed and power consumption far superior to previously available hybrid implementations. Additionally, the greater reliability of monolithic construction offers improved system reliability and lower costs than hybrid designs.

The fast settling input SHA is equally suited for both multiplexed systems that switch negative to positive full-scale voltage levels in successive channels and sampling inputs at frequencies up to and beyond the Nyquist rate. The AD1671 provides both reference output and reference input pins, allowing the on-board reference to serve as a system reference. An external reference can also be chosen to suit the dc accuracy and temperature drift requirements of the application.

The AD1671 uses a subranging flash conversion technique, with digital error correction for possible errors introduced in the first part of the conversion cycle. An on-chip timing generator provides strobe pulses for each of the four internal flash cycles. A single ENCODE pulse is used to control the converter. The digital output data is presented in twos complement or offset binary output format. An out-of-range signal indicates an overflow condition. It can be used with the most significant bit to determine low or high overflow.

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

The performance of the AD1671 is made possible by using high speed, low noise bipolar circuitry in the linear sections and low power CMOS for the logic sections. Analog Devices’ ABCMOS-1 process provides both high speed bipolar and 2-micron CMOS devices on a single chip. Laser trimmed thin-film resistors are used to provide accuracy and temperature stability.

The AD1671 is available in two performance grades and three temperature ranges. The AD1671J and K grades are available over the 0°C to +70°C temperature range. The AD1671A grade is available over the –40°C to +85°C temperature range. The AD1671S grade is available over the –55°C to +125°C temperature range.

PRODUCT HIGHLIGHTS

The AD1671 offers a complete single chip sampling 12-bit, 1.25 MSPS analog-to-digital conversion function in a 28-pin package.

The AD1671 at 570 mW consumes a fraction of the power of currently available hybrids.

An OUT OF RANGE output bit indicates when the input signal is beyond the AD1671’s input range.

Input signal ranges are 0 V to +5 V unipolar or ±5 V bipolar, selected by pin strapping, with an input resistance of 10 kΩ. The input signal range can also be pin strapped for 0 V to +2.5 V unipolar or ±2.5 V bipolar with an input resistance of 10 MΩ.

Output data is available in unipolar, bipolar offset or bipolar twos complement binary format.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

AD1671–SPECIFICATIONS

DC SPECIFICATIONS (TMIN to TMAX with VCC = +5 V 6 5%, VLOGIC = +5 V 6 10%, VEE = –5 V 6 5%, unless otherwise noted)

|

|

AD1671J/A/S |

|

|

AD1671K |

|

|

Parameter |

Min |

Typ |

Max |

Min |

Typ |

Max |

Units |

RESOLUTION |

12 |

|

|

12 |

|

|

Bits |

CONVERSION TIME |

|

|

800 |

|

|

800 |

ns |

ACCURACY |

|

±1.5 |

±2.5 |

|

±0.7 |

±2.5 |

|

Integral Nonlinearity (INL) |

|

|

LSB |

||||

(S Grade) |

|

|

±3.0 |

|

|

|

|

Differential Nonlinearity (DNL) |

11 |

|

|

12 |

|

|

Bits |

No Missing Codes |

11 Bits Guaranteed |

±9 |

12 Bits Guaranteed |

±9 |

|

||

Unipolar Offsets1 (+25°C) |

|

|

|

|

LSB |

||

Bipolar Zero1 (+25°C) |

|

|

±10 |

|

|

±10 |

LSB |

Gain Error1, 2 (+25°C) |

|

0.1 |

0.35 |

|

0.1 |

0.35 |

% FSR |

TEMPERATURE COEFFICIENTS3 |

|

|

±25 |

|

|

±25 |

ppm/°C |

Unipolar Offset |

|

|

|

|

|||

(S Grade) |

|

|

±25 |

|

|

±25 |

ppm/°C |

Bipolar Zero |

|

|

±25 |

|

|

||

(S Grade) |

|

|

±30 |

|

|

±30 |

ppm/°C |

Gain Error3 |

|

|

±30 |

|

|

||

(S Grade) |

|

|

±40 |

|

|

±20 |

ppm/°C |

Gain Error4 |

|

|

±20 |

|

|

||

POWER SUPPLY REJECTION5 |

|

|

|

|

|

|

|

VCC (+5 V ± 0.25 V) |

|

|

±4 |

|

|

±4 |

LSB |

(S Grade) |

|

|

±5 |

|

|

|

|

VLOGIC (+5 V ± 0.25 V) |

|

|

±4 |

|

|

±4 |

LSB |

(S Grade) |

|

|

±5 |

|

|

|

|

VEE (–5 V ± 0.25 V) |

|

|

±4 |

|

|

±4 |

LSB |

(S Grade) |

|

|

±5 |

|

|

|

|

ANALOG INPUT |

|

|

|

|

|

|

|

Input Ranges |

|

|

|

|

|

|

|

Bipolar |

–2.5 |

|

+2.5 |

–2.5 |

|

+2.5 |

Volts |

|

–5.0 |

|

+5.0 |

–5.0 |

|

+5.0 |

Volts |

Unipolar |

0 |

|

+2.5 |

0 |

|

+2.5 |

Volts |

Input Resistance |

0 |

|

+5.0 |

0 |

|

+5.0 |

Volts |

|

|

|

|

|

|

MΩ |

|

(0 V to +2.5 V or ±2.5 V Range) |

|

10 |

|

|

10 |

|

|

(0 V to +5.0 V or ±5 V Range) |

8 |

10 |

12 |

8 |

10 |

12 |

kΩ |

Input Capacitance |

|

10 |

|

|

10 |

|

pF |

Aperture Delay |

|

15 |

|

|

15 |

|

ns |

Aperture Jitter |

|

20 |

|

|

20 |

|

ps |

INTERNAL VOLTAGE REFERENCE |

|

|

|

|

|

|

|

Output Voltage |

2.475 |

2.5 |

2.525 |

2.475 |

2.5 |

2.525 |

Volts |

Output Current |

|

|

|

|

|

|

|

Unipolar Mode |

|

|

+2.5 |

|

|

+2.5 |

mA |

Bipolar Mode |

|

|

+1.0 |

|

|

+1.0 |

mA |

LOGIC INPUTS |

|

|

|

|

|

|

|

High Level Input Voltage, VIH |

2.0 |

|

|

2.0 |

|

|

Volts |

Low Level Input Voltage, VIL |

|

|

0.8 |

|

|

0.8 |

Volts |

High Level Input Current, IIH (VIN = VLOGIC) |

–10 |

|

+10 |

–10 |

|

+10 |

μA |

Low Level Input Current, ILL (VIN = 0 V) |

–10 |

|

+10 |

–10 |

|

+10 |

μA |

Input Capacitance, CIN |

|

5 |

|

|

5 |

|

pF |

LOGIC OUTPUTS |

|

|

|

|

|

|

|

High Level Output Voltage, VOH (IOH = 0.5 mA) |

2.4 |

|

|

2.4 |

|

|

Volts |

Low Level Output Voltage, VOL (IOL = 1.6 mA) |

|

|

0.4 |

|

|

0.4 |

Volts |

POWER SUPPLIES |

|

|

|

|

|

|

|

Operating Voltages |

|

|

|

|

|

|

|

VCC |

+4.75 |

|

+5.25 |

+4.75 |

|

+5.25 |

Volts |

VLOGIC |

+4.5 |

|

+5.5 |

+4.5 |

|

+5.5 |

Volts |

VEE |

–4.75 |

|

–5.25 |

–4.75 |

|

–5.25 |

Volts |

Operating Current |

|

|

|

|

|

|

|

ICC |

|

55 |

68 |

|

55 |

68 |

mA |

6 |

|

3 |

5 |

|

3 |

5 |

mA |

ILOGIC |

|

|

|||||

IEE |

|

–55 |

–68 |

|

–55 |

–68 |

mA |

POWER CONSUMPTION |

|

570 |

750 |

|

570 |

750 |

mW |

TEMPERATURE RANGE (SPECIFIED) |

|

|

|

|

|

|

°C |

J/K |

0 |

|

+70 |

0 |

|

+70 |

|

A |

–40 |

|

+85 |

–40 |

|

+85 |

°C |

S |

–55 |

|

+125 |

–55 |

|

+125 |

°C |

NOTES

1Adjustable to zero with external potentiometers.

2Includes internal voltage reference error.

3+25°C to TMIN and +25°C to TMAX 4Excludes internal reference drift.

5Change in gain error as a function of the dc supply voltage.

6Tested under static conditions. See Figure 15 for typical curve of ILOGIC vs. load capacitance at maximum tC. Specifications subject to change without notice.

–2– |

REV. B |

|

|

|

|

|

|

|

AD1671 |

|

(TMIN to TMAX with VCC = +5 V 6 5%, VLOGIC = +5 V 6 10%, VEE = –5 V 6 5%, fSAMPLE = 1 MSPS, |

|

|

||||||

AC SPECIFICATIONS flNPUT = 1OO kHz, unless otherwise noted)1 |

|

|

|

|

|

|

|

|

|

|

AD1671J/A/S |

|

AD1671K |

|

|

|

|

Parameter |

Min |

Typ |

Max |

Min |

Typ |

Max |

|

Units |

|

|

|

|

|

|

|

|

|

SIGNAL-TO-NOISE PLUS DISTORTION RATIO |

|

|

|

|

|

|

|

|

(S/N + D) |

|

|

|

|

|

|

|

|

–0.5 dB Input |

68 |

70 |

|

68 |

71 |

|

|

dB |

–20 dB Input |

|

50 |

|

|

51 |

|

|

dB |

|

|

|

|

|

|

|

|

|

EFFECTIVE NUMBER OF BITS (ENOB) |

11.2 |

|

|

11.2 |

|

|

|

Bits |

|

|

|

|

|

|

|

|

|

TOTAL HARMONIC DISTORTION (THD) |

|

–80 |

–75 |

|

–83 |

–75 |

|

dB |

|

|

|

|

|

|

|

|

|

PEAK SPURIOUS OR PEAK HARMONIC COMPONENT |

|

–80 |

–77 |

|

–81 |

–77 |

|

dB |

|

|

|

|

|

|

|

|

|

SMALL SIGNAL BANDWIDTH |

|

12 |

|

|

12 |

|

|

MHz |

|

|

|

|

|

|

|

|

|

FULL POWER BANDWIDTH |

|

2 |

|

|

2 |

|

|

MHz |

|

|

|

|

|

|

|

|

|

INTERMODULATION DISTORTION (IMD)2 |

|

|

|

|

|

|

|

|

2nd Order Products |

|

–80 |

–75 |

|

–80 |

–75 |

|

dB |

3rd Order Products |

|

–85 |

–75 |

|

–85 |

–75 |

|

dB |

|

|

|

|

|

|

|

|

|

NOTES

1fIN amplitude = –0.5 dB (9.44 V p-p) bipolar mode full scale unless otherwise indicated. All measurements referred to a 0 dB ( ±5 V) input signal, unless otherwise indicated.

2fA = 99 kHz, fB = 100 kHz with fSAMPLE = 1 MSPS. Specifications subject to change without notice.

(For all grades TMIN to TMAX with VCC = +5 V 6 5%, VLO61C = +5 V 6 10%, |

|

||||

SWITCHING SPECIFICATIONS VEE = –5 V 6 5%; VIL = 0.8 V, VIH = 2.0 V, VOL = 0.4 V and VOH = 2.4 V) |

|

|

|||

Parameters |

Symbol |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

Conversion Time |

tC |

|

|

800 |

ns |

Sample Rate |

FS |

|

|

1.25 |

MSPS |

ENCODE Pulse Width High (Figure 1a) |

tENC |

20 |

|

50 |

ns |

ENCODE Pulse Width Low (Figure 1b) |

tENCL |

20 |

|

|

ns |

DAV Pulse Width |

tDAV |

150 |

|

300 |

ns |

ENCODE Falling Edge Delay |

tF |

0 |

|

|

ns |

Start New Conversion Delay |

tR |

0 |

|

|

ns |

Data and OTR Delay from DAV Falling Edge |

tDD1 |

20 |

75 |

|

ns |

Data and OTR Valid before DAV Rising Edge |

tSS2 |

20 |

75 |

|

ns |

NOTES

1tDD is measured from when the falling edge of DAV crosses 0.8 V to when the output crosses 0.4 V or 2.4 V with a 25 pF load capacitor on each output pin. 2tSS is measured from when the outputs cross 0.4 V or 2.4 V to when the rising edge of DAV crosses 2.4 V with a 25 pF load capacitor on each output pin.

Specifications subject to change without notice.

|

tENC |

|

|

tC |

|

|

ENCODE |

|

|

|

|

|

|

|

|

|

|

tENCL |

||

|

tC |

|

|

|

||

|

tR |

ENCODE |

|

|

|

|

|

|

|

|

tF |

tR |

|

DAV |

|

t DAV |

|

|

||

|

|

|

|

tDAV |

|

|

|

|

|

|

|

|

|

|

t DD |

tSS |

DAV |

|

|

|

|

|

|

|

|

||

BIT 1–12 |

DATA 0 (PREVIOUS) |

DATA 1 |

|

tDD |

tSS |

|

MSB, OTR |

|

|

||||

|

|

|

BIT 1–12 |

DATA 0 (PREVIOUS) |

|

DATA 1 |

|

|

|

MSB, OTR |

|

||

|

|

|

|

|

|

|

|

Figure 1a. Encode Pulse HIGH |

|

Figure 1b. Encode Pulse LOW |

|

||

REV. B |

–3– |

AD1671

PIN DESCRIPTION

Symbol |

Pin No. |

Type |

Name and Function |

|

|

|

|

|

|

|

|

|

|

ACOM |

27 |

P |

Analog Ground. |

|

|

|

AIN |

22, 23 |

AI |

Analog Inputs, AIN1 and AIN2. The AD1671 can be pin strapped for four input ranges: |

|||

|

|

|

|

Range |

Pin Strap |

Signal Input |

|

|

|

|

0 to +2.5 V, ±2.5 V Connect AIN1 to AIN2 |

AIN1 or AIN2 |

|

|

|

|

|

0 to +5 V, ±5 V |

Connect AIN1 or AIN2 to ACOM |

AIN1 or AIN2 |

BIT 1 (MSB) |

13 |

DO |

Most Significant Bit. |

|

|

|

BIT 2–BIT 11 |

12-3 |

DO |

Data Bits 2 through 11. |

|

||

BIT 12 (LSB) |

2 |

DO |

Least Significant Bit. |

|

|

|

BPO/UPO |

26 |

AI |

Bipolar or Unipolar Configuration Pin. See section on Input Range Connections for details. |

|||

DAV |

16 |

DO |

Data Available Output. The rising edge of DAV indicates an end of conversion and can be used |

|||

|

|

|

|

to latch current data into an external register. The falling edge of DAV can be used to latch |

||

|

|

|

|

previous dam into an external register. |

|

|

DCOM |

19 |

P |

Digital Ground. |

|

|

|

ENCODE |

17 |

DI |

The analog input is sampled on the rising edge of ENCODE. |

|

||

|

|

14 |

DO |

Inverted Most Significant Bit. Provides twos complement output data format. |

||

MSB |

||||||

OTR |

15 |

DO |

Out of Range is Active HIGH when the analog input is out of range. See Output Data Format, |

|||

|

|

|

|

Table III. |

|

|

REF COM |

20 |

AI |

REF COM is the internal reference ground pin. REF COM should be connected as indicated |

|||

|

|

|

|

in the Grounding and Decoupling Rules and Optional External Reference Connection Sections. |

||

REF IN |

24 |

AI |

REF IN is the external 2.5 V reference input. |

|

||

REF OUT |

21 |

AO |

REF OUT is the internal 2.5 V reference output. |

|

||

SHA OUT |

25 |

AO |

No Connect for bipolar input ranges. Connect SHA OUT to BPO/UPO for unipolar input ranges. |

|||

VCC |

28 |

P |

+5 V Analog Power. |

|

|

|

VEE |

1 |

P |

–5 V Analog Power. |

|

|

|

VLOGIC |

18 |

P |

+5 V Digital Power. |

|

|

|

TYPE: AI = Analog Input; AO = Analog Output; DI = Digital Input; DO = Digital Outputs; P = Power.

PIN CONFIGURATION

VEE |

|

|

|

VCC |

1 |

|

28 |

||

BIT 12 (LSB) |

|

|

|

ACOM |

2 |

|

27 |

||

|

|

|

|

|

BIT 11 |

3 |

|

26 |

BPO/UPO |

|

|

|

|

|

|

|

|

|

|

BIT 10 |

4 |

|

25 |

SHA OUT |

BIT 9 |

|

|

|

REF IN |

5 |

|

24 |

||

BIT 8 |

|

|

|

AIN1 |

|

|

|

||

6 |

|

23 |

||

|

|

AD1671 |

|

|

|

|

|

|

|

BIT 7 |

7 |

22 |

AIN2 |

|

BIT 6 |

|

TOP VIEW |

|

|

8 |

(Not to Scale) |

21 |

REF OUT |

|

|

|

|

|

|

BIT 5 |

9 |

|

20 |

REF COM |

|

|

|

|

|

|

|

|

|

|

BIT 4 |

10 |

|

19 |

DCOM |

|

|

|

|

VLOGIC |

|

|

|

|

|

BIT 3 |

11 |

|

18 |

|

|

|

|

|

|

BIT 2 |

12 |

|

17 |

ENCODE |

BIT 1 (MSB) |

|

|

|

|

13 |

|

16 |

DAV |

|

|

|

|

|

|

|

|

|

|

|

MSB |

14 |

|

15 |

OTR |

|

|

|

|

|

–4– |

REV. B |

AD1671

ABSOLUTE MAXIMUM RATINGS*

Parameter |

With Respect to |

Min |

Max |

Units |

|

|

|

|

|

VCC |

ACOM |

–0 5 |

+6.5 |

Volts |

VEE |

ACOM |

–6.5 |

+0.5 |

Volts |

VLOGIC |

DCOM |

–0.5 |

+6.5 |

Volts |

ACOM |

DCOM |

–1.0 |

+1.0 |

Volts |

VCC |

VLOGIC |

–6.5 |

+6.5 |

Volts |

ENCODE |

DCOM |

–0.5 |

VLOGIC + 0.5 |

Volts |

REF IN |

ACOM |

–0.5 |

VCC + 0.5 |

Volts |

AIN |

ACOM |

–11.0 |

+11.0 |

Volts |

BPO/UPO |

ACOM |

–0.5 |

VCC + 0.5 |

Volts |

Junction Temperature |

|

+150 |

°C |

|

Storage Temperature |

–65 |

+150 |

°C |

|

Lead Temperature (10 sec) |

|

+300 |

°C |

|

|

|

|

|

|

*Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

ORDERING GUIDE

|

|

Temperature |

Package |

Model1 |

Linearity |

Range |

Option2, 3 |

|

|

|

|

AD1671JQ |

±2.5 LSB |

0°C to +70°C |

Q-28 |

AD1671KQ |

±2 LSB |

0°C to +70°C |

Q-28 |

AD1671JP |

±2.5 LSB |

0°C to +70°C |

P-28A |

AD1671KP |

±2 LSB |

0°C to +70°C |

P-28A |

AD1671AQ |

±2.5 LSB |

–40°C to +85°C |

Q-28 |

AD1671AP |

±2.5 LSB |

–40°C to +85°C |

P-28A |

AD1671SQ |

±3 LSB |

–55°C to +125°C |

Q-28 |

NOTES

1For details on grade and package offerings screened in accordance with MIL-STD-883, refer to Analog Devices’ Military Products Databook or current AD1671/883 data sheet.

2P = Plastic Leaded Chip Carrier, Q = Cerdip.

3Analog Devices reserves the right to ship side brazed ceramic packages in lieu of cerdip.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1671 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

REV. B |

–5– |

Loading...

Loading...