NSC 5962-9153001VXA, 5962-9153001VYA, 5962-9153001MYA, 5962-9153001MXA, 100324MW8 Datasheet

August 1998

100324

Low Power Hex TTL-to-ECL Translator

General Description

The 100324 is a hex translator, designed to convert TTL logic levels to 100K ECL logic levels. The inputs are compatible with standard or Schottky TTL. A common Enable (E), when LOW, holds all inverting outputs HIGH and holds all true outputs LOW. The differential outputs allow each circuit to be used as an inverting/non-inverting translator, or as a differential line driver. The output levels are voltage compensated over the full −4.2V to −5.7V range.

When the circuit is used in the differential mode, the 100324, due to its high common mode rejection, overcomes voltage gradients between the TTL and ECL ground systems. The VEE and VTTL power may be applied in either order.

The 100324 is pin and function compatible with the 100124 with similar AC performance, but features power dissipation roughly half of the 100124 to ease system cooling requirements.

Features

nPin/function compatible with 100124

nMeets 100124 AC specifications

n50% power reduction of the 100124

nDifferential outputs

n2000V ESD protection

n−4.2V to −5.7V operating range

nStandard Microcircuit Drawing (SMD) 5962-9153001

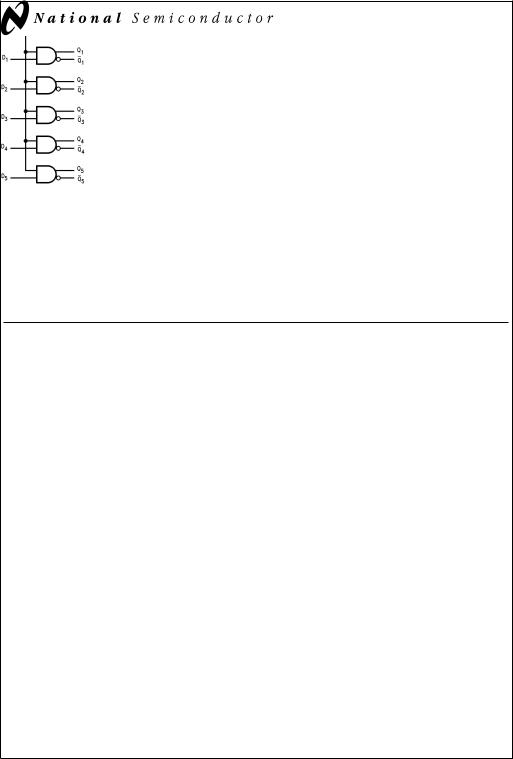

Logic Diagram |

|

|

|

|

|

|

|

|

|

|

Pin Names |

Description |

|

|

|

D0±D5 |

Data Inputs |

|||

|

|

E |

Enable Input |

|||

|

|

Q0±Q5 |

Data Outputs |

|||

|

|

|

|

|

|

|

|

|

Q |

0±Q |

5 |

Complementary |

|

|

|

|

|

|

|

Data Outputs |

|

|

|

|

|

|

|

DS100313-4

Translator ECL-to-TTL Hex Power Low 100324

© 1998 National Semiconductor Corporation |

DS100313 |

www.national.com |

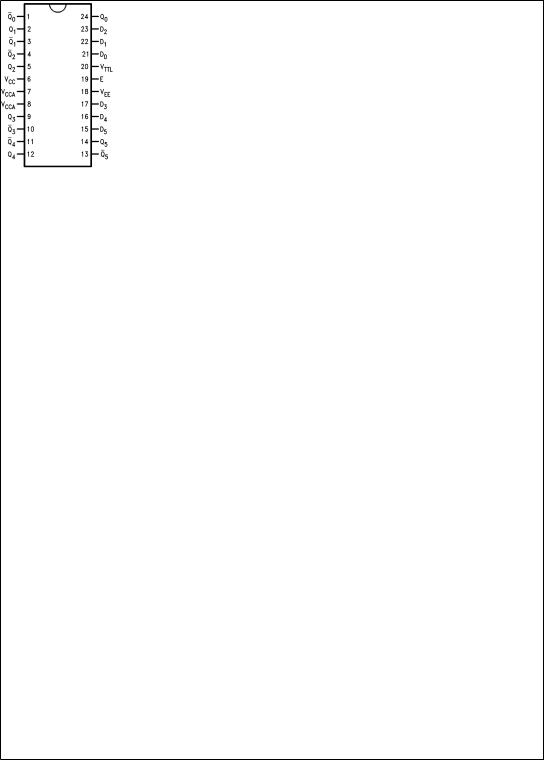

Connection Diagrams

24-Pin DIP |

24-Pin Quad Cerpak |

DS100313-2

DS100313-1

www.national.com |

2 |

Loading...

Loading...