Fairchild Semiconductor DM74LS47N, DM74LS47MX, DM74LS47M Datasheet

October 1988

Revised March 2000

DM74LS47

BCD to 7-Segment Decoder/Driver with

Open-Collector Outputs

General Description

The DM74LS47 accepts four lines of BCD (8421) input data, generates their complements internally and decodes the data with seven AND/OR gates having open-collector outputs to drive indicator segments directly. Each segment output is guaranteed to sink 24 mA in the ON (LOW) state and withstand 15V in the OFF (HIGH) state with a maximum leakage current of 250 μA. Auxiliary inputs provided blanking, lamp test and cascadable zero-suppression functions.

Features

■Open-collector outputs

■Drive indicator segments directly

■Cascadable zero-suppression capability

■Lamp test input

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74LS47M |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|

|

|

DM74LS47N |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

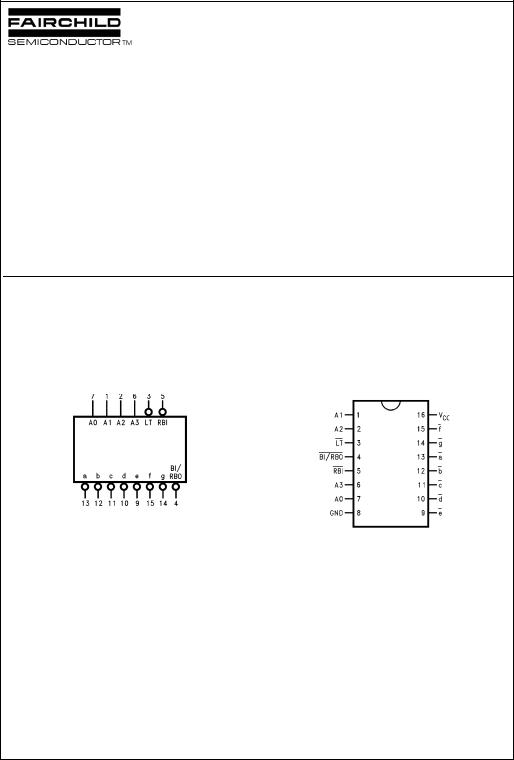

Logic Symbol |

Connection Diagram |

VCC = Pin 16

GND = Pin 8

Pin Descriptions

|

|

|

Pin Names |

Description |

|||||||

|

|

|

|||||||||

|

A0–A3 |

BCD Inputs |

|||||||||

|

|

|

|

|

|

|

|

|

|

Ripple Blanking Input (Active LOW) |

|

|

RBI |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

Lamp Test Input (Active LOW) |

||

|

LT |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

Blanking Input (Active LOW) or |

||

|

BI/RBO |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

Ripple Blanking Output (Active LOW) |

|

|

|

|

|

|

Segment Outputs (Active LOW) (Note 1) |

|||||

|

|

a |

–g |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

Note 1: OC—Open Collector

Outputs Collector-Open with Decoder/Driver Segment-7 to BCD DM74LS47

© 2000 Fairchild Semiconductor Corporation |

DS009817 |

www.fairchildsemi.com |

DM74LS47

Truth Table

Decimal |

|

|

|

|

|

|

|

Inputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Outputs |

|

|

|

|

|

|

|

|

|||||||

|

|

or |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

LT |

|

RBI |

A3 |

A2 |

A1 |

|

A0 |

BI/RBO |

|

a |

b |

c |

|

d |

e |

f |

g |

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

0 |

|

|

|

|

H |

|

|

H |

L |

L |

L |

|

L |

|

|

|

H |

|

|

L |

L |

|

L |

|

L |

|

L |

L |

H |

(Note 2) |

||||||||||

1 |

|

|

|

|

H |

|

|

X |

L |

L |

L |

|

H |

|

|

|

H |

|

H |

L |

|

L |

H |

H |

H |

H |

(Note 2) |

|||||||||||||

2 |

|

|

|

|

H |

|

|

X |

L |

L |

H |

|

L |

|

|

|

H |

|

|

L |

L |

H |

|

L |

|

L |

H |

L |

|

|||||||||||

3 |

|

|

|

|

H |

|

|

X |

L |

L |

H |

|

H |

|

|

|

H |

|

|

L |

L |

|

L |

|

L |

H |

H |

L |

|

|||||||||||

4 |

|

|

|

|

H |

|

|

X |

L |

H |

L |

|

L |

|

|

|

H |

|

H |

L |

|

L |

H |

H |

L |

L |

|

|||||||||||||

5 |

|

|

|

|

H |

|

|

X |

L |

H |

L |

|

H |

|

|

|

H |

|

|

L |

H |

|

L |

|

L |

H |

L |

L |

|

|||||||||||

6 |

|

|

|

|

H |

|

|

X |

L |

H |

H |

|

L |

|

|

|

H |

|

H |

H |

|

L |

|

L |

|

L |

L |

L |

|

|||||||||||

7 |

|

|

|

|

H |

|

|

X |

L |

H |

H |

|

H |

|

|

|

H |

|

|

L |

L |

|

L |

H |

H |

H |

H |

|

||||||||||||

8 |

|

|

|

|

H |

|

|

X |

H |

L |

L |

|

L |

|

|

|

H |

|

|

L |

L |

|

L |

|

L |

|

L |

L |

L |

|

||||||||||

9 |

|

|

|

|

H |

|

|

X |

H |

L |

L |

|

H |

|

|

|

H |

|

|

L |

L |

|

L |

H |

H |

L |

L |

|

||||||||||||

10 |

|

|

H |

|

|

X |

H |

L |

H |

|

L |

|

|

|

H |

|

H |

H |

H |

|

L |

|

L |

H |

L |

|

||||||||||||||

11 |

|

|

|

H |

|

|

X |

H |

L |

H |

|

H |

|

|

|

H |

|

H |

H |

|

L |

|

L |

H |

H |

L |

|

|||||||||||||

12 |

|

|

H |

|

|

X |

H |

H |

L |

|

L |

|

|

|

H |

|

H |

L |

H |

H |

H |

L |

L |

|

||||||||||||||||

13 |

|

|

H |

|

|

X |

H |

H |

L |

|

H |

|

|

|

H |

|

|

L |

H |

H |

|

L |

H |

L |

L |

|

||||||||||||||

14 |

|

|

H |

|

|

X |

H |

H |

H |

|

L |

|

|

|

H |

|

H |

H |

H |

|

L |

|

L |

L |

L |

|

||||||||||||||

15 |

|

|

H |

|

|

X |

H |

H |

H |

|

H |

|

|

|

H |

|

H |

H |

H |

H |

H |

H |

H |

|

||||||||||||||||

|

|

|

|

|

|

X |

|

|

X |

X |

X |

X |

|

X |

|

|

|

L |

|

H |

H |

H |

H |

H |

H |

H |

(Note 3) |

|||||||||||||

|

|

BI |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

H |

|

|

L |

L |

L |

L |

|

L |

|

|

|

L |

|

H |

H |

H |

H |

H |

H |

H |

(Note 4) |

||||||||||||||

|

RBI |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

L |

|

|

X |

X |

X |

X |

|

X |

|

|

|

H |

|

|

L |

L |

|

L |

|

L |

|

L |

L |

L |

(Note 5) |

||||||||||

|

|

LT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 2: BI/RBO is wire-AND logic serving as blanking input (BI) and/or ripple-blanking output (RBO). The blanking out (BI) must be open or held at a HIGH level when output functions 0 through 15 are desired, and ripple-blanking input (RBI) must be open or at a HIGH level if blanking or a decimal 0 is not desired. X = input may be HIGH or LOW.

Note 3: When a LOW level is applied to the blanking input (forced condition) all segment outputs go to a HIGH level regardless of the state of any other input condition.

Note 4: When ripple-blanking input (RBI) and inputs A0, A1, A2 and A3 are LOW level, with the lamp test input at HIGH level, all segment outputs go to a HIGH level and the ripple-blanking output (RBO) goes to a LOW level (response condition).

Note 5: When the blanking input/ripple-blanking output (BI/RBO) is OPEN or held at a HIGH level, and a LOW level is applied to lamp test input, all segment outputs go to a LOW level.

Functional Description

The DM74LS47 decodes the input data in the pattern indicated in the Truth Table and the segment identification illustration. If the input data is decimal zero, a LOW signal applied to the RBI blanks the display and causes a multidigit display. For example, by grounding the RBI of the highest order decoder and connecting its BI/RBO to RBI of the next lowest order decoder, etc., leading zeros will be suppressed. Similarly, by grounding RBI of the lowest order decoder and connecting its BI/RBO to RBI of the next highest order decoder, etc., trailing zeros will be suppressed. Leading and trailing zeros can be suppressed simultaneously by using external gates, i.e.: by driving RBI of a

intermediate decoder from an OR gate whose inputs are BI/RBO of the next highest and lowest order decoders. BI/ RBO also serves as an unconditional blanking input. The internal NAND gate that generates the RBO signal has a resistive pull-up, as opposed to a totem pole, and thus BI/ RBO can be forced LOW by external means, using wiredcollector logic. A LOW signal thus applied to BI/RBO turns off all segment outputs. This blanking feature can be used to control display intensity by varying the duty cycle of the blanking signal. A LOW signal applied to LT turns on all segment outputs, provided that BI/RBO is not forced LOW.

www.fairchildsemi.com |

2 |

Loading...

Loading...