Fairchild Semiconductor DM74LS374WMX, DM74LS374SJX, DM74LS374SJ, DM74LS374CW, IDM29901NC Datasheet

April 1986

Revised March 2000

DM74LS373 • DM74LS374

3-STATE Octal D-Type Transparent Latches

and Edge-Triggered Flip-Flops

General Description

These 8-bit registers feature totem-pole 3-STATE outputs designed specifically for driving highly-capacitive or relatively low-impedance loads. The high-impedance state and increased high-logic level drive provide these registers with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for interface or pull-up components. They are particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

The eight latches of the DM74LS373 are transparent D- type latches meaning that while the enable (G) is HIGH the Q outputs will follow the data (D) inputs. When the enable is taken LOW the output will be latched at the level of the data that was set up.

The eight flip-flops of the DM74LS374 are edge-triggered D-type flip flops. On the positive transition of the clock, the Q outputs will be set to the logic states that were set up at the D inputs.

A buffered output control input can be used to place the eight outputs in either a normal logic state (HIGH or LOW logic levels) or a high-impedance state. In the high-imped- ance state the outputs neither load nor drive the bus lines significantly.

The output control does not affect the internal operation of the latches or flip-flops. That is, the old data can be retained or new data can be entered even while the outputs are OFF.

Features

■Choice of 8 latches or 8 D-type flip-flops in a single package

■3-STATE bus-driving outputs

■Full parallel-access for loading

■Buffered control inputs

■P-N-P inputs reduce D-C loading on data lines

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74LS373WM |

M20B |

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

DM74LS373SJ |

M20D |

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

DM74LS373N |

N20A |

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

DM74LS374WM |

M20B |

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

DM74LS374SJ |

M20D |

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

IDM29901NC |

N20A |

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Flops-Flip Triggered-Edge and Latches Transparent Type-D Octal STATE-3 DM74LS374 • DM74LS373

© 2000 Fairchild Semiconductor Corporation |

DS006431 |

www.fairchildsemi.com |

DM74LS373 • DM74LS374

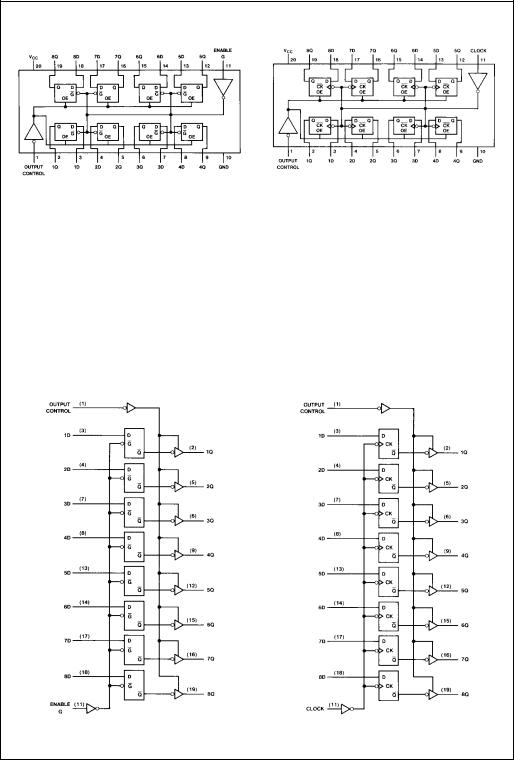

Connection Diagrams

DM74LS373 |

DM74LS374 |

Function Tables

DM74LS373 |

DM74LS374 |

Output |

Enable |

D |

Output |

|

Control |

G |

|||

|

|

|||

|

|

|

|

|

L |

H |

H |

H |

|

L |

H |

L |

L |

|

L |

L |

X |

Q0 |

|

H |

X |

X |

Z |

|

|

|

|

|

Output |

Clock |

D |

Output |

|

Control |

||||

|

|

|

||

|

|

|

|

|

L |

− |

H |

H |

|

L |

− |

L |

L |

|

L |

L |

X |

Q0 |

|

H |

X |

X |

Z |

|

|

|

|

|

H = HIGH Level (Steady State) |

L = LOW Level (Steady State) |

X = Don’t Care |

Z = High Impedance State |

|

− = Transition from LOW-to-HIGH level |

Q0 = The level of the output before steady-state input conditions were established. |

|||

Logic Diagrams |

|

|

|

|

DM74LS373 |

|

|

DM74LS374 |

|

Transparent Latches |

|

Positive-Edge-Triggered Flip-Flops |

||

www.fairchildsemi.com |

2 |

Absolute Maximum Ratings(Note 1)

Supply Voltage |

7V |

Note 1: The “Absolute Maximum Ratings” are those values beyond which |

|

the safety of the device cannot be guaranteed. The device should not be |

|||

Input Voltage |

7V |

operated at these limits. The parametric values defined in the Electrical |

|

Characteristics tables are not guaranteed at the absolute maximum ratings. |

|||

Storage Temperature Range |

−65°C to +150°C |

||

The “Recommended Operating Conditions” table will define the conditions |

|||

Operating Free Air Temperature Range |

0°C to +70°C |

for actual device operation. |

|

|

DM74LS373 Recommended Operating Conditions

Symbol |

Parameter |

|

Min |

Nom |

Max |

Units |

VCC |

Supply Voltage |

|

4.75 |

5 |

5.25 |

V |

VIH |

HIGH Level Input Voltage |

|

2 |

|

|

V |

VIL |

LOW Level Input Voltage |

|

|

|

0.8 |

V |

IOH |

HIGH Level Output Current |

|

|

|

−2.6 |

mA |

IOL |

LOW Level Output Current |

|

|

|

24 |

mA |

tW |

Pulse Width |

Enable HIGH |

15 |

|

|

ns |

|

(Note 3) |

Enable LOW |

15 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

tSU |

Data Setup Time (Note 2) (Note 3) |

5↓ |

|

|

ns |

|

tH |

Data Hold Time (Note 2) (Note 3) |

20↓ |

|

|

ns |

|

TA |

Free Air Operating Temperature |

0 |

|

70 |

°C |

|

Note 2: The symbol (↓) indicates the falling edge of the clock pulse is used for reference.

Note 3: TA = 25°C and VCC = 5V.

DM74LS373 Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Symbol |

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

(Note 4) |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

VI |

Input Clamp Voltage |

VCC = Min, II = −18 mA |

|

|

−1.5 |

V |

|

VOH |

HIGH Level |

VCC = Min, IOH = Max |

2.4 |

3.1 |

|

V |

|

|

Output Voltage |

VIL = Max, VIH = Min |

|

||||

|

|

|

|

|

|||

VOL |

LOW Level |

VCC = Min, IOL = Max |

|

|

|

|

|

|

Output Voltage |

VIL = Max, VIH = Min |

|

0.35 |

0.5 |

V |

|

|

|

IOL = 12 mA, VCC = Min |

|

|

0.4 |

|

|

II |

Input Current @ Max Input Voltage |

VCC = Max, VI = 7V |

|

|

0.1 |

mA |

|

IIH |

HIGH Level Input Current |

VCC = Max, VI = 2.7V |

|

|

20 |

μA |

|

IIL |

LOW Level Input Current |

VCC = Max, VI = 0.4V |

|

|

−0.4 |

mA |

|

IOZH |

Off-State Output Current with |

VCC = Max, VO = 2.7V |

|

|

20 |

μA |

|

|

HIGH Level Output Voltage Applied |

VIH = Min, VIL = Max |

|

|

|||

|

|

|

|

|

|||

IOZL |

Off-State Output Current with |

VCC = Max, VO = 0.4V |

|

|

−20 |

μA |

|

|

LOW Level Output Voltage Applied |

VIH = Min, VIL = Max |

|

|

|||

|

|

|

|

|

|||

IOS |

Short Circuit Output Current |

VCC = Max (Note 5) |

−50 |

|

−225 |

mA |

|

ICC |

Supply Current |

VCC = Max, OC = 4.5V, |

|

24 |

40 |

mA |

|

|

|

Dn, Enable = GND |

|

||||

|

|

|

|

|

|

||

Note 4: All |

typicals are at VCC = 5V, TA = 25°C. |

|

|

|

|

|

Note 5: Not more than one output should be shorted at a time, and the duration should not exceed one second.

DM74LS374 • DM74LS373

3 |

www.fairchildsemi.com |

Loading...

Loading...