Fairchild Semiconductor DM74LS74ASJX, DM74LS74ASJ, DM74LS74AN, DM74LS74AMX, DM74LS74AM Datasheet

...

August 1986

Revised March 2000

DM74LS74A

Dual Positive-Edge-Triggered D Flip-Flops with Preset, Clear and Complementary Outputs

General Description

This device contains two independent positive-edge-trig- gered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly related to the transition time of the rising edge of the clock. The data on the D input may be changed while the clock is LOW or HIGH without affecting the outputs as long as the data setup and hold times are not violated. A low logic level on the preset or clear inputs will set or reset the outputs regardless of the logic levels of the other inputs.

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

DM74LS74AM |

M14A |

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow |

|

|

|

DM74LS85ASJ |

M14D |

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

DM74LS74AN |

N14A |

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

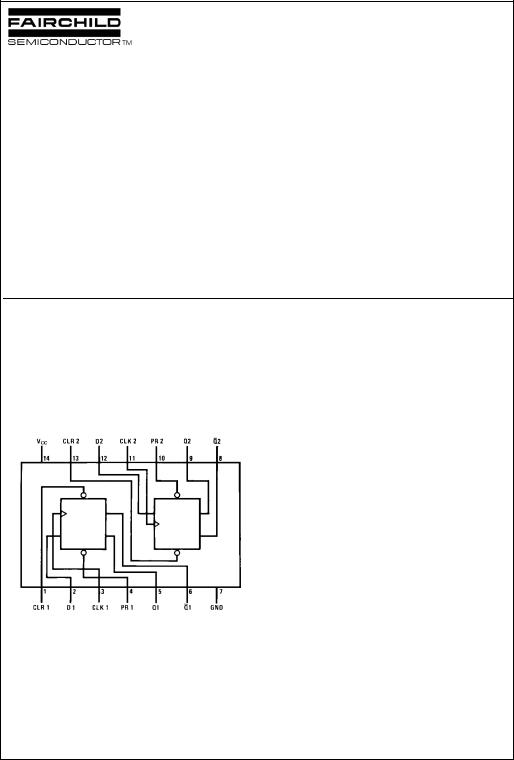

Connection Diagram |

Function Table |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|||||

|

|

|

Inputs |

|

Outputs |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PR |

CLR |

CLK |

|

D |

Q |

|

|

Q |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

L |

H |

X |

|

X |

H |

|

|

L |

||

|

|

H |

L |

X |

|

X |

L |

|

|

H |

||

|

|

L |

L |

X |

|

X |

H (Note 1) |

H (Note 1) |

||||

|

|

H |

H |

− |

|

H |

H |

|

|

L |

||

|

|

H |

H |

− |

|

L |

L |

|

|

H |

||

|

|

H |

H |

L |

|

X |

Q0 |

|

|

|||

|

|

|

|

Q |

0 |

|||||||

|

H = HIGH Logic Level |

|

|

|

|

|

|

|

|

|

||

|

X = Either LOW or HIGH Logic Level |

|

|

|

|

|

|

|

||||

|

L = LOW Logic Level |

|

|

|

|

|

|

|

|

|

||

|

− = Positive-going Transition |

|

|

|

|

|

|

|

||||

|

Q0 = The output logic level of Q before the indicated input conditions were |

|||||||||||

|

established. |

|

|

|

|

|

|

|

|

|

|

|

|

Note 1: This configuration is nonstable; that is, it will not persist when either |

|||||||||||

|

the preset and/or clear inputs return to their inactive (HIGH) level. |

|||||||||||

Outputs Complementary and Clear Preset, with Flops-Flip D Triggered-Edge-Positive Dual DM74LS74A

© 2000 Fairchild Semiconductor Corporation |

DS006373 |

www.fairchildsemi.com |

DM74LS74A

Absolute Maximum Ratings(Note 2)

Supply Voltage |

7V |

Note 2: The “Absolute Maximum Ratings” are those values beyond which |

|

the safety of the device cannot be guaranteed. The device should not be |

|||

Input Voltage |

7V |

operated at these limits. The parametric values defined in the Electrical |

|

Characteristics tables are not guaranteed at the absolute maximum ratings. |

|||

Operating Free Air Temperature Range |

0°C to +70°C |

||

The “Recommended Operating Conditions” table will define the conditions |

|||

Storage Temperature Range |

−65°C to +150°C |

for actual device operation. |

|

|

Recommended Operating Conditions

Symbol |

Parameter |

|

Min |

Nom |

Max |

Units |

|

VCC |

Supply Voltage |

|

4.75 |

5 |

5.25 |

V |

|

VIH |

HIGH Level Input Voltage |

|

2 |

|

|

V |

|

VIL |

LOW Level Input Voltage |

|

|

|

0.8 |

V |

|

IOH |

HIGH Level Output Current |

|

|

|

−0.4 |

mA |

|

IOL |

LOW Level Output Current |

|

|

|

8 |

mA |

|

fCLK |

Clock Frequency (Note 3) |

|

0 |

|

25 |

MHz |

|

fCLK |

Clock Frequency (Note 4) |

|

0 |

|

20 |

MHz |

|

tW |

Pulse Width |

Clock HIGH |

18 |

|

|

|

|

|

(Note 3) |

|

Preset LOW |

15 |

|

|

ns |

|

|

|

|

|

|

|

|

|

|

|

Clear LOW |

15 |

|

|

|

|

|

|

|

|

|

|

|

tW |

Pulse Width |

Clock HIGH |

25 |

|

|

|

|

|

(Note 4) |

|

Preset LOW |

20 |

|

|

ns |

|

|

|

|

|

|

|

|

|

|

|

Clear LOW |

20 |

|

|

|

|

|

|

|

|

|

|

|

tSU |

Setup Time (Note 3)(Note 5) |

|

20− |

|

|

ns |

|

tSU |

Setup Time (Note 4)(Note 5) |

|

25− |

|

|

ns |

|

tH |

Hold Time (Note 5)(Note 6) |

|

0− |

|

|

ns |

|

TA |

Free Air Operating Temperature |

0 |

|

70 |

°C |

||

Note 3: CL = 15 pF, RL = 2 kΩ, TA = 25°C, and VCC = 5V.

Note 4: CL = 50 pF, RL = 2 kΩ, TA = 25°C, and VCC = 5V.

Note 5: The symbol (−) indicates the rising edge of the clock pulse is used for reference.

Note 6: TA = 25°C and VCC = 5V.

www.fairchildsemi.com |

2 |

Loading...

Loading...