Fairchild Semiconductor 74ACT18825SSCX, 74ACT18825SSC, 74ACT18825MTDX, 74ACT18825MTD Datasheet

August 1999

Revised October 1999

74ACT18825

18-Bit Buffer/Line Driver with 3-STATE Outputs

General Description

The ACT18825 contains eighteen non-inverting buffers with 3-STATE outputs designed to be employed as a memory and address driver, clock driver, or bus oriented transmitter/receiver. The device is byte controlled. Each byte has separate 3-STATE control inputs which can be shorted together for full 18-bit operation.

Features

■Broadside pinout allows for easy board layout

■Separate control logic for each byte

■Extra data width for wider address/data paths or buses carrying parity

■Outputs source/sink 24 mA

■TTL-compatible inputs

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

74ACT18825SSC |

MS56A |

56-Lead Shrink Small Outline Package (SSOP), JEDEC MO-118, 0.300” Wide |

|

|

|

74ACT18825MTD |

MTD56 |

56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |

|

|

|

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

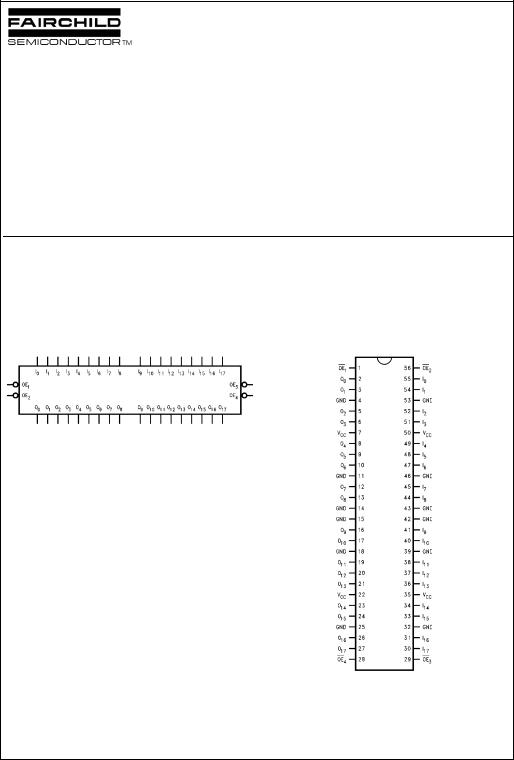

Logic Symbol |

Connection Diagram |

Pin Descriptions

Pin Names |

Description |

||

|

|

|

|

|

|

n |

Output Enable Input (Active LOW) |

|

OE |

||

|

I0–I17 |

Inputs |

|

|

O0–O17 |

Outputs |

|

FACTä, FACT Quiet Seriesä and GTOä are trademarks of Fairchild Semiconductor Corporation.

Outputs STATE-3 with Driver Buffer/Line Bit-18 74ACT18825

© 1999 Fairchild Semiconductor Corporation |

DS0500292 |

www.fairchildsemi.com |

74ACT18825

Functional Description

The ACT18825 contains eighteen non-inverting buffers with 3-STATE standard outputs. The device is byte controlled with each byte functioning identically, but independently of the other. The control pins may be shorted together to obtain full 8-bit operation. The 3-STATE outputs are controlled by an Output Enable (OEn) input for each

byte. When OEn is LOW, the outputs are in 2-state mode.

When OEn is HIGH, the outputs are in the high impedance mode, but this does not interfere with entering new data into the inputs.

Truth Table

|

|

|

|

|

|

Inputs |

|

|

Outputs |

||||

|

|

|

|

|

|

||||||||

Byte 1 (0:8) |

Byte 2 (8:17) |

I0–I 8 |

I9–I 17 |

O0–O 8 |

O9–O 17 |

||||||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

OE1 |

OE2 |

|

OE3 |

OE4 |

|||||||||

|

|

|

|

|

|||||||||

|

L |

L |

|

L |

L |

H |

H |

H |

H |

||||

|

H |

X |

|

L |

L |

X |

L |

Z |

L |

||||

|

X |

H |

|

L |

L |

X |

H |

Z |

H |

||||

|

L |

L |

|

H |

X |

L |

X |

L |

Z |

||||

|

L |

L |

|

X |

H |

H |

X |

H |

Z |

||||

|

H |

H |

|

H |

H |

X |

X |

Z |

Z |

||||

|

L |

L |

|

L |

L |

L |

L |

L |

L |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = HIGH Impedance

Logic Diagram

www.fairchildsemi.com |

2 |

Loading...

Loading...