Fairchild Semiconductor 74AC648SPC, 74AC648SCX, 74AC648SC, 74AC648CW Datasheet

November 1988

Revised August 2000

74AC648

Octal Transceiver/Register with 3-STATE Outputs

General Description

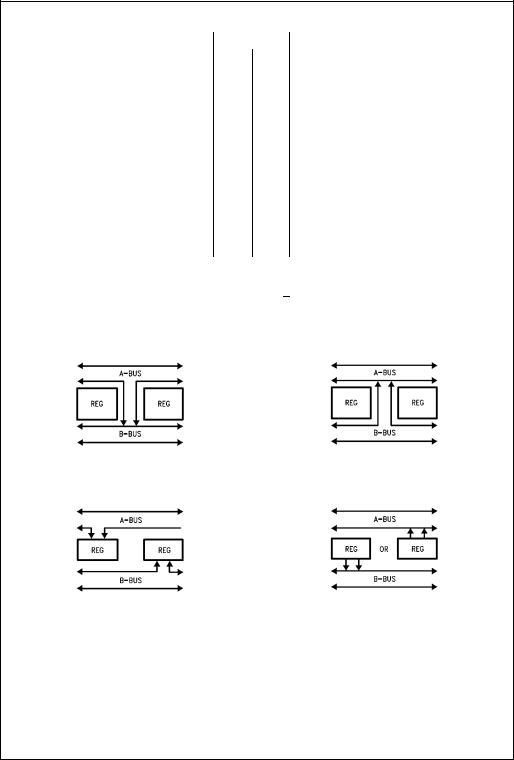

The AC648 consists of registered bus transceiver circuits, with outputs, D-type flip-flops and control circuitry providing multiplexed transmission of data directly from the input bus or from the internal storage registers. Data on the A or B bus will be loaded into the respective registers on the LOW-to-HIGH transition of the appropriate clock pin (CPAB or CPBA). The four fundamental data handling functions available are illustrated in Figure 1, Figure 2, Figure 3, and Figure 4.

Features

■Independent registers for A and B buses

■Multiplexed real-time and stored data transfers

■3-STATE outputs

■300 mil slim dual-in-line package

■Outputs source/sink 24 mA

■Inverted data to output

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

74AC648SC |

M24B |

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

74AC648SPC |

N24C |

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

|

|

|

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

Logic Symbols |

Connection Diagram |

IEEE/IEC

Pin Descriptions

|

|

Pin Names |

Description |

|||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

A |

0–A |

7 |

|

Data Register A Inputs, |

|||

|

|

|

|

|

|

|

|

Data Register A 3-STATE Outputs |

|

|

|

|

|

||||

|

B |

0– |

B |

7 |

|

Data Register B Inputs, |

||

|

|

|

|

|

|

|

|

Data Register B 3-STATE Outputs |

CPAB, CPBA |

Clock Pulse Inputs |

|||||||

SAB, SBA |

Transmit/Receive Inputs |

|||||||

|

|

|||||||

DIR, |

G |

|

Output Enable Inputs |

|||||

|

|

|

|

|

|

|

|

|

FACT is a trademark of Fairchild Semiconductor Corporation.

Outputs STATE-3 with Transceiver/Register Octal 74AC648

© 2000 Fairchild Semiconductor Corporation |

DS010133 |

www.fairchildsemi.com |

74AC648

Function Table

|

|

|

Inputs |

|

|

Data I/O (Note 1) |

Function |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G |

DIR |

CPAB |

CPBA |

SAB |

SBA |

A0–A7 |

B0–B7 |

|

|

|

H |

X |

H or L |

H or L |

X |

X |

|

|

Isolation |

|

H |

X |

|

X |

X |

X |

Input |

Input |

Clock An Data into A Register |

|

H |

X |

X |

|

X |

X |

|

|

Clock Bn Data into B Register |

|

L |

H |

X |

X |

L |

X |

|

|

An to Bn— Real Time (Transparent Mode) |

|

L |

H |

|

X |

L |

X |

Input |

Output |

Clock An Data into A Register |

|

L |

H |

H or L |

X |

H |

X |

|

|

A Register to Bn (Stored Mode) |

|

L |

H |

|

X |

H |

X |

|

|

Clock An Data into A Register and Output to Bn |

|

|

|

|

|

|

|

|

|

|

|

L |

L |

X |

X |

X |

L |

|

|

Bn to An — Real Time (Transparent Mode) |

|

L |

L |

X |

|

X |

L |

Output |

Input |

Clock Bn Data into B Register |

|

L |

L |

X |

H or L |

X |

H |

|

|

B Register to An (Stored Mode) |

|

L |

L |

X |

|

X |

H |

|

|

Clock Bn Data into B Register and Output to An |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Irrelevant

= LOW-to-HIGH Transition

Note 1: The data output functions may be enabled or disabled by various signals at the G and DIR inputs. Data input functions are always enabled; i.e., data at the bus pins will be stored on every LOW-to-HIGH transition of the clock inputs.

Real Time Transfer |

Real Time Transfer |

A-Bus to B-Bus |

B-Bus to A-Bus |

FIGURE 1. |

FIGURE 2. |

Storage from |

Transfer from |

Bus to Register |

Register to Bus |

FIGURE 3. |

FIGURE 4. |

www.fairchildsemi.com |

2 |

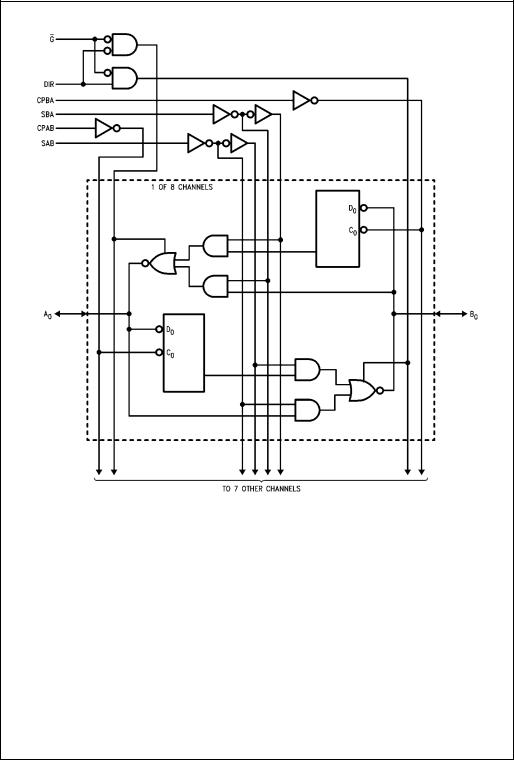

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

74AC648

3 |

www.fairchildsemi.com |

Loading...

Loading...