Fairchild Semiconductor 74ACT16646SSCX, 74ACT16646SSC, 74ACT16646MTDX, 74ACT16646MTD Datasheet

August 1999

Revised October 1999

74ACT16646

16-Bit Transceiver/Register with 3-STATE Outputs

General Description

The ACT16646 contains sixteen non-inverting bidirectional registered bus transceivers providing multiplexed transmission of data directly from the input bus or from the internal storage registers. Each byte has separate control inputs which can be shorted together for full 16-bit operation. The DIR inputs determine the direction of data flow through the device. The CPAB and CPBA inputs load data into the registers on the LOW-to-HIGH transition.

Features

■Independent registers for A and B buses

■Multiplexed real-time and stored data transfers

■Separate control logic for each byte

■16-bit version of the ACT646

■Outputs source/sink 24 mA

■TTL-compatible inputs

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

74ACT16646SSC |

MS56A |

56-Lead Shrink Small Outline Package (SSOP), JEDEC MO-118, 0.300” Wide |

|

|

|

74ACT16646MTD |

MTD56 |

56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |

|

|

|

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

Logic Symbol |

Connection Diagram |

FACTä is a trademark of Fairchild Semiconductor Corporation.

Outputs STATE-3 with Transceiver/Register Bit-16 74ACT16646

© 1999 Fairchild Semiconductor Corporation |

DS500345 |

www.fairchildsemi.com |

74ACT16646

Function Table

|

|

|

Inputs |

|

|

Data I/O (Note 1) |

Output Operation Mode |

||

|

|

|

|

|

|

|

|

|

|

|

G1 |

DIR1 |

CPAB1 |

CPBA1 |

SAB1 |

SBA1 |

A0–7 |

B0–7 |

|

|

H |

X |

H or L |

H or L |

X |

X |

|

|

Isolation |

|

H |

X |

|

X |

X |

X |

Input |

Input |

Clock An Data into A Register |

|

H |

X |

X |

|

X |

X |

|

|

Clock Bn Data Into B Register |

|

L |

H |

X |

X |

L |

X |

|

|

An to Bn—Real Time (Transparent Mode) |

|

L |

H |

|

X |

L |

X |

Input |

Output |

Clock An Data to A Register |

|

L |

H |

H or L |

X |

H |

X |

|

|

A Register to Bn (Stored Mode) |

|

L |

H |

|

X |

H |

X |

|

|

Clock An Data into A Register and Output to Bn |

|

L |

L |

X |

X |

X |

L |

|

|

Bn to An—Real Time (Transparent Mode) |

|

L |

L |

X |

|

X |

L |

Output |

Input |

Clock Bn Data into B Register |

|

L |

L |

X |

H or L |

X |

H |

|

|

B Register to An (Stored Mode) |

|

L |

L |

X |

|

X |

H |

|

|

Clock Bn into B Register and Output to An |

H = HIGH Voltage Level |

X = Immaterial |

L = LOW Voltage Level = LOW-to-HIGH Transition. |

|||||||

Note 1: The data output functions may be enabled or disabled by various signals at the G and DIR inputs. Data input functions are always enabled; i.e., data at the bus pins will be stored on every LOW-to-HIGH transition of the appropriate clock inputs. Also applies to data I/O (A and B: 8-15) and #2 control pins.

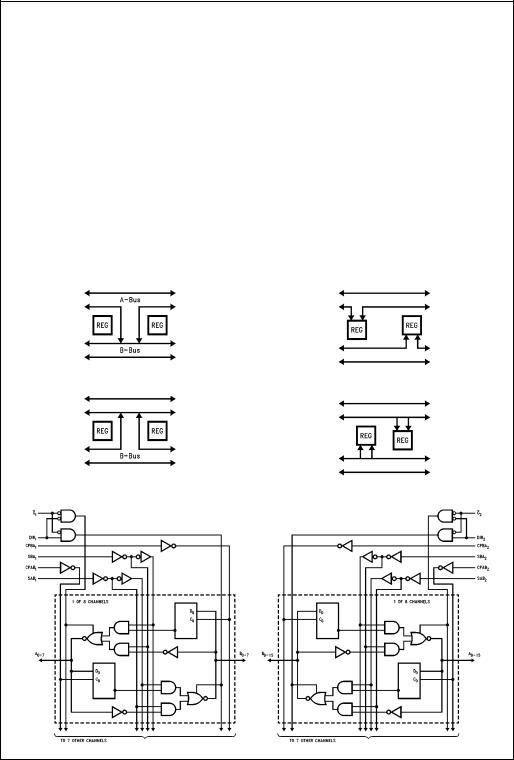

Real Time Transfer |

Storage from |

A-Bus to B-Bus |

Bus to Register |

Real Time Transfer |

Transfer from |

|

B-Bus to A-Bus |

||

Register to Bus |

||

|

Logic Diagram

www.fairchildsemi.com |

2 |

Loading...

Loading...