Analog Devices OP177GS, OP177GP, OP177FP, OP177FS Datasheet

a |

Ultraprecision |

|

Operational Amplifier |

||

|

|

|

|

|

OP177 |

|

|

|

FEATURES

Ultralow Offset Voltage:

TA = 25 C: 25 V Max

Outstanding Offset Voltage Drift: 0.1 V/ C Max

Excellent Open-Loop Gain and Gain Linearity:

12 V/ V Typ

CMRR: 130 dB Min

PSRR: 115 dB Min

Low Supply Current: 2.0 mA Max

Fits Industry Standard Precision Op Amp Sockets

(OP07/OP77)

PIN CONNECTIONS

Epoxy Mini-DIP

(P Suffix)

8-Pin SO (S-Suffix)

V |

TRIM |

1 |

8 |

V |

TRIM |

OS |

|

|

|

OS |

|

|

–IN |

2 |

7 |

V+ |

|

|

+IN |

3 |

6 |

OUT |

|

|

V– |

4 |

5 |

NC |

|

NC = NO CONNECT

GENERAL DESCRIPTION

The OP177 features the highest precision performance of any op amp currently available. Offset voltage of the OP177 is only 25 V max at room temperature. The ultralow VOS of the OP177 combines with its exceptional offset voltage drift (TCVOS) of 0.1 V/°C max to eliminate the need for external VOS adjustment and increases system accuracy over temperature.

The OP177’s open-loop gain of 12 V/ V is maintained over the full ±10 V output range. CMRR of 130 dB min, PSRR of

120 dB min, and maximum supply current of 2 mA are just a few examples of the excellent performance of this operational amplifier. The OP177’s combination of outstanding specifications ensures accurate performance in high closed-loop gain applications.

This low noise bipolar input op amp is also a cost effective alternative to chopper-stabilized amplifiers. The OP177 provides chopper-type performance without the usual problems of high noise, low frequency chopper spikes, large physical size, limited common-mode input voltage range, and bulky external storage capacitors.

The OP177 is offered in the –40°C to +85°C extended industrial temperature ranges. This product is available in 8-pin epoxy DIPs, as well as the space saving 8-pin SmallOutline (SO).

V+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R2A* |

|

(OPTIONA |

R2B* |

|

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

||

|

|

|

|

|

|

C1 |

|

|

|

R7 |

|

|

|

|

|

|

NULL) |

|

|

|

|

||

|

|

|

R1A |

|

R1B |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

2B |

|

|

|

|

|

|

|

|

Q19 |

|

|

|

|

|

|

|

|

Q9 |

|

Q10 |

|

|

|

|

Q7 |

|

Q8 |

|

|

Q11 |

Q12 |

|

R9 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

Q5 |

Q3 |

Q6 |

|

Q4 |

|

|

|

|

OUTPUT |

NONINVERTING |

R3 |

|

|

|

|

Q27 |

C3 |

C2 |

|

Q17 |

R10 |

|

|

|

|

|

|

|

|

Q16 |

|||

INPUT |

|

|

Q1 |

|

|

Q26 |

R5 |

|

|

|

|

|

|

Q21 |

|

|

|

|

|

Q20 |

|||

|

|

Q23 |

|

|

Q25 |

|

|

|

|

||

|

R4 |

Q22 |

Q24 |

|

|

|

|

|

|

|

|

INVERTING |

|

|

Q2 |

|

|

|

Q15 |

|

|||

|

|

|

|

|

|

|

|

|

|||

INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q18 |

|

|

|

|

|

|

|

|

|

|

Q14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q13 |

R6 |

R8 |

|

V– |

|

|

|

|

|

|

|

|

|

|

|

|

*NOTE: |

|

|

|

|

|

|

|

|

|

|

|

R2A AND R2B ARE ELECTRONICALLY ADJUSTED ON CHIP AT FACTORY. |

|

|

|

|||||||

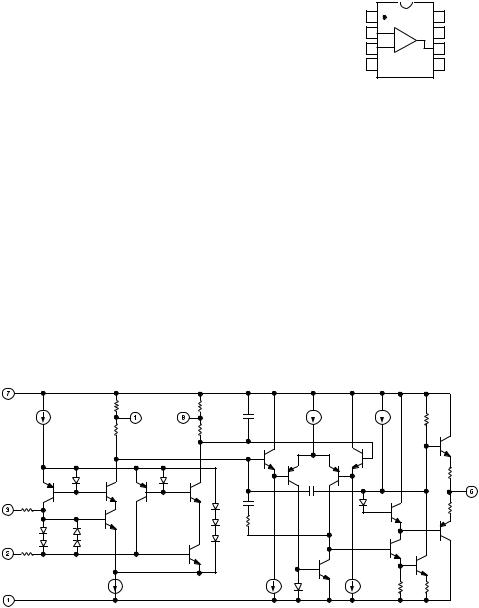

Figure 1. Simplified Schematic

REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 |

www.analog.com |

Fax: 781/326-8703 |

© Analog Devices, Inc., 2002 |

ELECTRICAL CHARACTERISTICS (@ VS = 15 V, TA = 25 C, unless otherwise noted.) |

|

|

OP177 |

||||||

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OP177F |

|

|

OP177G |

|

|

Parameter |

Symbol |

Conditions |

Min |

Typ |

Max |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

INPUT OFFSET |

|

|

|

|

|

|

|

|

µV |

VOLTAGE |

VOS |

|

|

10 |

25 |

|

20 |

60 |

|

LONG-TERM |

|

|

|

|

|

|

|

|

|

INPUT OFFSET |

∆VOS/Time |

|

|

|

|

|

|

|

µV/Mo |

Voltage Stability |

|

|

0.3 |

|

|

0.4 |

|

||

INPUT OFFSET1 |

|

|

|

|

|

|

|

|

|

CURRENT |

IOS |

|

|

0.3 |

1.5 |

|

0.3 |

2.8 |

nA |

INPUT BIAS |

|

|

|

|

|

|

|

|

|

CURRENT |

IB |

|

–0.2 |

1.2 |

2 |

–0.2 |

1.2 |

2.8 |

nA |

INPUT NOISE |

|

fo = 1 Hz to 100 Hz2 |

|

|

|

|

|

|

|

VOLTAGE |

en |

|

118 |

150 |

|

118 |

150 |

nV rms |

|

INPUT NOISE |

|

fo = 1 Hz to 100 Hz2 |

|

|

|

|

|

|

|

CURRENT |

in |

|

3 |

8 |

|

3 |

8 |

pA rms |

|

INPUT |

|

|

|

|

|

|

|

|

|

RESISTANCE |

|

|

|

|

|

|

|

|

|

Differential- |

|

|

|

|

|

|

|

|

MΩ |

Mode3 |

RIN |

|

26 |

45 |

|

18.5 |

45 |

|

|

INPUT |

|

|

|

|

|

|

|

|

|

RESISTANCE |

|

|

|

|

|

|

|

|

GΩ |

COMMON-MODE |

RINCM |

|

|

200 |

|

|

200 |

|

|

INPUT VOLTAGE |

|

|

±13 |

± 14 |

|

± 13 |

± 14 |

|

|

RANGE4 |

IVR |

|

|

|

V |

||||

COMMON-MODE |

|

|

|

|

|

|

|

|

|

REJECTION |

|

VCM = ±13 V |

|

|

|

|

|

|

|

RATIO |

CMRR |

130 |

140 |

|

115 |

140 |

|

dB |

|

|

|

|

|

|

|

|

|

|

|

POWER SUPPLY |

|

|

|

|

|

|

|

|

|

REJECTION |

|

VS = ±3 V to ± 18 V |

|

|

|

|

|

|

|

RATIO |

PSRR |

|

115 |

125 |

|

110 |

120 |

dB |

|

LARGE SIGNAL |

|

RL 2 kΩ, |

|

|

|

|

|

|

|

VOLTAGE GAIN |

AVO |

5000 |

12000 |

|

2000 |

6000 |

|

V/mV |

|

|

|

VO = 610 V5 |

|

|

|

|

|

|

|

OUTPUT |

|

|

|

|

|

|

|

|

|

VOLTAGE |

|

RL 10 kΩ |

±13.5 |

± 14.0 |

|

± 13.5 |

± 14.0 |

|

|

SWING |

VO |

|

|

V |

|||||

|

|

RL 2 kΩ |

±12.5 |

± 13.0 |

|

± 12.5 |

± 13.0 |

|

V |

|

|

RL 1 kΩ |

±12.0 |

± 12.5 |

|

± 12.0 |

± 12.5 |

|

V |

SLEW RATE2 |

SR |

RL 2 kΩ |

0.1 |

0.3 |

|

0.1 |

0.3 |

|

V/µs |

CLOSED-LOOP |

|

|

|

|

|

|

|

|

|

BANDWIDTH2 |

BW |

AVCL = 1 |

0.4 |

0.6 |

|

0.4 |

0.6 |

|

MHz |

OPEN-LOOP |

|

|

|

|

|

|

|

|

|

OUTPUT |

|

|

|

|

|

|

|

|

Ω |

RESISTANCE |

RO |

|

|

60 |

|

|

60 |

|

|

REV. C |

–2– |

|

|

|

|

|

|

|

OP177 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POWER |

|

VS = ±15 V, |

|

|

|

|

|

|

CONSUMPTION |

PD |

|

|

|

|

|

|

|

|

|

No Load |

50 |

60 |

50 |

60 |

|

mW |

|

|

Vs = ±3 V, |

|

|

|

|

|

|

|

|

No Load |

3.5 |

4.5 |

3.5 |

4.5 |

|

mW |

|

|

|

|

|

|

|

|

|

SUPPLY |

|

VS = ±15 V, |

|

|

|

|

|

|

CURRENT |

ISY |

|

|

|

|

|

|

|

|

|

No Load |

1.6 |

2 |

1.6 |

2 |

|

mA |

|

|

|

|

|

|

|

|

|

OFFSET |

|

|

|

|

|

|

|

|

ADJUSTMENT |

|

RP = 20 kΩ |

± 3 |

|

± 3 |

|

|

|

RANGE |

|

|

|

|

mV |

|||

NOTES

1Long-Term Input Offset Voltage Stability refers to the averaged trend line of VOS versus time over extended periods after the first 30 days of operation. Excluding the initial hour of operation, changes in VOS during the first 30 operating days are typically less than 2.0 V.

2Sample tested.

3Guaranteed by design.

4Guaranteed by CMRR test condition.

5To ensure high open-loop gain throughout the ± 10 V output range, AVO is tested at –10 V ≤ VO ≤ 0 V, 0 V ≤ VO ≤ +10 V, and –10 V ≤ VO ≤ +10 V.

Specifications subject to change without notice.

REV. C |

–3– |

OP177–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS (@ VS = 15 V, –40 C ≤ TA ≤ 85 C, unless otherwise noted.)

|

|

|

|

OP177F |

|

|

OP177G |

|

|

Parameter |

Symbol |

Conditions |

Min |

Typ |

Max |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

INPUT OFFSET VOLTAGE |

VOS |

|

|

15 |

40 |

|

20 |

100 |

µV |

AVERAGE INPUT OFFSET |

|

|

|

|

|

|

|

|

µV/°C |

VOLTAGE DRIFT1 |

TCVOS |

|

|

0.1 |

0.3 |

|

0.7 |

1.2 |

|

INPUT OFFSET CURRENT |

IOS |

|

|

0.5 |

2.2 |

|

0.5 |

4.5 |

nA |

AVERAGE INPUT OFFSET |

|

|

|

|

|

|

|

|

pA/°C |

CURRENT DRIFT2 |

TCIOS |

|

|

1.5 |

40 |

|

1.5 |

85 |

|

INPUT BIAS CURRENT |

IB |

|

–0.2 |

2.4 |

4 |

|

2.4 |

± 6 |

nA |

AVERAGE INPUT BIAS |

|

|

|

|

|

|

|

|

pA/°C |

CURRENT DRIFT2 |

TCIB |

|

|

8 |

40 |

|

15 |

60 |

|

INPUT VOLTAGE RANGE3 |

IVR |

|

± 13 |

± 13.5 |

|

±13 |

± 13.5 |

|

V |

COMMON-MODE |

|

VCM = ± 13 V |

|

|

|

|

|

|

|

REJECTION RATIO |

CMRR |

120 |

140 |

|

110 |

140 |

|

dB |

|

|

|

|

|

|

|

|

|

|

|

POWER SUPPLY |

|

VS = ±3 V to ±18 V |

|

|

|

|

|

|

|

REJECTION RATIO |

PSSR |

110 |

120 |

|

106 |

115 |

|

dB |

|

|

|

|

|

|

|

|

|

|

|

LARGE-SIGNAL |

|

RL 2 kΩ, VO = 10 V |

|

|

|

|

|

|

|

VOLTAGE GAIN4 |

AVO |

2000 |

6000 |

|

1000 |

4000 |

|

V/mV |

|

OUTPUT VOLTAGE SWING |

VO |

RL 2/kΩ |

± 12 |

± 13 |

|

±12 |

± 13 |

|

V |

|

|

|

|

|

|

|

|

|

|

POWER CONSUMPTION |

PD |

VS = ±15 V, No Load |

|

60 |

75 |

|

60 |

75 |

mW |

SUPPLY CURRENT |

ISY |

VS = ±15 V, No Load |

|

20 |

2.5 |

|

2 |

2.5 |

mA |

NOTES

1OP177TCVOS is sample tested.

2Guaranteed by endpoint limits.

3Guaranteed by CMRR test condition.

4To ensure high open-loop gain throughout the ± 10 V output range, AVO is tested at –10 V ≤ VO ≤ 0 V, 0 V ≤ VO ≤ +10 V, and –10 V ≤ VO ≤ +10 V.

Specifications subject to change without notice.

200k

50

–

OP177

VO

VO

+

VO VOS = 4000

Figure 2. Typical Offset Voltage Test Circuit

20k

|

|

V+ |

– |

– |

|

INPUT |

OP177 |

OUTPUT |

+ |

+ |

|

|

|

VOS TRIM RANGE IS |

|

|

TYPICALLY 3.0mV |

|

V– |

|

Figure 3. Optional Offset Nulling Circuit

–4– |

REV. C |

Loading...

Loading...