Analog Devices DAC8408GP, DAC8408FT, DAC8408FS, DAC8408FPC, DAC8408FP Datasheet

...

a |

Quad 8-Bit Multiplying CMOS |

|

D/A Converter with Memory |

||

|

|

|

|

|

DAC8408 |

|

|

|

FEATURES

Four DACs in a 28 Pin, 0.6 Inch Wide DIP or 28-Pin JEDEC Plastic Chip Carrier

61/4 LSB Endpoint Linearity

Guaranteed Monotonic DACs Matched to Within 1% Microprocessor Compatible

Read/Write Capability (with Memory) TTL/CMOS Compatible Four-Quadrant Multiplication Single-Supply Operation (+5 V)

Low Power Consumption Latch-Up Resistant Available In Die Form

APPLICATIONS

Voltage Set Points in Automatic Test Equipment Systems Requiring Data Access for Self-Diagnostics Industrial Automation

Multichannel Microprocessor-Controlled Systems Digitally Controlled Op Amp Offset Adjustment Process Control

Digital Attenuators

GENERAL DESCRIPTION

The DAC8408 is a monolithic quad 8-bit multiplying digital-to- analog CMOS converter. Each DAC has its own reference input, feedback resistor, and onboard data latches that feature read/write capability. The readback function serves as memory for those systems requiring self-diagnostics.

A common 8-bit TTL/CMOS compatible input port is used to load data into any of the four DAC data-latches. Control lines DS1, DS2, and A/B determine which DAC will accept data.

Data loading is similar to that of a RAMs write cycle. Data can

be read back onto the same data bus with control line R/W. The DAC8408 is bus compatible with most 8-bit microprocessors, including the 6800, 8080, 8085, and Z80. The DAC8408 operates on a single +5 volt supply and dissipates less than 20 mW. The DAC8408 is manufactured using PMI’s highly stable, thin-film resistors on an advanced oxide-isolated, silicon-gate, CMOS process. PMI’s improved latch-up resistant design eliminates the need for external protective Schottky diodes.

ORDERING INFORMATION1

|

|

|

|

Temperature |

Package |

Model |

INL |

DNL |

Range |

Description |

|

|

|

|

|

|

|

DAC8408GP |

± 1/4 LSB |

± 1/2 LSB |

0°C to +70°C |

28-Pin Plastic DIP |

|

DAC8408ET |

± 1/4 LSB |

± 1/2 LSB |

–40°C to +85°C |

28-Pin Cerdip |

|

DAC8408AT2 |

± 1/4 LSB |

± 1/2 LSB |

–55°C to +125°C |

28-Pin Cerdip |

|

DAC8408FT |

± 1/2 LSB |

± 1 LSB |

–40°C to +85°C |

28-Pin Cerdip |

|

DAC8408BT2 |

± 1/2 LSB |

± 1 |

LSB |

–55°C to +125°C |

28-Pin Cerdip |

DAC8408FPC3 |

± 1/2 LSB |

± 1 |

LSB |

–40°C to +85°C |

28-Contact PLCC |

DAC8408FS |

± 1/2 LSB |

± 1 |

LSB |

–40°C to +85°C |

28-Pin SOL |

DAC8408FP |

± 1/2 LSB |

± 1 |

LSB |

–40°C to +85°C |

28-Pin Plastic DIP |

NOTES

1Burn-in is available on commercial and industrial temperature range parts

in cerdip, plastic DIP, and TO-can packages. For outline information see Package Information section.

2For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

3For availability and burn-in information on SO and PLCC packages, contact your local sales office.

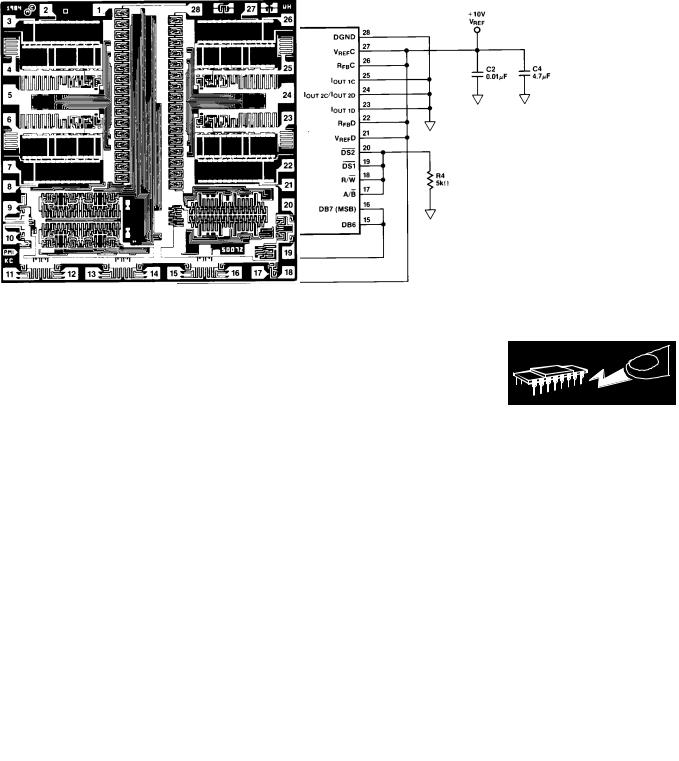

FUNCTIONAL BLOCK DIAGRAM

DAC8408

REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

DAC8408

ELECTRICAL CHARACTERISTICS (@ VDD = +5 V; VREF = 610 V; VOUTA, B, C, D = 0 V; TA = –558C to +1258C apply for DAC8408AT/BT, TA = –408C to +858C apply for DAC8408ET/FT/FP/FPC/FS; TA = 08C to +708C apply for DAC8408GP, unless otherwise noted.

Specifications apply for DAC A, B, C, & D.)

|

|

|

|

DAC8408 |

|

|

Parameter |

Symbol |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

STATIC ACCURACY |

|

|

|

|

|

|

Resolution |

N |

|

8 |

|

±1/4 |

Bits |

Nonlinearity1, 2 |

INL |

DAC8408A/E/G |

|

|

LSB |

|

|

|

DAC8408B/F/H |

|

|

±1/2 |

LSB |

Differential |

DNL |

DAC8408A/E/G |

|

|

±1/2 |

LSB |

Nonlinearity |

|

DAC8408B/F/H |

|

|

±1 |

LSB |

Gain Error |

GFSE |

(Using Internal RFB) |

|

|

±1 |

LSB |

Gain Tempco3, 6 |

TCGFS |

|

|

±2 |

±40 |

ppm/°C |

Power Supply Rejection |

|

|

|

|

|

|

( VDD = ±10%) |

PSR |

|

|

|

0.001 |

%FSR/% |

IOUT 1A, B, C, D |

|

TA =+25°C |

|

|

±30 |

|

Leakage Current13 |

ILKG |

|

|

nA |

||

|

|

TA = Full Temperature Range |

|

|

±100 |

nA |

REFERENCE INPUT |

|

|

|

|

±20 |

|

Input Voltage Range |

|

|

|

|

V |

|

Input Resistance Match4 |

|

RA, B, C, D |

|

|

±1 |

% |

Input Resistance |

RIN |

|

6 |

10 |

14 |

kΩ |

DIGITAL INPUTS |

|

|

|

|

|

|

Digital Input Low |

VIL |

|

|

|

0.8 |

V |

Digital Input High |

VIH |

TA = +25°C |

2.4 |

±0.01 |

±1.0 |

V |

Input Current5 |

|

|

μA |

|||

Input Capacitance6 |

IIN |

TA = Full Temperature Range |

|

|

±10.0 |

μA |

CIN |

|

|

|

8 |

pF |

|

DATA BUS OUTPUTS |

|

|

|

|

|

|

Digital Output Low |

VOL |

16 mA Sink |

|

|

0.4 |

V |

Digital Output High |

VOH |

400 μA Source |

4 |

|

|

V |

Output Leakage Current |

ILKG |

TA = +25°C |

|

±0.005 |

±1.0 |

μA |

|

|

TA = Full Temperature Range |

|

±0.075 |

±10.0 |

μA |

DAC OUTPUTS6 |

|

|

|

|

|

|

Propagation Delay7 |

tPD |

|

|

150 |

180 |

ns |

Settling Time11,12 |

tS |

|

|

190 |

250 |

ns |

Output Capacitance |

COUT |

DAC Latches All “0s” |

|

|

30 |

pF |

|

|

DAC Latches All “1s” |

|

|

50 |

pF |

AC Feedthrough |

FT |

(20 Vp-p @ F = 100 kHz) |

54 |

|

|

dB |

SWITCHING CHARACTERISTICS6, 10 |

|

TA = +25°C |

|

|

|

|

Write to Data Strobe Time |

tDS1 or |

90 |

|

|

ns |

|

|

tDS2 |

TA = Full Temperature Range |

145 |

|

|

ns |

Data Valid to Strobe Set-Up Time |

tDSU |

TA = +25°C |

150 |

|

|

ns |

Data Valid to Strobe Hold Time |

tDH |

TA = Full Temperature Range |

175 |

|

|

ns |

|

10 |

|

|

ns |

||

DAC Select to Strobe Set-Up Time |

tAS |

|

0 |

|

|

ns |

DAC Select to Strobe Hold Time |

tAH |

|

0 |

|

|

ns |

Write Select to Strobe Set-Up Time |

tWSU |

|

0 |

|

|

ns |

Write Select to Strobe Hold Time |

tWH |

TA = +25°C |

0 |

|

|

ns |

Read to Data Strobe Width |

tRDS |

220 |

|

|

ns |

|

|

|

TA = Full Temperature Range |

350 |

|

|

ns |

Data Strobe to Output Valid Time |

tCO |

TA = +25°C |

320 |

|

|

ns |

|

|

TA = Full Temperature Range |

430 |

|

|

ns |

Output Data to Deselect Time |

tOTD |

TA = +25°C |

200 |

|

|

ns |

Read Select to Strobe Set-Up Time |

tRSU |

TA = Full Temperature Range |

270 |

|

|

ns |

|

0 |

|

|

ns |

||

Read Select to Strobe Hold Time |

tRH |

|

0 |

|

|

ns |

Specifications subject to change without notice.

–2– |

REV. A |

DAC8408

ELECTRICAL CHARACTERISTICS @ VDD = +5 V; VREF = 610 V; VOUTA, B, C, D = 0 V; TA = –558C to +1258C apply for DAC8408AT/BT, TA = –408C to +858C apply for DAC8408ET/FT/FP/FPC/FS; TA = 08C to +708C apply for DAC8408GP, unless otherwise noted.

Specifications apply for DAC A, B, C, & D. Continued

|

|

|

|

DAC8408 |

|

Parameter |

Symbol |

Conditions |

Min |

Typ Max |

Units |

|

|

|

|

|

|

POWER SUPPLY |

|

|

|

|

|

Voltage Range |

VDD |

|

4.5 |

5.5 |

V |

Supply Current8 |

IDD |

TA = +25°C |

|

50 |

μA |

Supply Current9 |

IDD |

|

1.0 |

mA |

|

|

|

TA = Full Temperature Range |

|

1.5 |

mA |

NOTES

1This is an end-point linearity specification.

2Guaranteed to be monotonic over the full operating temperature range.

3ppm/°C of FSR (FSR = Full Scale Range = VREF-1 LSB.) 4Input Resistance Temperature Coefficient = +300ppm/°C.

5Logic Inputs are MOS gates. Typical input current at +25°C Is less than 10 nA. 6Guaranteed by design.

7From Digital Input to 90% of final analog output current. 8All Digital Inputs “0” or VDD.

9All Digital Inputs VIH or VIL.

10See Timing Diagram.

11Digital Inputs = 0 V to VDD or VDD to 0 V.

12Extrapolated: tS (1/2 LSB) = tPD + 6.2τ where τ = the measured first time constant of the final RC decay.

13All Digital Inputs = 0 V; VREF = +10 V. Specifications subject to change without notice.

PIN CONNECTIONS

DAC8408

TOP VIEW

(Not to Scale)

ABSOLUTE MAXIMUM RATINGS

(TA = +25°C, unless otherwise noted.)

VDD to IOUT 2A, IOUT 2B, IOUT 2C, IOUT 2D . . . . . . . . . . 0 V, +7 V VDD to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V, +7 V

IOUT 1A, IOUT 1B,

IOUT 1C, IOUT 1D to DGND . . . . . . . . . |

–0.3 V to VDD +0.3 V |

|

RFBA, RFBB, RFBC, RFBD to IOUT . . . . . |

. . . . . . . . . . . . ±25 V |

|

IOUT 2A, IOUT 2B, |

|

|

IOUT 2C, IOUT 2D to DGND . . . . . . . . . |

–0.3 V to VDD + 0.3 |

V |

DB0 through DB7 to DGND . . . . . . . . |

–0.3 V to VDD + 0.3 |

V |

Control Logic |

|

|

Input Voltage to DGND . . . . . . . . . . |

–0.3 V + VDD + 0.3 |

V |

VREFA, VREFB, VREFC, VREFD to |

±25 |

|

IOUT 2A, IOUT 2B, IOUT 2C, IOUT 2D . . . . . |

V |

|

Operating Temperature Range

Commercial Grade (GP) . . . . . . . . . . . . . . . . 0°C to +70°C Industrial Grade (ET, FT, FP, FPC, FS) . –40°C to +85°C Military Grade (AT, BT) . . . . . . . . . . . . . .–55°C to +125°C Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . +150°C Storage Temperature . . . . . . . . . . . . . . . . . . .–65°C to +150°C Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . . +300°C

Package Type |

uJA* |

uJC |

Units |

28-Pin Hermetic DIP (T) |

55 |

10 |

°C/W |

28-Pin Plastic DIP (P) |

53 |

27 |

°C/W |

28-Pin SOL (S) |

68 |

23 |

°C/W |

28-Contact PLCC (PC) |

66 |

29 |

°C/W |

*θJA is specified for worst case mounting conditions, i.e., θJA is specified for device in socket for cerdip and P-DIP packages; θJA is specified for device soldered to printed circuit board for SOL and PLCC packages.

CAUTION

1.Do not apply voltages higher than VDD +0.3 V or less than –0.3 V potential on any terminal except VREF and RFB.

2.The digital control inputs are diode-protected; however, permanent damage may occur on unconnected inputs from high energy electrostatic fields. Keep in conductive foam at all times until ready to use.

3.Use proper antistatic handling procedures.

4.Absolute Maximum Ratings apply to both packaged devices and DICE. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device.

REV. A |

–3– |

DAC8408

|

Burn-in Circuit |

|

|

CAUTION |

|

|

|

|

|

|

|

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily |

|

|

|

|

WARNING! |

||

accumulate on the human body and test equipment and can discharge without detection. |

|

||

Although the DAC8408 features proprietary ESD protection circuitry, permanent damage may |

|

|

|

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD |

|

ESD SENSITIVE DEVICE |

|

precautions are recommended to avoid performance degradation or loss of functionality. |

|

||

|

|

||

|

|

|

|

|

DICE CHARACTERISTICS |

|

|

1. |

VDD |

15. |

DB6 |

2. |

VREFA |

16. |

DB7 (MSB) |

3. |

RFBA |

17. |

A/B |

4. |

IOUT 1A |

18. |

R/W |

5. |

IOUT 2A/IOUT 2B |

19. |

DS1 |

6. |

IOUT 1B |

20. |

DS2 |

7. |

RFBB |

21. |

VREFD |

8. |

VREFB |

22. |

RFBD |

9. |

DB0 (LSB) |

23. |

IOUT 1D |

10. |

DB1 |

24. |

IOUT 2C/IOUT 2D |

11. |

DB2 |

25. |

IOUT 1C |

12. |

DB3 |

26. |

RFBC |

13. |

DB4 |

27. |

VREFC |

14. DB5 |

28. DGND |

||

DIE SIZE 0.130 × 0.124 inch, 16,120 sq. mils (3.30 × 3.15 mm, 10.4 sq. mm)

–4– |

REV. A |

DAC8408

WAFER TESTLIMITS at VDD = +5 V; VREF = 610 V; VOUTA, B, C, D = 0 V; TA = +258C, unless otherwise noted. Specifications apply for

DAC A, B, C, & D.

|

|

|

DAC8408G |

|

Parameter |

Symbol |

Conditions |

Limits |

Units |

|

|

|

|

|

STATIC ACCURACY |

|

|

|

|

Resolution |

N |

|

8 |

Bits min |

Nonlinearity1 |

INL |

|

±1/2 |

LSB max |

Differential Nonlinearity |

DNL |

|

±1 |

LSB max |

Gain Error |

GFSE |

Using Internal RFB |

±1 |

LSB max |

Power Supply Rejection |

PSR |

Using Internal RFB |

0.001 |

%FSR/% max |

( VDD = ±10%)2 |

|

|

±30 |

|

IOUT 1A, B, C, D Leakage Current |

ILKG |

All Digital Inputs = 0 V |

nA max |

|

|

VREF = +10 V |

|

|

|

REFERENCE INPUT |

|

|

|

kΩ min/max |

Reference Input |

RIN |

|

6/14 |

|

Resistance3 |

|

|

±1 |

|

Input Resistance Match |

RIN |

|

% max |

|

DIGITAL INPUTS |

|

|

|

|

Digital Input Low |

VIL |

|

0.8 |

V max |

Digital Input High |

VIH |

|

2.4 |

V min |

Input Current4 |

IIN |

|

±1.0 |

μA max |

DATA BUS OUTPUTS |

|

|

|

|

Digital Output Low |

VOL |

1.6 mA Sink |

0.4 |

V max |

Digital Output High |

VOH |

400 μA Source |

4 |

V min |

Output Leakage Current |

ILKG |

|

±1.0 |

μA max |

POWER SUPPLY |

|

|

|

μA max |

Supply Current5 |

IDD |

|

50 |

|

Supply Current6 |

IDD |

|

1.0 |

mA max |

NOTES

1This is an endpoint linearity specification.

2FSR is Full Scale Range = VREF –1 LSB.

3Input Resistance Temperature Coefficient approximately equals +300 ppm/°C. 4Logic inputs are MOS gates.Typical input current at +25°C is less than 10 nA. 5All Digital Inputs are either “0” or VDD.

6All Digital Inputs are either VIH or VIL.

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

REV. A |

–5– |

Loading...

Loading...