Analog Devices EVAL-AD1959EB, AD1959YRSRL, AD1959YRS Datasheet

a |

PLL/Multibit - DAC |

|

|

|

|

|

|

AD1959 |

|

|

|

FEATURES

5 V Stereo Audio DAC System Accepts 16-Bit/20-Bit/24-Bit Data Supports 24 Bits, 192 kHz Sample Rate

Accepts a Wide Range of Sample Rates Including:

32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, and 192 kHz Multibit Sigma-Delta Modulator with Data Directed

Scrambling

Single-Ended Output for Easy Application –94 dB THD + N

108 dB SNR and Dynamic Range

75 dB Stopband Attenuation Clickless Volume Control

Hardware and Software Controllable Clickless Mute Serial (SPI) Control for: Serial Mode, Number of Bits, Sample Rate, Volume, Mute, De-Emphasis and

Output Phase

Digital De-Emphasis Processing for 32 kHz, 44.1 kHz, and 48 kHz Sample Rates

Programmable Dual Fractional-N PLL Clock Generator 27 MHz Master Clock Input/Oscillator

Generated System Clocks

SCLK0: 33.8688 MHz

SCLK1: 384/256 fS (32 kHz/44.1 kHz/48 kHz/88.2 kHz/ 96 kHz)

SCLK2: 512 fS (32 kHz/44.1 kHz/48 kHz/88.2 kHz/ 96 kHz)/22.5792 MHz

Better than 100 ps RMS Clock Jitter

Flexible Serial Data Port with Right-Justified, LeftJustified, I2S-Compatible, and DSP Serial Port Modes

28-Lead SSOP Plastic Package

APPLICATIONS

DVD, CD, Home Theater Systems, Automotive Audio

Systems, Sampling Musical Keyboards, Digital Mixing

Consoles, Digital Audio Effects Processors

PRODUCT OVERVIEW

The AD1959 is a complete high-performance single-chip stereo digital audio playback system. It is comprised of a multibit sigmadelta modulator, digital interpolation filters, and analog output drive circuitry with an on-board dual PLL clock generator.

Other features include an on-chip stereo attenuator and mute, programmed through an SPI-compatible serial control port. The AD1959 is fully compatible with all known DVD formats including 96 kHz and 192 kHz sample frequencies and 24 bits. It also is backwards-compatible by supporting 50 s/15 s digital de-emphasis for “redbook” compact discs, as well as de-emphasis at 32 kHz and 48 kHz sample rates.

The AD1959 has a simple but flexible serial data input port that allows for glueless interconnection to a variety of ADCs, DSP chips, AES/EBU receivers, and sample rate converters. The AD1959 can be configured in left-justified, I2S, right-justified, or DSP serial-port-compatible modes. It can support 16, 20, and 24 bits in all modes. The AD1959 accepts serial audio data in MSB first, two’s-complement format, and operates from a single 5 V power supply. It is fabricated on a single monolithic integrated circuit and housed in a 28-lead SSOP package for operation over the temperature range –40°C to +105°C.

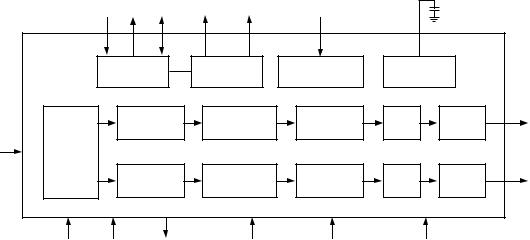

FUNCTIONAL BLOCK DIAGRAM

16-/20-/24- BIT DIGITAL

DATA INPUT 3

LOOP |

CLOCK |

CONTROL DATA |

|

XIN XOUT MCLK FILTERS |

OUTPUTS |

INPUT |

|

|

|||

|

|

|

|

2 |

3 |

3 |

|

|

|

AD1959 |

OSC |

|

PLL |

SERIAL CONTROL |

VOLTAGE |

|

|

|

|

CIRCUIT |

INTERFACE |

REFERENCE |

|

|

|||

|

|

|

|

|

||||

|

|

ATTEN/MUTE |

|

8 FS |

MULTIBIT |

DAC |

OUTPUT |

|

|

|

|

SIGMA-DELTA |

L |

||||

|

|

|

INTERPOLATOR |

MODULATOR |

|

BUFFER |

|

|

SERIAL |

|

|

|

|

|

|

|

ANALOG |

DATA |

|

|

|

|

|

|

|

|

INTERFACE |

|

|

|

|

|

|

|

OUTPUTS |

|

|

ATTEN/MUTE |

|

8 FS |

MULTIBIT |

DAC |

OUTPUT |

R |

|

|

|

SIGMA-DELTA |

|||||

|

|

|

INTERPOLATOR |

MODULATOR |

|

BUFFER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

2 |

3 |

|

|

RESET |

MUTE |

ZERO FLAG |

|

PLL SUPPLY |

DIGITAL SUPPLY |

ANALOG SUPPLY |

|

|

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 |

www.analog.com |

Fax: 781/326-8703 |

© Analog Devices, Inc., 2001 |

AD1959–SPECIFICATIONS

TEST CONDITIONS UNLESS OTHERWISE NOTED |

||

Supply Voltages (AVDD, DVDD) 5.0 |

V |

|

Ambient Temperature |

25°C |

|

Input Clock |

12.288 MHz |

|

Input Signal |

996.11 Hz |

|

|

–0.5 dB Full Scale |

|

Input Sample Rate |

48 kHz |

|

Measurement Bandwidth |

20 Hz to 20 kHz |

|

Word Width |

20 Bits |

|

Load Capacitance |

100 pF |

|

Load Impedance |

47 kΩ |

|

Input Voltage HI |

3.5 |

V |

Input Voltage LO |

0.8 |

V |

ANALOG PERFORMANCE

|

Min |

Typ |

Max |

Unit |

|

|

|

|

|

Resolution |

|

24 |

|

Bits |

Signal-to-Noise Ratio (20 Hz to 20 kHz) |

|

|

|

|

No Filter (Stereo) |

|

105 |

|

dB |

With A-Weighted Filter (Stereo) |

|

108 |

|

dB |

Dynamic Range (20 Hz to 20 kHz, –60 dB Input) |

|

|

|

|

No Filter (Stereo) |

|

105 |

|

dB |

With A-Weighted Filter (Stereo) |

101 |

108 |

|

dB |

Total Harmonic Distortion + Noise (Stereo) |

|

–94 |

–91 |

dB |

PLL Performance |

|

|

|

|

Master Clock Input Frequency |

|

27 |

|

MHz |

Generated System Clocks |

|

|

|

|

SCLK0 |

|

33.8688 |

|

MHz |

SCLK1 |

|

12.288 |

|

MHz |

SCLK2 |

|

22.5792 |

|

MHz |

Jitter (SCLK0 and SCLK1) |

|

85 |

125 |

ps rms |

Analog Outputs |

|

|

|

|

Single-Ended Output Range (±Full Scale) |

|

3.17 |

|

V p-p |

Output Capacitance at Each Output Pin |

|

|

2 |

pF |

VREF (FILTR) |

2.34 |

2.39 |

2.44 |

V |

Gain Error |

–5 |

±2.0 |

+5 |

% |

Interchannel Gain Mismatch |

–0.15 |

±0.015 |

+0.15 |

dB |

Gain Drift |

|

150 |

250 |

ppm/°C |

DC Offset |

–25 |

–5 |

+15 |

mV |

Out-of-Band Energy (0.5 × fS to 100 kHz) |

|

|

–90 |

dB |

Interchannel Crosstalk (EIAJ Method) |

|

–120 |

|

dB |

Interchannel Phase Deviation |

|

±0.1 |

±0.1 |

Degrees |

De-Emphasis Gain Error |

|

|

dB |

|

|

|

|

|

|

NOTES

Performance of right and left channels is identical (exclusive of the Interchannel Gain Mismatch and Interchannel Phase Deviation specifications). Specifications subject to change without notice.

DIGITAL I/O (–40°C to +105°C )

|

Min |

Typ |

Max |

Unit |

|

|

|

|

|

Input Voltage HI (VIH) Except XIN |

2.2 |

|

|

V |

Input Voltage HI (VIH) XIN |

2.7 |

|

|

V |

Input Voltage LO (VIL) |

|

|

0.8 |

V |

Input Leakage (IIH @ VIH = 2.4 V) |

|

|

10 |

µA |

Input Leakage (IIL @ VIL = 0.8 V) |

|

|

10 |

µA |

High Level Output Voltage (VOH) IOH = 1 mA |

2.0 |

|

|

V |

Low Level Output Voltage (VOL) IOL = 1 mA Except XOUT |

|

|

0.4 |

V |

Low Level Output Voltage (VOL) IOL = 1 mA XOUT |

|

|

1.2 |

V |

Input Capacitance |

|

|

20 |

pF |

|

|

|

|

|

Specifications subject to change without notice.

–2– |

REV. 0 |

|

|

|

|

AD1959 |

|

TEMPERATURE RANGE |

|

|

|

|

|

|

|

|

|

|

|

|

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

Specifications Guaranteed |

|

25 |

|

°C |

|

Functionality Guaranteed |

–40 |

|

+105* |

°C |

|

Storage |

–55 |

|

+150 |

°C |

|

NOTES

*105°C ambient guaranteed for a 4-layer board, two 1 oz. planes, two 2 oz. signal layers. Derate to 85 °C for 2-layer board, 2 oz. layers.

Specifications subject to change without notice.

POWER

|

|

|

Min |

Typ |

Max |

Unit |

||

|

|

|

|

|

|

|

|

|

Supplies |

|

|

|

|

|

|

|

|

Voltage, Analog Digital PLL |

|

4.50 |

5 |

5.50 |

V |

|||

Analog Current |

|

|

|

|

36 |

42 |

mA |

|

Digital Current |

|

|

|

|

28 |

34 |

mA |

|

PLL Current |

|

|

|

|

27 |

32 |

mA |

|

Dissipation |

|

|

|

|

|

|

|

|

Operation – All Supplies |

|

|

|

455 |

540 |

mW |

||

Operation – Analog Supply |

|

|

|

180 |

|

|

mW |

|

Operation – Digital Supply |

|

|

|

140 |

|

|

mW |

|

Operation – PLL Supply |

|

|

|

135 |

|

|

mW |

|

|

|

|

|

|

|

|

|

|

Specifications subject to change without notice. |

|

|

|

|

|

|

|

|

DIGITAL FILTER CHARACTERISTICS |

|

|

|

|

|

|

|

|

Sample Rate (kHz) |

Pass Band (kHz) |

Stop Band (kHz) |

|

Stopband Attenuation (dB) |

|

Pass-Band Ripple (dB) |

||

|

|

|

|

|

|

|

|

|

44.1 |

DC–20 |

24.1–328.7 |

|

75 |

|

±0.0002 |

|

|

48 |

DC–21.8 |

26.23–358.28 |

|

75 |

|

±0.0002 |

|

|

96 |

DC–39.95 |

56.9–327.65 |

|

75 |

|

±0.0005 |

|

|

192 |

DC–87.2 |

117–327.65 |

|

60 |

|

0/–0.04 (DC–21.8 kHz) |

||

|

|

|

|

|

|

|

0/–0.5 (DC–65.4 kHz) |

|

|

|

|

|

|

|

|

0/–1.5 (DC–87.2 kHz) |

|

|

|

|

|

|

|

|

|

|

Specifications subject to change without notice.

GROUP DELAY

Chip Mode |

Group Delay Calculation |

fS |

Group Delay |

Unit |

INT8× Mode |

24.625/fS |

48 kHz |

513 |

µs |

INT4× Mode |

15.75/fS |

96 kHz |

164 |

µs |

INT2× Mode |

14/fS |

192 kHz |

72.91 |

µs |

Specifications subject to change without notice.

DIGITAL TIMING (Guaranteed over –40°C to +105°C, AVDD = DVDD = 5.0 V ± 10%)

|

|

Min |

Unit |

|

|

|

|

tDMP |

MCLK Period (FMCLK = 256 × FLRCLK) |

54 |

ns |

tDML |

MCLK LO Pulsewidth (All Modes) |

15 |

ns |

tDMH |

MCLK HI Pulsewidth (All Modes) |

10 |

ns |

tDBH |

BCLK HI Pulsewidth |

7 |

ns |

tDBL |

BCLK LO Pulsewidth |

12 |

ns |

tDBP |

BCLK Period |

60 |

ns |

tDLS |

LRCLK Setup |

20 |

ns |

tDLH |

LRCLK Hold (DSP Serial Port Mode Only) |

20 |

ns |

tDDS |

SDATA Setup |

15 |

ns |

tDDH |

SDATA Hold |

10 |

ns |

tRSTL |

RST LO Pulsewidth |

15 |

ns |

Specifications subject to change without notice.

REV. 0 |

–3– |

Loading...

Loading...