NSC CLC502MDC, CLC502AMC, CLC502AJP, CLC502AJE-TR13, CLC502AD-MLS Datasheet

...

N June 1999

CLC502

Clamping, Low-Gain Op Amp with Fast 14-bit Settling

General Description |

Features |

|

■ Output clamping with fast recovery |

|

■ 0.0025% settling in 25ns (32ns max.) |

|

■ Low power, 170mW |

|

■ Low distortion. -50dBc at 20MHz |

Applications

■ Output clamping applications

■ High-accuracy A/D systems (12-14 bits) ■ High-accuracy D/A converters

■ Pulse amplitude modulation systems

The CLC502 is available in several versions to meet a variety of requirements. A three-letter suffix determines the version:

CLC502AJP |

-40°C to +85°C |

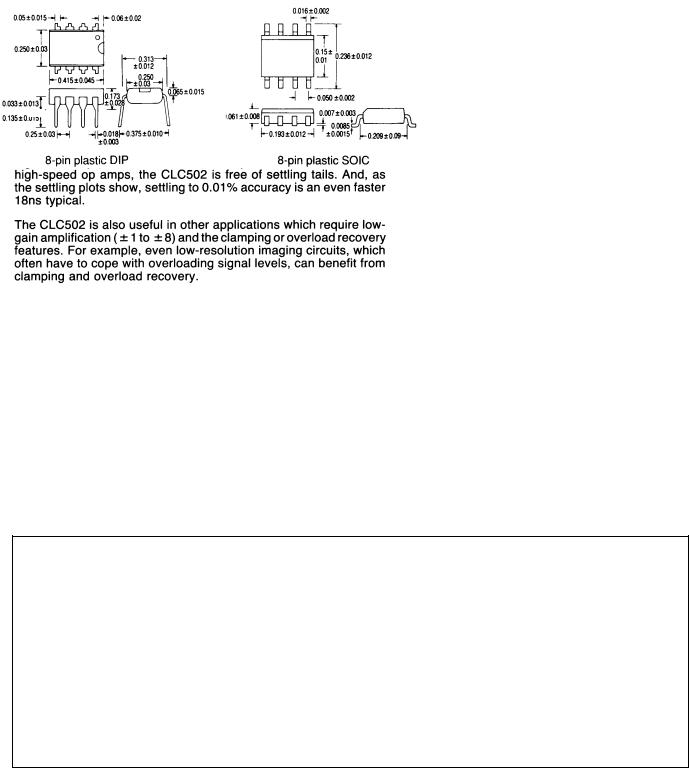

8-pin plastic DIP |

CLC502AJE |

-40°C to +85°C |

8-pin plastic SOIC |

DESC SMD number: 5962-91743

Package Dimensions

Pinout

DIP & SOIC

CLC502

Settling bit-14 Fast with Amp Op Gain-Low Clamping,

|

|

|

|

|

|

|

|

|

|

|

|

© 1999 National Semiconductor Corporation |

http://www.national.com |

||

Printed in the U.S.A.

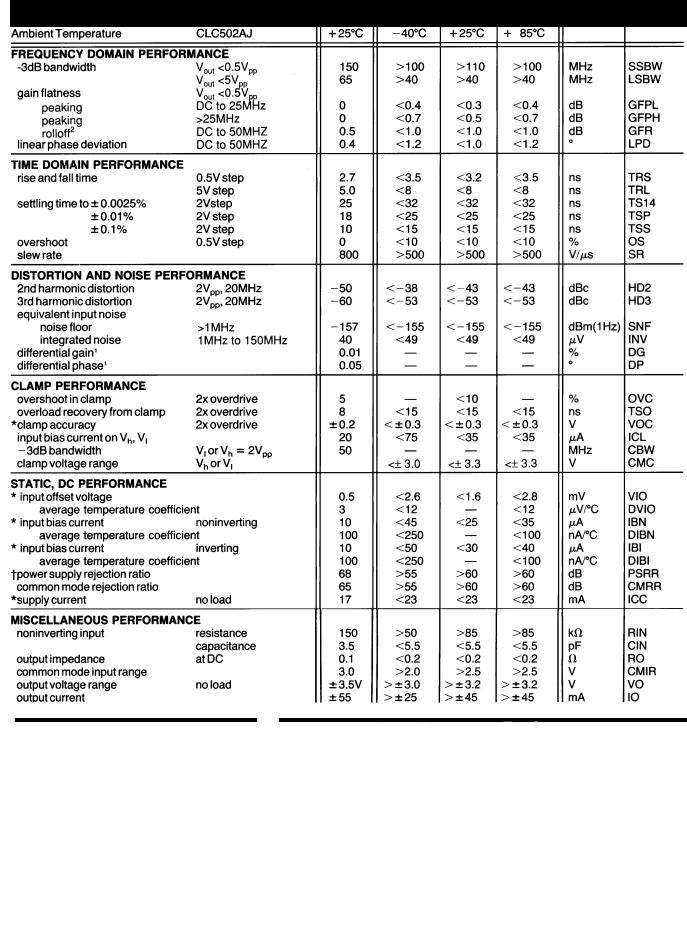

CLC502 Electrical Characteristics (Av = +2,Vcc = ±5V, R L = 100Ω, Rf = 250Ω,VH = +3V, VL = -3V)

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

Absolute Maximum Ratings |

Miscellaneous Ratings |

http://www.national.com |

2 |

Loading...

Loading...