MOTOROLA MC14536BF, MC14536BDWR2, MC14536BCP, MC14536BDW, MC14536BFL2 Datasheet

...

MC14536B

Programmable Timer

The MC14536B programmable timer is a 24±stage binary ripple counter with 16 stages selectable by a binary code. Provisions for an on±chip RC oscillator or an external clock are provided. An on±chip monostable circuit incorporating a pulse±type output has been included. By selecting the appropriate counter stage in conjunction with the appropriate input clock frequency, a variety of timing can be achieved.

•24 Flip±Flop Stages Ð Will Count From 20 to 224

•Last 16 Stages Selectable By Four±Bit Select Code

•8±Bypass Input Allows Bypassing of First Eight Stages

•Set and Reset Inputs

•Clock Inhibit and Oscillator Inhibit Inputs

•On±Chip RC Oscillator Provisions

•On±Chip Monostable Output Provisions

•Clock Conditioning Circuit Permits Operation With Very Long Rise and Fall Times

•Test Mode Allows Fast Test Sequence

•Supply Voltage Range = 3.0 Vdc to 18 Vdc

•Capable of Driving Two Low±power TTL Loads or One Low±power Schottky TTL Load Over the Rated Temperature Range

MAXIMUM RATINGS (Voltages Referenced to VSS) (Note 2.)

Symbol |

Parameter |

Value |

Unit |

|

|

|

|

VDD |

DC Supply Voltage Range |

± 0.5 to +18.0 |

V |

Vin, Vout |

Input or Output Voltage Range |

± 0.5 to VDD + 0.5 |

V |

|

(DC or Transient) |

|

|

|

|

|

|

Iin, Iout |

Input or Output Current |

±10 |

mA |

|

(DC or Transient) per Pin |

|

|

|

|

|

|

PD |

Power Dissipation, |

500 |

mW |

|

per Package (Note 3.) |

|

|

|

|

|

|

TA |

Operating Temperature Range |

± 55 to +125 |

°C |

Tstg |

Storage Temperature Range |

± 65 to +150 |

°C |

TL |

Lead Temperature |

260 |

°C |

|

(8±Second Soldering) |

|

|

|

|

|

|

2.Maximum Ratings are those values beyond which damage to the device may occur.

3.Temperature Derating:

Plastic ªP and D/DWº Packages: ± 7.0 mW/C From 65_C To 125_C

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high±impedance circuit. For proper operation, Vin and Vout should be constrained

to the range VSS v (Vin or Vout) v VDD.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD). Unused outputs must be left open.

http://onsemi.com

|

|

MARKING |

|

|

DIAGRAMS |

|

|

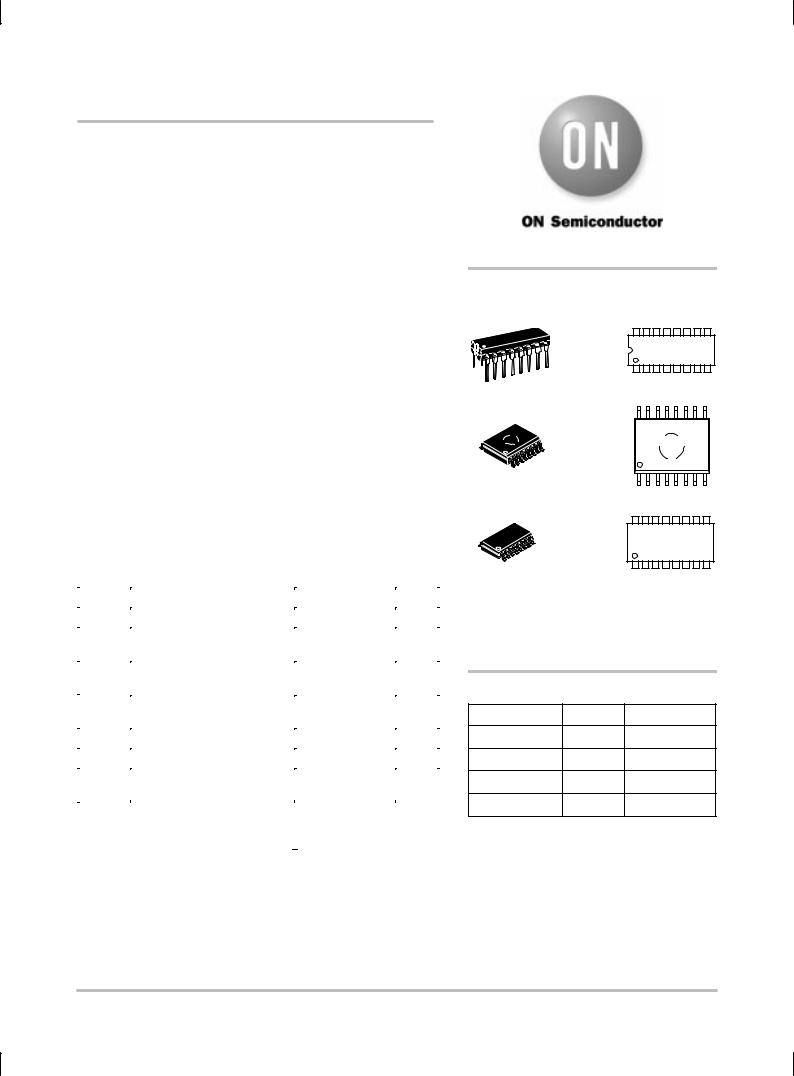

16 |

|

PDIP±16 |

MC14536BCP |

|

P SUFFIX |

|

|

AWLYYWW |

|

|

CASE 648 |

|

|

|

|

|

|

1 |

|

|

16 |

|

SOIC±16 |

14536B |

|

|

|

|

DW SUFFIX |

|

|

CASE 751G |

AWLYYWW |

|

|

|

|

|

1 |

|

|

16 |

|

SOEIAJ±16 |

MC14536B |

|

F SUFFIX |

|

|

AWLYWW |

|

|

CASE 966 |

|

|

|

|

|

|

1 |

A |

= Assembly Location |

|

WL or L = Wafer Lot |

|

|

YY or Y |

= Year |

|

WW or W = Work Week |

||

ORDERING INFORMATION |

||

Device |

Package |

Shipping |

MC14536BCP |

PDIP±16 |

2000/Box |

MC14536BDW |

SOIC±16 |

47/Rail |

MC14536BDWR2 |

SOIC±16 |

1000/Tape & Reel |

MC14536BF |

SOEIAJ±16 |

See Note 1. |

1.For ordering information on the EIAJ version of the SOIC packages, please contact your local ON Semiconductor representative.

Semiconductor Components Industries, LLC, 2000 |

1 |

Publication Order Number: |

March, 2000 ± Rev. 5 |

|

MC14536B/D |

MC14536B

PIN ASSIGNMENT

SET |

|

1 |

16 |

VDD |

|

||||

|

||||

RESET |

|

2 |

15 |

MONO IN |

IN 1 |

|

3 |

14 |

OSC INH |

|

||||

OUT 1 |

|

4 |

13 |

DECODE |

|

||||

OUT 2 |

|

5 |

12 |

D |

|

||||

8±BYPASS |

|

6 |

11 |

C |

|

||||

CLOCK INH |

|

7 |

10 |

B |

|

||||

VSS |

|

8 |

9 |

A |

|

||||

|

BLOCK DIAGRAM

CLOCK INH. |

RESET |

SET 8 BYPASS |

|

7 |

2 |

1 |

6 |

OSC. INHIBIT 14

IN1 |

|

STAGES |

|

3 |

1 THRU 8 |

||

|

|||

|

|

4 5 OUT1 OUT2

VDD = PIN 16

VSS = PIN 8

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

STAGES 9 THRU 24 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q |

||||||||||||||||||||||||||||||||

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

|||||||||||||||||

|

|

|

|

|

|||||||||||||||||||||||||||||||||

A |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

B |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DECODER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

C |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

D |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DECODE |

|

|

|||||||

|

|

|

|

|

|

|

MONO±IN |

|

|

15 |

|

|

|

|

MONOSTABLE |

|

|

13 |

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

MULTIVIBRATOR |

|

|

|

|

OUT |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

http://onsemi.com

2

MC14536B

ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS)

|

|

|

VDD |

± 55_C |

|

25_C |

|

|

125_C |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

|

Symbol |

Vdc |

Min |

Max |

Min |

Typ (4.) |

Max |

Min |

Max |

Unit |

|

Output Voltage |

ª0º Level |

VOL |

5.0 |

Ð |

0.05 |

Ð |

0 |

0.05 |

Ð |

0.05 |

Vdc |

|

Vin = VDD or 0 |

|

|

10 |

Ð |

0.05 |

Ð |

0 |

0.05 |

Ð |

0.05 |

|

|

|

|

|

15 |

Ð |

0.05 |

Ð |

0 |

0.05 |

Ð |

0.05 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ª1º Level |

VOH |

5.0 |

4.95 |

Ð |

4.95 |

5.0 |

Ð |

4.95 |

Ð |

Vdc |

|

Vin = 0 or VDD |

|

|

10 |

9.95 |

Ð |

9.95 |

10 |

Ð |

9.95 |

Ð |

|

|

|

|

|

15 |

14.95 |

Ð |

14.95 |

15 |

Ð |

14.95 |

Ð |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Voltage |

ª0º Level |

VIL |

|

|

|

|

|

|

|

|

|

Vdc |

(VO = 4.5 or 0.5 Vdc) |

|

|

5.0 |

Ð |

1.5 |

Ð |

2.25 |

1.5 |

Ð |

1.5 |

|

|

(VO = 9.0 or 1.0 Vdc) |

|

|

10 |

Ð |

3.0 |

Ð |

4.50 |

3.0 |

Ð |

3.0 |

|

|

(VO = 13.5 or 1.5 Vdc) |

|

15 |

Ð |

4.0 |

Ð |

6.75 |

4.0 |

Ð |

4.0 |

|

||

(VO = 0.5 or 4.5 Vdc) |

ª1º Level |

VIH |

5.0 |

3.5 |

Ð |

3.5 |

2.75 |

Ð |

3.5 |

Ð |

Vdc |

|

|

|

|

||||||||||

(VO = 1.0 or 9.0 Vdc) |

|

|

10 |

7.0 |

Ð |

7.0 |

5.50 |

Ð |

7.0 |

Ð |

|

|

(VO = 1.5 or 13.5 Vdc) |

|

15 |

11 |

Ð |

11 |

8.25 |

Ð |

11 |

Ð |

|

||

Output Drive Current |

|

IOH |

|

|

|

|

|

|

|

|

|

mAdc |

(VOH = 2.5 Vdc) |

Source |

|

5.0 |

± 1.2 |

Ð |

± 1.0 |

± 1.7 |

Ð |

± 0.7 |

Ð |

|

|

(VOH = 4.6 Vdc) |

Pins 4 & 5 |

|

5.0 |

± 0.25 |

Ð |

± 0.25 |

± 0.36 |

Ð |

± 0.14 |

Ð |

|

|

(VOH = 9.5 Vdc) |

|

|

10 |

± 0.62 |

Ð |

± 0.5 |

± 0.9 |

Ð |

± 0.35 |

Ð |

|

|

(VOH = 13.5 Vdc) |

|

|

15 |

± 1.8 |

Ð |

± 1.5 |

± 3.5 |

Ð |

± 1.1 |

Ð |

|

|

(VOH = 2.5 Vdc) |

Source |

|

5.0 |

± 3.0 |

Ð |

± 2.4 |

± 4.2 |

Ð |

± 1.7 |

Ð |

mAdc |

|

(VOH = 4.6 Vdc) |

Pin 13 |

|

5.0 |

± 0.64 |

Ð |

± 0.51 |

± 0.88 |

Ð |

± 0.36 |

Ð |

|

|

(VOH = 9.5 Vdc) |

|

|

10 |

± 1.6 |

Ð |

± 1.3 |

± 2.25 |

Ð |

± 0.9 |

Ð |

|

|

(VOH = 13.5 Vdc) |

|

|

15 |

± 4.2 |

Ð |

± 3.4 |

± 8.8 |

Ð |

± 2.4 |

Ð |

|

|

(VOL = 0.4 Vdc) |

Sink |

IOL |

5.0 |

0.64 |

Ð |

0.51 |

0.88 |

Ð |

0.36 |

Ð |

mAdc |

|

(VOL = 0.5 Vdc) |

|

|

10 |

1.6 |

Ð |

1.3 |

2.25 |

Ð |

0.9 |

Ð |

|

|

(VOL = 1.5 Vdc) |

|

|

15 |

4.2 |

Ð |

3.4 |

8.8 |

Ð |

2.4 |

Ð |

|

|

Input Current |

|

Iin |

15 |

Ð |

± 0.1 |

Ð |

± 0.00001 |

± 0.1 |

Ð |

± 1.0 |

μAdc |

|

Input Capacitance |

|

Cin |

Ð |

Ð |

Ð |

Ð |

5.0 |

7.5 |

Ð |

Ð |

pF |

|

(Vin = 0) |

|

|

|

|

|

|

|

|

|

|

|

|

Quiescent Current |

|

IDD |

5.0 |

Ð |

5.0 |

Ð |

0.010 |

5.0 |

Ð |

150 |

μAdc |

|

(Per Package) |

|

|

10 |

Ð |

10 |

Ð |

0.020 |

10 |

Ð |

300 |

|

|

|

|

|

15 |

Ð |

20 |

Ð |

0.030 |

20 |

Ð |

600 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Total Supply Current (5.) (6.) |

I |

5.0 |

|

|

I = (1.50 μA/kHz) f + I |

DD |

|

|

μAdc |

|||

|

|

T |

|

|

|

T |

|

|

|

|

|

|

(Dynamic plus Quiescent, |

|

10 |

|

|

IT = (2.30 μA/kHz) f + IDD |

|

|

|

||||

Per Package) |

|

|

15 |

|

|

IT = (3.55 μA/kHz) f + IDD |

|

|

|

|||

(CL = 50 pF on all outputs, all |

|

|

|

|

|

|

|

|

|

|

|

|

buffers switching) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.Data labelled ªTypº is not to be used for design purposes but is intended as an indication of the IC's potential performance.

5.The formulas given are for the typical characteristics only at 25_C.

6.To calculate total supply current at loads other than 50 pF:

IT(CL) = IT(50 pF) + (CL ± 50) Vfk

where: IT is in μA (per package), CL in pF, V = (VDD ± VSS) in volts, f in kHz is input frequency, and k = 0.003.

http://onsemi.com

3

MC14536B

SWITCHING CHARACTERISTICS (7.) (CL = 50 pF, TA = 25_C)

Characteristic |

Symbol |

V |

Min |

Typ (8.) |

Max |

Unit |

|

|

DD |

|

|

|

|

Output Rise and Fall Time (Pin 13) |

tTLH, |

|

|

|

|

ns |

tTLH, tTHL = (1.5 ns/pF) CL + 25 ns |

tTHL |

5.0 |

Ð |

100 |

200 |

|

tTLH, tTHL = (0.75 ns/pF) CL + 12.5 ns |

|

10 |

Ð |

50 |

100 |

|

tTLH, tTHL = (0.55 ns/pF) CL + 9.5 ns |

|

15 |

Ð |

40 |

80 |

|

Propagation Delay Time |

tPLH, |

|

|

|

|

ns |

Clock to Q1, 8±Bypass (Pin 6) High |

tPHL |

|

|

|

|

|

tPLH, tPHL = (1.7 ns/pF) CL + 1715 ns |

|

5.0 |

Ð |

1800 |

3600 |

|

tPLH, tPHL = (0.66 ns/pF) CL + 617 ns |

|

10 |

Ð |

650 |

1300 |

|

tPLH, tPHL = (0.5 ns/pF) CL + 425 ns |

|

15 |

Ð |

450 |

1000 |

|

Clock to Q1, 8±Bypass (Pin 6) Low |

tPLH, |

|

|

|

|

μs |

tPLH, tPHL = (1.7 ns/pF) CL + 3715 ns |

tPHL |

5.0 |

Ð |

3.8 |

7.6 |

|

tPLH, tPHL = (0.66 ns/pF) CL + 1467 ns |

|

10 |

Ð |

1.5 |

3.0 |

|

tPLH, tPHL = (0.5 ns/pF) CL + 1075 ns |

|

15 |

Ð |

1.1 |

2.3 |

|

Clock to Q16 |

tPLH, |

|

|

|

|

μs |

tPHL, tPLH = (1.7 ns/pF) CL + 6915 ns |

tPHL |

5.0 |

Ð |

7.0 |

14 |

|

tPHL, tPLH = (0.66 ns/pF) CL + 2967 ns |

|

10 |

Ð |

3.0 |

6.0 |

|

tPHL, tPLH = (0.5 ns/pF) CL + 2175 ns |

|

15 |

Ð |

2.2 |

4.5 |

|

Reset to Qn |

tPHL |

|

|

|

|

ns |

tPHL = (1.7 ns/pF) CL + 1415 ns |

|

5.0 |

Ð |

1500 |

3000 |

|

tPHL = (0.66 ns/pF) CL + 567 ns |

|

10 |

Ð |

600 |

1200 |

|

tPHL = (0.5 ns/pF) CL + 425 ns |

|

15 |

Ð |

450 |

900 |

|

Clock Pulse Width |

tWH |

5.0 |

600 |

300 |

Ð |

ns |

|

|

10 |

200 |

100 |

Ð |

|

|

|

15 |

170 |

85 |

Ð |

|

|

|

|

|

|

|

|

Clock Pulse Frequency |

fcl |

5.0 |

Ð |

1.2 |

0.4 |

MHz |

(50% Duty Cycle) |

|

10 |

Ð |

3.0 |

1.5 |

|

|

|

15 |

Ð |

5.0 |

2.0 |

|

|

|

|

|

|

|

|

Clock Rise and Fall Time |

tTLH, |

5.0 |

|

|

|

Ð |

|

tTHL |

10 |

|

No Limit |

|

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

Reset Pulse Width |

tWH |

5.0 |

1000 |

500 |

Ð |

ns |

|

|

10 |

400 |

200 |

Ð |

|

|

|

15 |

300 |

150 |

Ð |

|

|

|

|

|

|

|

|

7.The formulas given are for the typical characteristics only at 25_C.

8.Data labelled ªTypº is not to be used for design purposes but is intended as an indication of the IC's potential performance.

http://onsemi.com

4

MC14536B

PIN DESCRIPTIONS

INPUTS

SET (Pin 1) Ð A high on Set asynchronously forces Decode Out to a high level. This is accomplished by setting an output conditioning latch to a high level while at the same time resetting the 24 flip±flop stages. After Set goes low (inactive), the occurrence of the first negative clock transition on IN1 causes Decode Out to go low. The counter's flip±flop stages begin counting on the second negative clock transition of IN1. When Set is high, the on±chip RC oscillator is disabled. This allows for very low±power standby operation.

RESET (Pin 2) Ð A high on Reset asynchronously forces Decode Out to a low level; all 24 flip±flop stages are also reset to a low level. Like the Set input, Reset disables the on±chip RC oscillator for standby operation.

IN1 (Pin 3) Ð The device's internal counters advance on the negative±going edge of this input. IN1 may be used as an external clock input or used in conjunction with OUT1 and OUT2 to form an RC oscillator. When an external clock is used, both OUT1 and OUT2 may be left unconnected or used to drive 1 LSTTL or several CMOS loads.

8±BYPASS (Pin 6) Ð A high on this input causes the first 8 flip±flop stages to be bypassed. This device essentially becomes a 16±stage counter with all 16 stages selectable. Selection is accomplished by the A, B, C, and D inputs. (See the truth tables.)

CLOCK INHIBIT (Pin 7) Ð A high on this input disconnects the first counter stage from the clocking source. This holds the present count and inhibits further counting. However, the clocking source may continue to run. Therefore, when Clock Inhibit is brought low, no oscillator start±up time is required. When Clock Inhibit is low, the counter will start counting on the occurrence of the first negative edge of the clocking source at IN1.

OSC INHIBIT (Pin 14) Ð A high level on this pin stops the RC oscillator which allows for very low±power standby operation. May also be used, in conjunction with an external clock, with essentially the same results as the Clock Inhibit input.

MONO±IN (Pin 15) Ð Used as the timing pin for the on±chip monostable multivibrator. If the Mono±In input is connected to VSS, the monostable circuit is disabled, and Decode Out is directly connected to the selected Q output. The monostable circuit is enabled if a resistor is connected between Mono±In and VDD. This resistor and the device's internal capacitance will determine the minimum output pulse widths. With the addition of an external capacitor to VSS, the pulse width range may be extended. For reliable operation the resistor value should be limited to the range of 5 kΩ to 100 kΩ and the capacitor value should be limited to a maximum of 1000 pf. (See figures 3, 4, 5, and 10).

A, B, C, D (Pins 9, 10, 11, 12) Ð These inputs select the flip±flop stage to be connected to Decode Out. (See the truth tables.)

OUTPUTS

OUT1, OUT2 (Pin 4, 5) Ð Outputs used in conjunction with IN1 to form an RC oscillator. These outputs are buffered and may be used for 20 frequency division of an external clock.

DECODE OUT (Pin 13) Ð Output function depends on configuration. When the monostable circuit is disabled, this output is a 50% duty cycle square wave during free run.

TEST MODE

The test mode configuration divides the 24 flip±flop stages into three 8±stage sections to facilitate a fast test sequence. The test mode is enabled when 8±Bypass, Set and Reset are at a high level. (See Figure 8.)

http://onsemi.com

5

Loading...

Loading...