Fairchild Semiconductor 74AC280SJX, 74AC280SJ, 74AC280SCX, 74AC280SC Datasheet

© 1999 Fairchild Semiconductor Corporation DS009955 www.fairchildsemi.com

November 1988

Revised November 1999

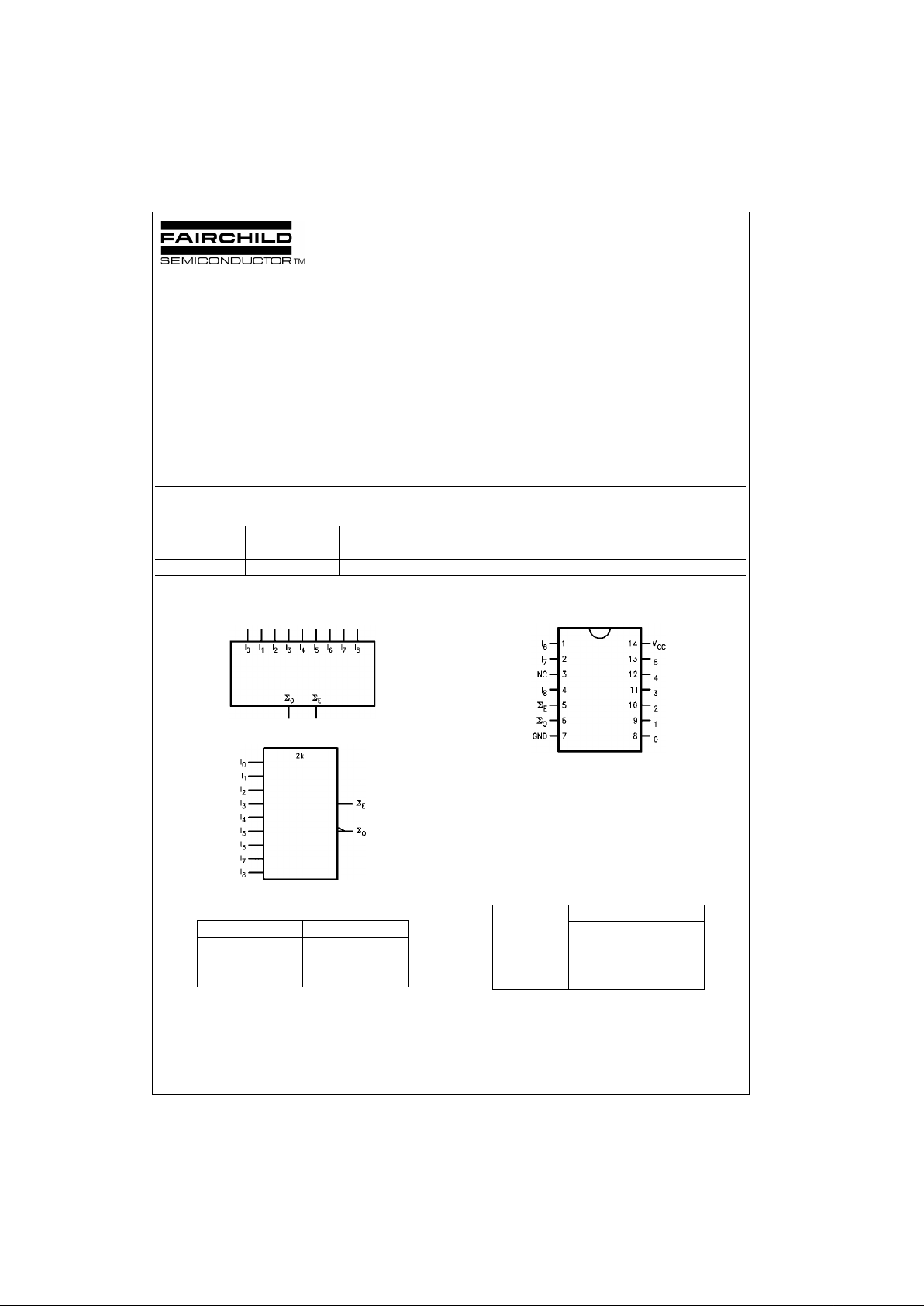

74AC280 9-Bit Parity Generator/Checker

74AC280

9-Bit Parity Generator/Checker

General Description

The AC280 is a high-sp eed parity generator/checker th at

accepts nine bits of input data and detects whether an

even or an odd number of these inputs is HIGH. If a n even

number of inputs is HIGH, the Sum Even output is HIGH. If

an odd number is HIGH, the Sum Even output is LOW. The

Sum Odd output is t he complemen t of the Sum Even output.

Features

■ ICC reduced by 50%

■ 9-bit width for memory applications

■ AC280: 5962-92201

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending su ffix let te r “X” to the ordering code.

Logic Symbols

IEEE/IEC

Pin Descriptions

Connection Diagram

Truth Table

H = HIGH Voltage Level

L = LOW Voltage Level

FACT is a trademark of Fairchild Semiconductor Corporation.

Order Number Package Number Package Description

74AC280SC M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow Body

74AC280SJ M14D 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Pin Names Description

I

0–I8

Data Inputs

∑

Ο

Odd Parity Output

∑

Ε

Even Parity Output

Number of Outputs

HIGH Inputs

∑ Even ∑ Odd

I

0–I8

0, 2, 4, 6, 8 H L

1, 3, 5, 7, 9 L H

www.fairchildsemi.com 2

74AC280

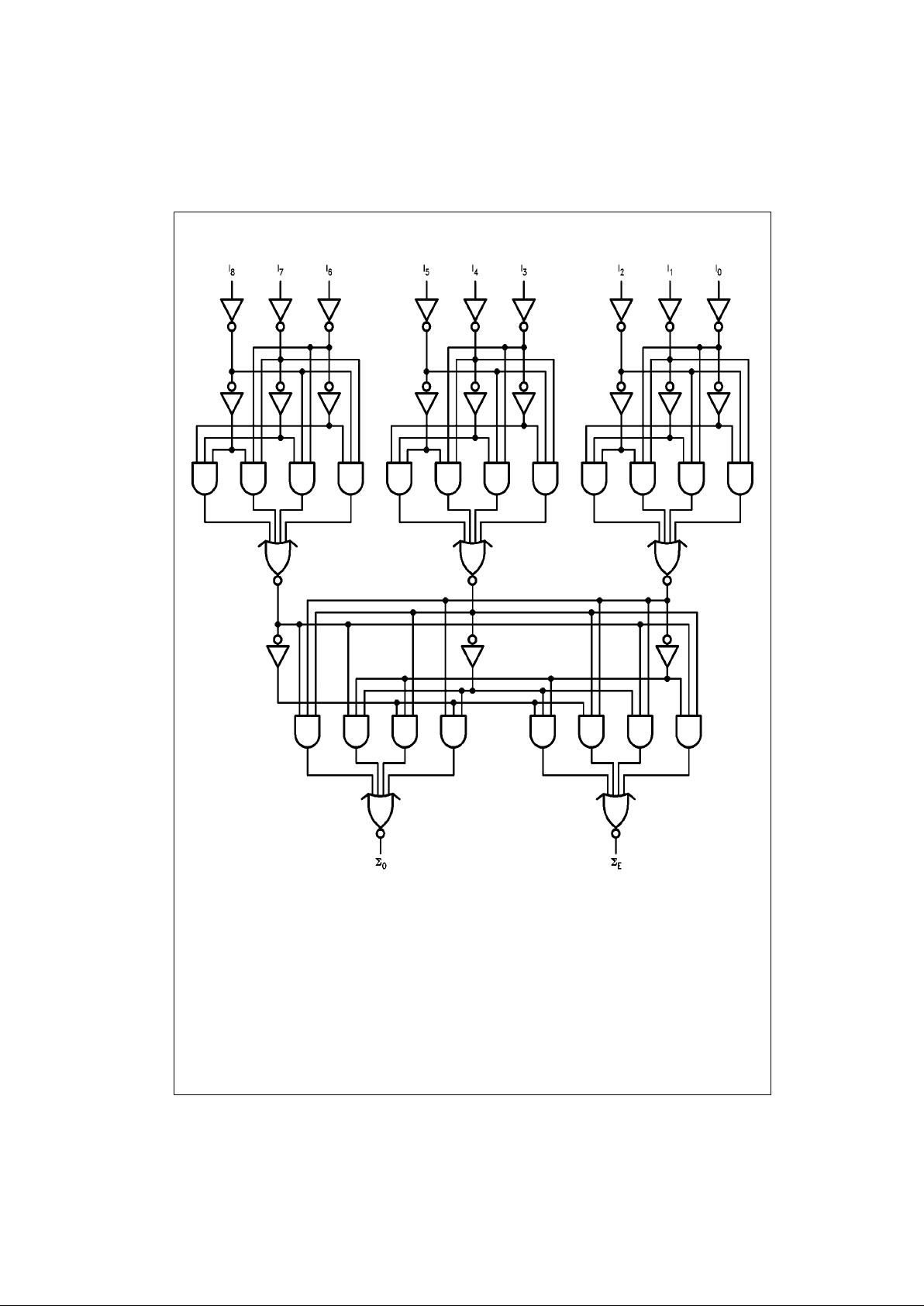

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

Loading...

Loading...