Motorola MCM56824AZP35R2, MCM56824AZP25R2, MCM56824AZP20, MCM56824AZP20R2, MCM56824AZP25 Datasheet

...

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MCM56824A/D

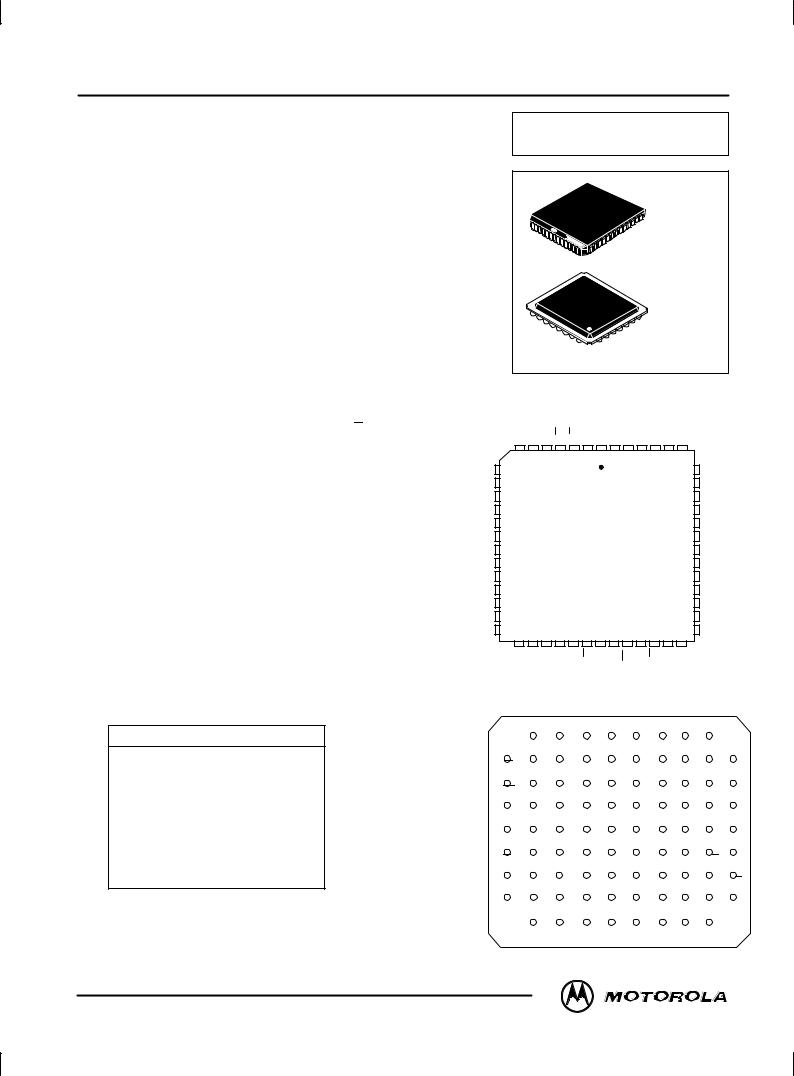

DSPRAM

8K x 24 Bit Fast Static RAM

The MCM56824A is a 196,608 bit static random access memory organized as 8,192 words of 24 bits. The device integrates an 8K x 24 SRAM core with multiple chip enable inputs, output enable, and an externally controlled single address pin multiplexer. These functions allow for direct connection to the Motorola DSP56001 Digital Signal Processor and provide a very efficient means for implementation of a reduced parts count system requiring no additional interface logic.

The availability of multiple chip enable (E1 and E2) and output enable (G) inputs provides for greater system flexibility when multiple devices are used. With either chip enable input unasserted, the device will enter standby mode, useful in low±power applications. A single on±chip multiplexer selects A12 or X/Yas the highest order address input depending upon the state of the V/S control input. This feature allows one physical static RAM component to efficiently store program and vector or scalar operands by dynamically re±partitioning the RAM array. Typical applications will logically map vector operands into upper memory with scalar operands being stored in lower memory. By connecting

MCM56824A

FN PACKAGE 52±LEAD PLCC CASE 778±02

9 x 10 GRID

86 BUMP PBGA CASE 896A±01

PIN ASSIGNMENTS

PLCC

DSP56001address A15 to the VECTOR/SCALAR (V/S) MUX control pin, such partitioning can occur with no additional components. This allows efficient utilization of the RAM resource irrespective of operand type. See application diagrams at the end of this document for additional information.

Multiple power and ground pins have been utilized to minimize effects induced by output noise.

The MCM56824A is available in a 52 pin plastic leaded chip±carrier (PLCC) and a 9 x 10 grid, 86 bump surface mount PBGA.

•Single 5 V ± 10% Power Supply

•Fast Access and Cycle Times: 20/25/35 ns Max

•Fully Static Read and Write Operations

•Equal Address and Chip Enable Access Times

•Single Bit On±Chip Address Multiplexer

•Active High and Active Low Chip Enable Inputs

•Output Enable Controlled Three State Outputs

•High Board Density PLCC Package

•Low Power Standby Mode

•Fully TTL Compatible

PIN NAMES

A0 ± A11 . . . . . . . . . . . . . . . Address Inputs

A12, X/Y . . . . . . . . . . Multiplexed Address

V/S . . . . . . . . . Address Multiplexer Control

W . . . . . . . . . . . . . . . . . . . . . . . Write Enable

E1, E2 . . . . . . . . . . . . . . . . . . . Chip Enable

G . . . . . . . . . . . . . . . . . . . . . . Output Enable

DQ0 ± DQ23 . . . . . . . . . . Data Input/Output

VCC . . . . . . . . . . . . . . . +5 V Power Supply

VSS . . . . . . . . . . . . . . . . . . . . . . . . . . Ground

NC . . . . . . . . . . . . . . . . . . . . No Connection

For proper operation of the device, all VSS pins must be connected to ground.

DSPRAM is a trademark of Motorola, Inc.

REV 2 4/95

MOTOROLAMotorola, Inc. 1995FAST SRAM

|

|

A10 |

A11 |

A12 |

X/Y |

V/S |

NC |

CC |

A0 |

A1 A2 |

A3 A4 |

A5 |

|

|

|

|

|

V |

|

|

|

||||||||||

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

|

52 51 50 49 48 47 |

|

|

|||

DQ0 |

8 |

|

|

|

|

|

|

|

|

|

|

|

46 |

DQ23 |

|

DQ1 |

9 |

|

|

|

|

|

|

|

|

|

|

|

45 |

DQ22 |

|

DQ2 |

10 |

|

|

|

|

|

|

|

|

|

|

|

44 |

DQ21 |

|

VSS |

11 |

|

|

|

|

|

|

|

|

|

|

|

43 |

VSS |

|

DQ3 |

12 |

|

|

|

|

|

|

|

|

|

|

|

42 |

DQ20 |

|

DQ4 |

13 |

|

|

|

|

|

|

|

|

|

|

|

41 |

DQ19 |

|

DQ5 |

14 |

|

|

|

|

|

|

|

|

|

|

|

40 |

DQ18 |

|

DQ6 |

15 |

|

|

|

|

|

|

|

|

|

|

|

39 |

DQ17 |

|

DQ7 |

16 |

|

|

|

|

|

|

|

|

|

|

|

38 |

DQ16 |

|

DQ8 |

17 |

|

|

|

|

|

|

|

|

|

|

|

37 |

DQ15 |

|

VSS |

18 |

|

|

|

|

|

|

|

|

|

|

|

36 |

VSS |

|

DQ9 |

19 |

|

|

|

|

|

|

|

|

|

|

|

35 |

DQ14 |

|

DQ10 |

20 |

21 22 23 24 25 26 |

27 28 |

|

|

34 |

DQ13 |

|

|||||||

29 30 31 32 33 |

|

||||||||||||||

|

|

DQ11 |

A9 |

A8 |

A7 |

A6 |

G |

CC |

|

SS |

E1 E2 |

W NC |

DQ12 |

|

|

|

|

V |

|

V |

|

|

|||||||||

|

|

|

VIEW OF PBGA PACKAGE BOTTOM |

|

|||||||||||

|

10 |

|

9 |

|

8 |

|

7 |

|

|

6 |

5 |

4 |

3 |

2 |

1 |

A |

|

|

D13 |

VSS |

|

D16 D17 |

D18 |

D20 |

D21 |

D23 |

|

||||

|

|

|

|

|

|||||||||||

B |

W |

|

D12 |

|

D14 |

|

D15 |

|

|

D19 |

VSS |

D22 |

A5 |

A4 |

|

|

|

|

|

|

|

||||||||||

C |

E1 |

|

E2 |

|

|

|

|

|

|

|

|

|

|

A3 |

A2 |

|

|

|

|

|

|

|

|

|

|

|

|

||||

D |

VSS |

|

VSS |

|

|

|

|

|

|

|

|

|

|

A1 |

A0 |

|

|

|

|

|

|

|

|

|

|

|

|

||||

E |

VCC |

|

|

|

|

|

|

|

|

|

|

|

VCC |

||

|

|

|

|

|

|

|

|

|

|

|

|

||||

F |

G |

|

A6 |

|

|

|

|

|

|

|

|

|

|

V/S |

NC |

|

|

|

|

|

|

|

|

|

|

|

|

||||

G |

A7 |

|

A8 |

|

|

|

|

|

|

|

|

|

|

A12 |

X/Y |

|

|

|

|

|

|

|

|

|

|

|

|

||||

H |

A9 |

|

D11 |

|

D9 |

|

D8 |

|

|

|

D4 |

VSS |

D1 |

A10 |

A11 |

|

|

|

|

|

|

|

|||||||||

J |

|

|

D10 |

VSS |

|

D7 |

|

D6 |

D5 |

D3 |

D2 |

D0 |

|

||

|

|

|

|

|

|

||||||||||

Not to Scale

MCM56824A

1

|

|

|

|

|

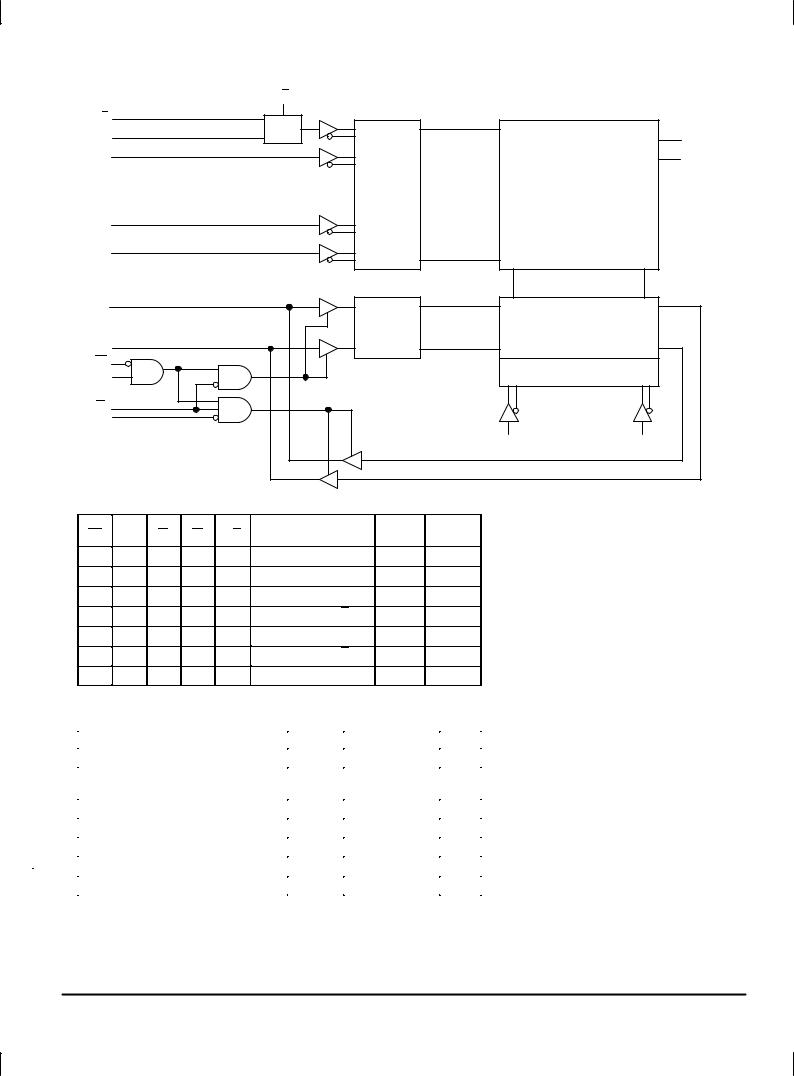

BLOCK DIAGRAM |

|

|

||

|

|

|

|

|

V/S |

|

|

|

|

X/Y |

|

|

|

|

A12 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

VCC |

A12 |

|

|

|

|

0 |

|

|

|

|

A0 |

|

|

|

|

2 TO 1 MUX |

|

|

|

VSS |

|

|

|

|

|

|

|

|

||

• |

|

|

|

|

|

|

|

MEMORY ARRAY |

|

• |

|

|

|

|

|

|

|

|

|

• |

|

|

|

|

|

ROW |

• |

|

|

|

|

|

|

|

|

|

|

||

A5 |

|

|

|

|

|

DECODER |

• |

|

|

|

|

|

|

|

|

• |

512 ROWS x |

|

|

|

|

|

|

|

|

|

|

|

|

A10 |

|

|

|

|

|

|

|

384 COLUMNS |

|

|

|

|

|

|

|

|

|

|

|

A11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

••• |

|

DQ0 |

|

|

|

|

|

INPUT |

|

|

|

|

|

|

|

|

• |

• |

|

• |

|

|

|

|

|

|

• |

DATA |

• |

COLUMN I/O |

• |

|

|

|

|

|

• |

• |

• |

||

DQ23 |

|

|

|

|

|

CONTROL |

|

|

|

|

|

|

|

|

|

|

|

|

|

E1 |

|

|

|

|

|

|

|

COLUMN DECODER |

|

E2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

••• |

|

W |

|

|

|

|

|

|

|

|

|

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(LSB) |

A6 |

|

A9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(MSB) |

|

|

|

TRUTH TABLE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Supply |

I/O |

|

|

E1 |

E2 |

G |

W |

V/S |

Mode |

Current |

Status |

|

|

H |

X |

X |

X |

X |

Not Selected |

ISB |

High±Z |

|

|

X |

L |

X |

X |

X |

Not Selected |

ISB |

High±Z |

|

|

L |

H |

H |

H |

X |

Output Disable |

ICC |

High±Z |

|

|

L |

H |

L |

H |

H |

Read Using X/Y |

ICC |

Data Out |

|

|

L |

H |

L |

H |

L |

Read Using A12 |

ICC |

Data Out |

|

|

L |

H |

X |

L |

H |

Write Using X/Y |

ICC |

Data In |

|

|

L |

H |

X |

L |

L |

Write Using A12 |

ICC |

Data In |

|

|

NOTE: X=don't care. |

|

|

|

|

|

|

|

||

ABSOLUTE MAXIMUM RATINGS (Voltages Referenced to VSS = 0 V)

Rating |

Symbol |

Value |

|

Unit |

|

|

|

|

|

Power Supply Voltage |

VCC |

± 0.5 to + |

7.0 |

V |

Voltage Relative to VSS for Any Pin |

Vin, Vout |

± 0.5 to VCC + 0.5 |

V |

|

Except VCC |

|

|

|

|

Output Current (per I/O) |

Iout |

± 20 |

|

mA |

Power Dissipation |

PD |

1.75 |

|

W |

Temperature Under Bias |

Tbias |

± 10 to + |

85 |

°C |

Operating Temperature |

TA |

0 to + 70 |

°C |

|

Storage Temperature |

Tstg |

± 55 to + 125 |

°C |

|

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This device contains circuitry to protect against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high±impedance circuit.

This CMOS memory circuit has been designed to meet the dc and ac specifications shown in the tables, after thermal equilibrium has been established. The circuit is assumed to be in a test socket or mounted on a printed circuit board with at least 300 LFPM of transverse air flow being maintained.

MCM56824A |

MOTOROLA FAST SRAM |

2 |

|

DC OPERATING CONDITIONS AND CHARACTERISTICS

(VCC = 5.0 V ± 10%, TA = 0 to + 70°C, Unless Otherwise Noted)

RECOMMENDED OPERATING CONDITIONS (Voltages Referenced to VSS = 0 V)

Parameter |

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

Supply Voltage (Operating Voltage Range) |

VCC |

4.5 |

5.0 |

5.5 |

V |

Input High Voltage |

VIH |

2.2 |

Ð |

VCC + 0.3 |

V |

Input Low Voltage |

VIL |

± 0.5* |

Ð |

0.8 |

V |

* VIL (min) = ± 3.0 V ac (pulse width ≤ 20 ns) |

|

|

|

|

|

DC CHARACTERISTICS

|

|

|

|

Parameter |

|

|

|

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Leakage Current (All Inputs, Vin = 0 to VCC) |

|

|

|

Ilkg(i) |

Ð |

± 1.0 |

μA |

|||||

Output Leakage Current (G = VIH, E1 = VIH, E2 = VIL, Vout = 0 to VCC) |

|

|

Ilkg(O) |

Ð |

± 1.0 |

μA |

||||||

AC Supply Current (G = VIH, E1 = VIL, E2 = VIH, Iout = 0 mA, |

|

|

ICCA |

|

|

mA |

||||||

All Other Inputs ≥ VIL = 0.0 V and VIH ≥ 3.0 V) |

MCM56824A±20 Cycle Time: ≥ |

20 ns |

|

|

Ð |

260 |

|

|||||

|

|

|

|

|

MCM56824A±25 Cycle Time: ≥ |

25 ns |

|

|

Ð |

220 |

|

|

|

|

|

|

|

MCM56824A±35 Cycle Time: ≥ |

35 ns |

|

|

Ð |

180 |

|

|

|

|

|

|

|

|

|

|

|

||||

Standby Current (E1 = VIH, E2 = VIL, All Inputs = VIL or VIH) |

|

|

ISB1 |

Ð |

15 |

mA |

||||||

CMOS Standby Current (E1 ≥ VCC ± 0.2 V, E2 ≤ 0.2 V, All Inputs ≥ VCC ± 0.2 V or ≤ 0.2 V) |

ISB2 |

Ð |

10 |

mA |

||||||||

Output Low Voltage (IOL = + 8.0 mA) |

|

|

|

VOL |

Ð |

0.4 |

V |

|||||

Output High Voltage (IOH = ± 4.0 mA) |

|

|

|

VOH |

2.4 |

Ð |

V |

|||||

CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, TA = 25°C, Periodically Sampled Rather Than 100% Tested) |

|

|

|

|||||||||

|

|

|

|

Parameter |

|

|

|

Symbol |

|

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|||||

Input Capacitance |

All Pins Except DQ0 ± DQ23 |

|

Cin |

|

4 |

6 |

pF |

|||||

Input/Output Capacitance |

DQ0 ± DQ23 |

|

Cout |

|

6 |

8 |

pF |

|||||

|

|

|

|

+ 5 V |

|

|

RL = 50 Ω |

|

480 Ω |

|

|

|

|

|

OUTPUT |

|

OUTPUT |

|

|

|

|

|

|

|

|

Z0 = 50 Ω |

255 |

Ω |

5 pF |

|

|

|

||

|

|

VL = 1.5 V |

|

|

|

(a) |

|

|

(b) |

Figure 1. AC Test Loads

MOTOROLA FAST SRAM |

MCM56824A |

|

3 |

Loading...

Loading...