Philips TDA8772AH-3, TDA8772H-8, TDA8772H-3, TDA8772AH-8 Datasheet

INTEGRATED CIRCUITS

TDA8772; TDA8772A

Triple 8-bit video digital-to-analog converter

Product specification |

1995 Mar 09 |

Supersedes data of May 1994

File under Integrated Circuits, IC02

Philips Semiconductors

Philips Semiconductors |

Product specification |

|

|

|

|

Triple 8-bit video digital-to-analog

TDA8772; TDA8772A

converter

FEATURES

∙8-bit resolution

∙Sampling rate up to

35 MHz for TDA8772H/3, TDA8772AH/3

85 MHz for TDA8772H/8, TDA8772AH/8

∙Internal reference voltage regulator

∙No deglitching circuit required

∙SYNC, BLANK control inputs

∙3 independent clock inputs (one per DAC)

∙1 V output voltage range

∙75 Ω output load

∙TDA8772A has BLANK control input on the GREEN channel only while TDA8772 has it on the 3 channels

∙Single 5 V power supply

∙44-pin QFP package.

APPLICATIONS

∙General purpose high-speed digital-to-analog conversion

∙Digital TV

∙Graphic display

∙Desktop video processing.

ORDERING INFORMATION

GENERAL DESCRIPTION

The TDA8772, TDA8772A are triple 8-bit video digital-to-analog converters (DACs). They convert the digital input signals into analog voltage outputs at a maximum conversion rate of 35 MHz (TDA8772H/3, TDA8772AH/3) and 85 MHz (TDA8772H/8, TDA8772AH/8).

The DACs are based on resistor-string architecture with integrated output buffers. The output voltage range is determined by a built-in reference source.

The devices are fabricated in a 5 V CMOS process that ensures high functionality with low power dissipation.

TYPE NUMBER |

|

|

PACKAGE |

|

SAMPLING |

|

|

|

|

|

|

||

PINS |

PIN POSITION |

|

MATERIAL |

CODE |

FREQUENCY |

|

|

|

|||||

|

|

|

||||

|

|

|

|

|

|

|

TDA8772H/3 |

44 |

QFP44 |

|

plastic |

SOT307B |

35 MHz |

|

|

|

|

|

|

|

TDA8772AH/3 |

44 |

QFP44 |

|

plastic |

SOT307B |

35 MHz |

|

|

|

|

|

|

|

TDA8772H/8 |

44 |

QFP44 |

|

plastic |

SOT307B |

85 MHz |

|

|

|

|

|

|

|

TDA8772AH/8 |

44 |

QFP44 |

|

plastic |

SOT307B |

85 MHz |

|

|

|

|

|

|

|

1995 Mar 09 |

2 |

Philips Semiconductors |

Product specification |

|

|

Triple 8-bit video digital-to-analog

TDA8772; TDA8772A

converter

QUICK REFERENCE DATA

SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

|

|

VDDA |

analog supply voltage |

|

4.5 |

5.0 |

5.5 |

V |

VDDD |

digital supply voltage |

|

4.5 |

5.0 |

5.5 |

V |

IDDA |

analog supply current |

RL = 75 Ω; note 1 |

40 |

65 |

100 |

mA |

IDDD |

digital supply current |

|

|

|

|

|

|

TDA8772H/3, TDA8772AH/3 |

|

− |

7 |

16 |

mA |

|

TDA8772H/8, TDA8772AH/8 |

|

− |

16 |

27 |

mA |

|

|

|

|

|

|

|

INL |

integral non-linearity2 |

fclk = 35 MHz; ramp input |

− |

±0.5 |

±1 |

LSB |

|

|

fclk = 85 MHz; ramp input |

− |

±0.75 |

±1.2 |

LSB |

DNL |

differential non-linearity |

fclk = 35 MHz; ramp input |

− |

±0.25 |

±0.5 |

LSB |

|

|

fclk = 85 MHz; ramp input |

- |

±0.5 |

±0.75 |

LSB |

fclk(max) |

maximum clock frequency |

|

|

|

|

|

|

TDA8772H/3, TDA8772AH/3 |

|

35 |

− |

− |

MHz |

|

TDA8772H/8, TDA8772AH/8 |

|

85 |

− |

− |

MHz |

|

|

|

|

|

|

|

Ptot |

total power dissipation |

note 1 |

|

|

|

|

|

TDA8772H/3, TDA8772AH/3 |

RL = 75 Ω; fclk = 35 MHz |

180 |

360 |

640 |

mW |

|

TDA8772H/8, TDA8772AH/8 |

RL = 75 Ω; fclk = 85 MHz |

180 |

405 |

700 |

mW |

Note

1.Minimum and maximum data of current and power consumption are measured in worse case conditions: for minimum data, all digital inputs are at logic level 0 while for maximum data, all digital inputs are at logic level 1.

1995 Mar 09 |

3 |

Philips Semiconductors |

Product specification |

|

|

Triple 8-bit video digital-to-analog

TDA8772; TDA8772A

converter

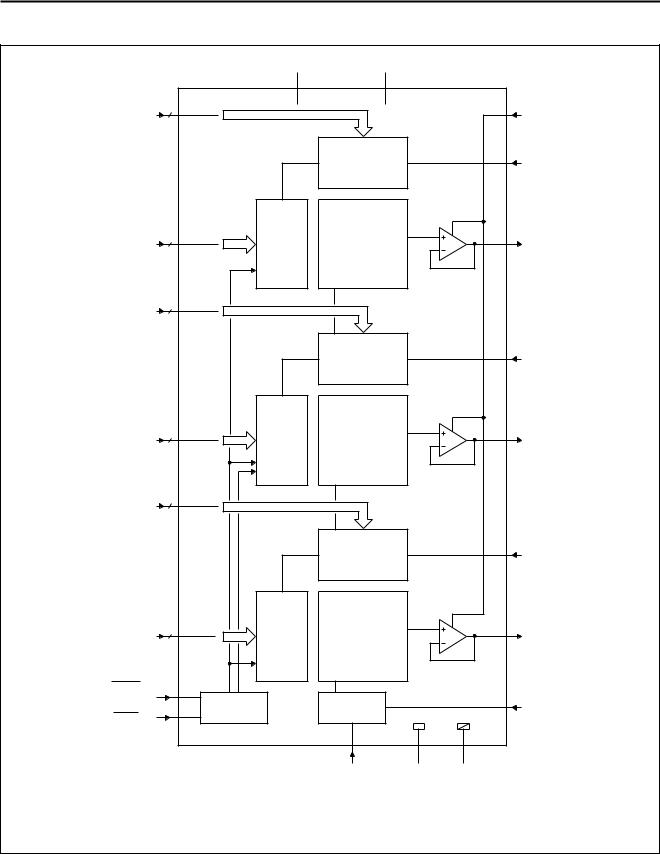

BLOCK DIAGRAMS |

|

|

|

|

|

|

|

|

|

handbook, full pagewidth |

|

|

|

V DDA |

V DDD |

|

|

|

|

RED |

4 |

|

|

35,39,43 |

10,32 |

|

|

||

8–5 |

|

|

|

|

|

41 |

reference |

||

digital inputs |

|

|

|

|

|

||||

|

|

|

|

4 |

|

|

|

current input |

|

(bits R0 to R3) |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

(I REFB ) |

|

|

|

|

|

|

|

|

|

|

|

|

|

TDA8772 |

|

LSB |

|

|

21 |

RED |

|

|

|

|

DECODER |

|

|

|

clock input |

||

|

|

|

|

|

|

|

|

||

RED |

4 |

4–1 |

|

MSB |

RESISTOR |

|

|

44 |

RED |

digital inputs |

4 |

|

|

||||||

|

|

DECODER |

STRING |

|

|

|

analog output |

||

(bits R4 to R7) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

GREEN |

4 |

20–17 |

|

|

|

|

|

|

|

digital inputs |

|

|

|

|

4 |

|

|

|

|

(bits G0 to G3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

|

|

22 |

GREEN |

|

|

|

|

|

DECODER |

|

|

|

clock input |

GREEN |

4 |

16–13 |

|

MSB |

RESISTOR |

|

|

40 |

GREEN |

digital inputs |

4 |

|

|

||||||

|

|

DECODER |

STRING |

|

|

|

analog output |

||

(bits G4 to G7) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

BLUE |

4 |

31–28 |

|

|

|

|

|

|

|

digital inputs |

|

|

|

|

4 |

|

|

|

|

(bits B0 to B3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

|

|

23 |

BLUE |

|

|

|

|

|

DECODER |

|

|

|

clock input |

BLUE |

4 |

27–24 |

MSB |

RESISTOR |

|

|

36 |

BLUE |

|

digital inputs |

|

|

|||||||

|

|

4 |

DECODER |

STRING |

|

|

|

analog output |

|

(bits B4 to B7) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

BLANK |

|

12 |

|

|

|

|

|

|

|

control input |

|

|

|

|

|

|

38 |

reference current |

|

|

|

CONTROL |

|

BANDGAP |

|

|

|||

|

|

11 |

|

|

|

|

input for internal |

||

|

|

REGISTER |

|

REFERENCE |

|

|

|

||

SYNC |

|

|

|

|

|

reference |

|||

|

|

|

|

|

|

|

|

||

control input |

|

|

|

|

34 |

|

37,42 |

9,33 |

(I REFA ) |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

reference voltage |

VSSA |

V SSD |

MBB661 - 2 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

decoupling input |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(V REF ) |

|

|

|

|

Fig.1 Block diagram for TDA8772.

1995 Mar 09 |

4 |

Philips Semiconductors |

Product specification |

|

|

Triple 8-bit video digital-to-analog

TDA8772; TDA8772A

converter

handbook, full pagewidth |

|

|

|

V DDA |

V DDD |

|

|

|

|

RED |

4 |

|

|

35,39,43 |

10,32 |

|

|

||

8–5 |

|

|

|

|

|

41 |

reference |

||

digital inputs |

|

|

|

|

|

||||

|

|

|

|

4 |

|

|

|

current input |

|

(bits R0 to R3) |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

(I REFB ) |

|

|

|

|

|

|

|

|

|

|

|

|

|

TDA8772A |

|

LSB |

|

|

21 |

RED |

|

|

|

|

DECODER |

|

|

|

clock input |

||

|

|

|

|

|

|

|

|

||

RED |

4 |

4–1 |

|

MSB |

RESISTOR |

|

|

44 |

RED |

digital inputs |

4 |

|

|

||||||

|

|

DECODER |

STRING |

|

|

|

analog output |

||

(bits R4 to R7) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

GREEN |

4 |

20–17 |

|

|

|

|

|

|

|

digital inputs |

|

|

|

|

4 |

|

|

|

|

(bits G0 to G3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

|

|

22 |

GREEN |

|

|

|

|

|

DECODER |

|

|

|

clock input |

GREEN |

4 |

16–13 |

|

MSB |

RESISTOR |

|

|

40 |

GREEN |

digital inputs |

4 |

|

|

||||||

|

|

DECODER |

STRING |

|

|

|

analog output |

||

(bits G4 to G7) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

BLUE |

4 |

31–28 |

|

|

|

|

|

|

|

digital inputs |

|

|

|

|

4 |

|

|

|

|

(bits B0 to B3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

|

|

23 |

BLUE |

|

|

|

|

|

DECODER |

|

|

|

clock input |

BLUE |

4 |

27–24 |

MSB |

RESISTOR |

|

|

36 |

BLUE |

|

digital inputs |

|

|

|||||||

|

|

4 |

DECODER |

STRING |

|

|

|

analog output |

|

(bits B4 to B7) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

BLANK |

|

12 |

|

|

|

|

|

|

|

control input |

|

|

|

|

|

|

38 |

reference current |

|

|

|

CONTROL |

|

BANDGAP |

|

|

|||

|

|

11 |

|

|

|

|

input for internal |

||

|

|

REGISTER |

|

REFERENCE |

|

|

|

||

SYNC |

|

|

|

|

|

reference |

|||

|

|

|

|

|

|

|

|

||

control input |

|

|

|

|

34 |

|

37,42 |

9,33 |

(I REFA ) |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

reference voltage |

VSSA |

V SSD |

MLB724 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

decoupling input |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(V REF ) |

|

|

|

|

Fig.2 Block diagram for TDA8772A.

1995 Mar 09 |

5 |

Philips Semiconductors |

Product specification |

|

|

Triple 8-bit video digital-to-analog

TDA8772; TDA8772A

converter

PINNING

|

SYMBOL |

PIN |

DESCRIPTION |

||

|

|

|

|

||

|

R7 |

1 |

RED digital input data; bit 7 (MSB) |

||

|

|

|

|

||

|

R6 |

2 |

RED digital input data; bit 6 |

||

|

|

|

|

||

|

R5 |

3 |

RED digital input data; bit 5 |

||

|

|

|

|

||

|

R4 |

4 |

RED digital input data; bit 4 |

||

|

|

|

|

||

|

R3 |

5 |

RED digital input data; bit 3 |

||

|

|

|

|

||

|

R2 |

6 |

RED digital input data; bit 2 |

||

|

|

|

|

||

|

R1 |

7 |

RED digital input data; bit 1 |

||

|

|

|

|

||

|

R0 |

8 |

RED digital input data; bit 0 (LSB) |

||

|

|

|

|

||

|

VSSD1 |

9 |

digital supply ground 1 |

||

|

VDDD1 |

10 |

digital supply voltage 1 |

||

|

|

|

|

11 |

composite sync control input; for GREEN channel only (active LOW) |

|

SYNC |

|

|

||

|

|

|

|

||

|

|

|

|

12 |

composite blank control input (active LOW) |

|

BLANK |

|

|||

|

|

|

|

||

|

G7 |

13 |

GREEN digital input data; bit 7 (MSB) |

||

|

|

|

|

||

|

G6 |

14 |

GREEN digital input data; bit 6 |

||

|

|

|

|

||

|

G5 |

15 |

GREEN digital input data; bit 5 |

||

|

|

|

|

||

|

G4 |

16 |

GREEN digital input data; bit 4 |

||

|

|

|

|

||

|

G3 |

17 |

GREEN digital input data; bit 3 |

||

|

|

|

|

||

|

G2 |

18 |

GREEN digital input data; bit 2 |

||

|

|

|

|

||

|

G1 |

19 |

GREEN digital input data; bit 1 |

||

|

|

|

|

||

|

G0 |

20 |

GREEN digital input data; bit 0 (LSB) |

||

|

|

|

|

||

|

CLKR |

21 |

RED clock input |

||

|

|

|

|

||

|

CLKG |

22 |

GREEN clock input |

||

|

|

|

|

||

|

CLKB |

23 |

BLUE clock input |

||

|

|

|

|

||

|

B7 |

24 |

BLUE digital input data; bit 7 (MSB) |

||

|

|

|

|

||

|

B6 |

25 |

BLUE digital input data; bit 6 |

||

|

|

|

|

||

|

B5 |

26 |

BLUE digital input data; bit 5 |

||

|

|

|

|

||

|

B4 |

27 |

BLUE digital input data; bit 4 |

||

|

|

|

|

||

|

B3 |

28 |

BLUE digital input data; bit 3 |

||

|

|

|

|

||

|

B2 |

29 |

BLUE digital input data; bit 2 |

||

|

|

|

|

||

|

B1 |

30 |

BLUE digital input data; bit 1 |

||

|

|

|

|

||

|

B0 |

31 |

BLUE digital input data; bit 0 (LSB) |

||

|

|

|

|

||

|

VDDD2 |

32 |

digital supply voltage 2 |

||

|

VSSD2 |

33 |

digital supply ground 2 |

||

|

VREF |

34 |

decoupling input for reference voltage |

||

|

VDDA1 |

35 |

analog supply voltage 1 |

||

|

OUTB |

36 |

BLUE analog output |

||

|

|

|

|

||

|

VSSA1 |

37 |

analog supply ground 1 |

||

|

IREFA |

38 |

reference current input for internal reference |

||

|

VDDA2 |

39 |

analog supply voltage 2 |

||

|

OUTG |

40 |

GREEN analog output |

||

|

|

|

|

|

|

1995 Mar 09 |

6 |

Loading...

Loading...