Philips TDA8768H-5-C1, TDA8768H-4-C1, TDA8768AH-7-C1, TDA8768AH-5-C1, TDA8768AH-4-C1 Datasheet

INTEGRATED CIRCUITS

DATA SHEET

TDA8768

12-bit high-speed Analog-to-Digital Converter (ADC)

Preliminary specification |

1998 Aug 26 |

Supersedes data of 1998 Feb 25

File under Integrated Circuits, IC02

Philips Semiconductors |

Preliminary specification |

|

|

12-bit high-speed Analog-to-Digital

TDA8768

Converter (ADC)

FEATURES

∙12-bit resolution

∙Sampling rate up to 55 MHz

∙−3 dB bandwidth of 190 MHz

∙5 V power supplies

∙Binary or twos-complement CMOS outputs

∙In-range CMOS-compatible output

∙TLL-CMOS compatible static digital inputs

∙3 to 5 V CMOS-compatible digital outputs

∙Differential clock input; Positive Emitter Coupled Logic (PECL)-compatible

∙Power dissipation 325 mW (typical)

∙Low analog input capacitance (typical 2 pF), no buffer amplifier required

∙Integrated sample-and-hold amplifier

∙Differential analog input

∙External amplitude range control

∙Voltage controlled regulator included.

QUICK REFERENCE DATA

APPLICATIONS

∙High-speed analog-to-digital conversion for

–Video signal digitizing

–High Definition TV (HDTV)

–Imaging (camera scanner)

–Medical imaging

–Telecommunication

–Base-station receiver.

GENERAL DESCRIPTION

The TDA8768 is a bipolar 12-bit Analog-to-Digital Converter (ADC) optimized for telecommunications and professional imaging. It converts the analog input signal into 12-bit binary coded digital words at a maximum sampling rate of 55 MHz. All static digital inputs (SH, CE and OTC) are TTL and CMOS compatible and all outputs are CMOS compatible. A sine wave clock input signal can also be used.

SYMBOL |

PARAMETER |

|

CONDITIONS |

|

MIN. |

TYP. |

|

MAX. |

UNIT |

||

|

|

|

|

|

|

|

|

|

|

|

|

VCCA |

analog supply voltage |

|

|

|

|

4.75 |

5.0 |

|

5.25 |

V |

|

VCCD |

digital supply voltage |

|

|

|

|

4.75 |

5.0 |

|

5.25 |

V |

|

VCCO |

output supply voltage |

|

|

|

|

3.0 |

3.3 |

|

5.25 |

V |

|

ICCA |

analog supply current |

|

|

|

|

− |

33 |

|

tbf |

mA |

|

ICCD |

digital supply current |

|

|

|

|

− |

30 |

|

tbf |

mA |

|

ICCO |

output supply current |

|

fCLK = 4 MHz; fi = 400 kHz |

|

− |

3.2 |

|

tbf |

mA |

||

INL |

integral non-linearity |

|

fCLK = 4 MHz; fi = 400 kHz |

|

− |

±2.0 |

|

±4.5 |

LSB |

||

DNL |

differential non-linearity |

|

fCLK = 4 MHz; fi = 400 kHz |

|

− |

±0.6 |

|

±1.0 |

LSB |

||

fCLK(max) |

maximum clock frequency |

|

|

|

|

|

|

|

|

|

|

|

TDA8768H/4 |

|

|

|

|

40 |

− |

|

− |

MHz |

|

|

TDA8768H/5 |

|

|

|

|

55 |

− |

|

− |

MHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

Ptot |

total power dissipation |

|

|

|

|

− |

325 |

|

tbf |

mW |

|

ORDERING INFORMATION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TYPE |

|

|

PACKAGE |

|

|

|

SAMPLING |

||||

|

|

|

|

|

|

|

|

||||

NUMBER |

NAME |

|

DESCRIPTION |

|

VERSION |

FREQUENCY (MHz) |

|||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||

TDA8768H/4 |

QFP44 |

plastic quad flat package; 44 leads |

|

SOT307-2 |

|

40 |

|

||||

|

(lead length 1.3 mm); body 10 × 10 × 1.75 mm |

|

|

|

|

|

|||||

TDA8768H/5 |

|

|

55 |

|

|||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

1998 Aug 26 |

2 |

Philips Semiconductors |

Preliminary specification |

|

|

12-bit high-speed Analog-to-Digital |

|

|

|

|

|

|

TDA8768 |

|||||

Converter (ADC) |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

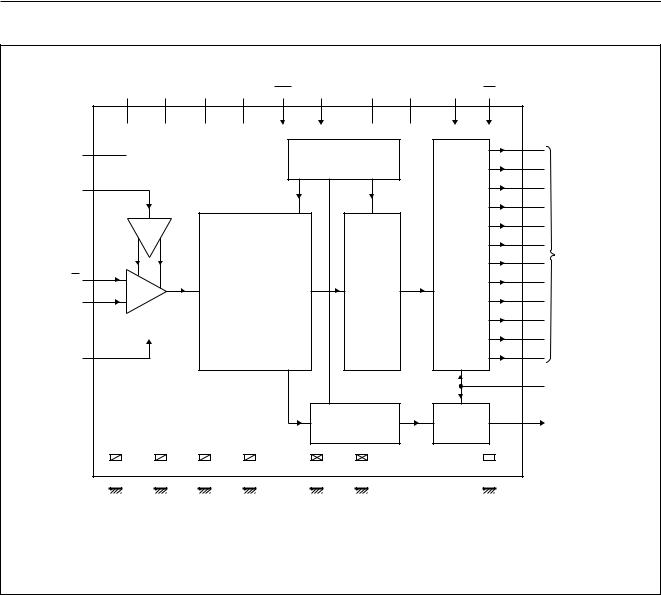

BLOCK DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

VCCA1 |

VCCA2 |

VCCA3 |

VCCA4 |

CLK |

CLK |

VCCD1 VCCD2 |

OTC |

CE |

|

|

|

|

2 |

9 |

3 |

41 |

35 |

36 |

37 |

15 |

18 |

19 |

|

|

|

1, 5 to 8, 12 to 14, 16 |

|

|

|

|

|

|

|

|

21 |

D11 |

MSB |

|

|

|

|

|

|

|

|

|

|

|

|||

n.c. |

|

|

|

|

CLOCK DRIVER |

|

|

|

22 |

D10 |

||

|

|

|

|

|

|

|

|

|||||

|

|

TDA8768 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

23 |

D9 |

|

||

11 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Vref |

|

|

|

|

|

|

|

|

|

24 |

D8 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

25 |

D7 |

|

AMP |

|

|

|

|

|

|

|

|

26 |

D6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

CMOS |

|

27 |

D5 |

data outputs |

|

|

|

|

|

|

|

|

OUTPUTS |

||||

|

|

|

|

|

|

|

|

|

|

|

||

43 |

|

|

|

|

|

|

|

|

|

28 |

D4 |

|

VI |

|

ANALOG-TO-DIGITAL |

LATCHES |

|

|

|

|

|

|

|||

42 |

|

|

|

|

29 |

D3 |

|

|||||

|

|

CONVERTER |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||||

VI |

|

|

|

|

|

|

|

|

|

30 |

D2 |

|

sample- |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

31 |

D1 |

|

||

and-hold |

|

|

|

|

|

|

|

|

|

|||

39 |

|

|

|

|

|

|

|

|

|

32 |

D0 |

LSB |

SH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

VCCO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OVERFLOW/ |

|

CMOS |

|

20 |

|

IR |

|

|

|

|

|

|

UNDERFLOW |

|

OUTPUT |

|

|

|||

|

|

|

|

|

|

LATCH |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

10 |

4 |

40 |

|

38 |

17 |

|

|

34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGR470 |

|

AGND1 |

AGND2 |

AGND3 |

AGND4 |

|

DGND1 |

DGND2 |

|

|

OGND |

|

|

|

Fig.1 Block diagram.

1998 Aug 26 |

3 |

Philips Semiconductors |

Preliminary specification |

|

|

12-bit high-speed Analog-to-Digital

TDA8768

Converter (ADC)

PINNING

|

SYMBOL |

PIN |

DESCRIPTION |

|

|

|

|

||

n.c. |

1 |

not connected |

||

|

|

|

||

VCCA1 |

2 |

analog supply voltage 1 (+5 V) |

||

|

VCCA3 |

3 |

analog supply voltage 3 (+5 V) |

|

|

AGND3 |

4 |

analog ground 3 |

|

|

|

|

|

|

|

n.c. |

5 |

not connected |

|

|

|

|

|

|

|

n.c. |

6 |

not connected |

|

|

|

|

|

|

|

n.c. |

7 |

not connected |

|

|

|

|

|

|

|

n.c. |

8 |

not connected |

|

|

|

|

|

|

|

VCCA2 |

9 |

analog supply voltage 2 (+5 V) |

|

|

AGND2 |

10 |

analog ground 2 |

|

|

|

|

|

|

|

Vref |

11 |

reference voltage input |

|

n.c. |

12 |

not connected |

||

|

|

|

||

n.c. |

13 |

not connected |

||

|

|

|

||

n.c. |

14 |

not connected |

||

|

|

|

||

VCCD2 |

15 |

digital supply voltage 2 (+5 V) |

||

n.c. |

16 |

not connected |

||

|

|

|

||

DGND2 |

17 |

digital ground 2 |

||

|

|

|

||

OTC |

18 |

control input twos complement |

||

|

|

|

|

output; active HIGH |

|

|

|

||

|

|

|

19 |

chip enable input |

|

CE |

|

||

|

|

|

|

(CMOS level; active LOW) |

|

|

|

||

IR |

20 |

in-range output |

||

|

|

|

||

D11 |

21 |

data output; bit 11 (MSB) |

||

|

|

|

||

D10 |

22 |

data output; bit 10 |

||

|

|

|

|

|

|

SYMBOL |

PIN |

DESCRIPTION |

||

|

|

|

|

||

|

D9 |

23 |

data output; bit 9 |

||

|

|

|

|

||

|

D8 |

24 |

data output; bit 8 |

||

|

|

|

|

||

|

D7 |

25 |

data output; bit 7 |

||

|

|

|

|

||

|

D6 |

26 |

data output; bit 6 |

||

|

|

|

|

||

|

D5 |

27 |

data output; bit 5 |

||

|

|

|

|

||

|

D4 |

28 |

data output; bit 4 |

||

|

|

|

|

||

|

D3 |

29 |

data output; bit 3 |

||

|

|

|

|

||

|

D2 |

30 |

data output; bit 2 |

||

|

|

|

|

||

|

D1 |

31 |

data output; bit 1 |

||

|

|

|

|

||

|

D0 |

32 |

data output; bit 0 (LSB) |

||

|

|

|

|

||

|

VCCO |

33 |

output supply voltage (3 to 5.25 V) |

||

|

OGND |

34 |

output ground |

||

|

|

|

|

|

|

|

|

|

|

35 |

complementary clock input; active |

|

CLK |

|

|||

|

|

|

|

|

LOW |

|

|

|

|

||

|

CLK |

36 |

clock input |

||

|

|

|

|

||

|

VCCD1 |

37 |

digital supply voltage 1 (+5 V) |

||

|

DGND1 |

38 |

digital ground 1 |

||

|

|

|

|

||

|

SH |

39 |

sample-and-hold enable input |

||

|

|

|

|

|

(CMOS level; active HIGH) |

|

|

|

|

||

|

AGND4 |

40 |

analog ground 4 |

||

|

|

|

|

||

|

VCCA4 |

41 |

analog supply voltage 4 (+5 V) |

||

|

VI |

42 |

positive analog input voltage |

||

|

|

I |

43 |

negative analog input voltage |

|

|

V |

||||

|

AGND1 |

44 |

analog ground 1 |

||

|

|

|

|

|

|

1998 Aug 26 |

4 |

Philips Semiconductors |

Preliminary specification |

|

|

12-bit high-speed Analog-to-Digital

TDA8768

Converter (ADC)

AGND1 |

|

V |

|

V |

|

V |

|

AGND4 |

|

SH |

|

DGND1 |

|

V |

|

CLK |

|

CLK |

|

OGND |

|

|

I |

|

I |

|

CCA4 |

|

|

|

|

|

|

|

CCD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

43 |

|

42 |

|

41 |

|

40 |

|

39 |

|

38 |

|

37 |

|

36 |

|

35 |

|

34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n.c. 1

VCCA1 2

VCCA3 3

AGND3 4

n.c. 5

TDA8768H

n.c. 6

n.c. 7

n.c. 8

VCCA2 9

AGND2 10

Vref 11

12 |

|

13 |

|

14 |

|

15 |

|

16 |

|

17 |

|

18 |

|

19 |

|

20 |

|

21 |

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

n.c. |

|

n.c. |

|

n.c. |

|

CCD2 |

|

n.c. |

|

DGND2 |

|

OTC |

|

CE |

|

IR |

|

D11 |

|

D10 |

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

V |

|

|

|

|

|

|

|

Fig.2 Pin configuration.

33 VCCO

32 D0

31 D1

30 D2

29 D3

28 D4

27 D5

26 D6

25 D7

24 D8

23 D9

MGR469

1998 Aug 26 |

5 |

Philips Semiconductors |

Preliminary specification |

|

|

12-bit high-speed Analog-to-Digital

TDA8768

Converter (ADC)

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

MAX. |

UNIT |

|

|

|

|

|

|

VCCA |

analog supply voltage |

note 1 |

−0.3 |

+7.0 |

V |

VCCD |

digital supply voltage |

note 1 |

−0.3 |

+7.0 |

V |

VCCO |

output supply voltage |

note 1 |

−0.3 |

+7.0 |

V |

VCC |

supply voltage difference |

|

|

|

|

|

VCCA − VCCD |

|

−1.0 |

+1.0 |

V |

|

VCCD − VCCO |

|

−1.0 |

+4.0 |

V |

|

VCCA − VCCO |

|

−1.0 |

+4.0 |

V |

VI |

input voltage at pins 42 and 43 |

referenced to AGND |

0.3 |

VCCA |

V |

Vi(p-p) |

input voltage at pins 35 and 36 for |

|

− |

VCCD |

V |

|

differential clock drive (peak-to-peak |

|

|

|

|

|

value) |

|

|

|

|

|

|

|

|

|

|

IO |

output current |

|

− |

10 |

mA |

Tstg |

storage temperature |

|

−55 |

+150 |

°C |

Tamb |

operating ambient temperature |

|

−10 |

+85 |

°C |

Tj |

junction temperature |

|

− |

150 |

°C |

Note

1. The supply voltages VCCA, VCCD and VCCO may have any value between −0.3 V and +7.0 V provided that the supply voltage differences VCC are respected.

HANDLING

Inputs and outputs are protected against electrostatic discharges in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling integrated circuits.

THERMAL CHARACTERISTICS

SYMBOL |

PARAMETER |

CONDITION |

VALUE |

UNIT |

|

|

|

|

|

Rth(j-a) |

thermal resistance from junction to ambient |

in free air |

75 |

K/W |

1998 Aug 26 |

6 |

Loading...

Loading...