Philips tda3654 DATASHEETS

INTEGRATED CIRCUITS

DATA SHEET

TDA3654

TDA3654Q

Vertical deflection and guard circuit (110˚)

Product specification |

|

March 1991 |

|||||

File under Integrated Circuits, IC02 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Philips Semiconductors |

Product specification |

|

|

Vertical deflection and guard circuit |

TDA3654 |

(110˚) |

TDA3654Q |

|

|

|

|

GENERAL DESCRIPTION

The TDA3654 is a full performance vertical deflection output circuit for direct drive of the deflection coils and can be used for a wide range of 90° and 110° deflection systems.

A guard circuit is provided which blanks the picture tube screen in the absence of deflection current.

Features

∙Direct drive to the deflection coils

∙90° and 110° deflection system

∙Internal blanking guard circuit

∙Internal voltage stabilizer

QUICK REFERENCE DATA

Output voltage

Output current (peak-to-peak)

Supply voltage

Guard circuit output voltage

Operating ambient temperature range

Storage temperature

V5-2 |

max. |

60 |

V |

I5(p-p) |

max. |

3 |

A |

V9-2 |

max. |

40 |

V |

V7-2 |

max. |

5,6 |

V |

Tamb |

−25 to +60 |

°C |

|

Tstg |

−55 to +150 |

°C |

|

THERMAL RESISTANCE |

|

|

|

|

From junction to mounting base |

Rth j-mb |

3,5 to 4 |

K/W |

|

PACKAGE OUTLINES |

|

|

|

|

TDA3654 |

: 9-lead SIL; plastic power (SOT131) (1). |

|

|

|

TDA3654Q |

: 9-lead SIL bent to DIL; plastic power (SOT157) (2). |

|

|

|

Notes

1.SOT131-2; 1997 January 07

2.SOT157-2; 1997 January 07

March 1991 |

2 |

Philips Semiconductors |

Product specification |

|

|

Vertical deflection and guard circuit (110˚)

TDA3654

TDA3654Q

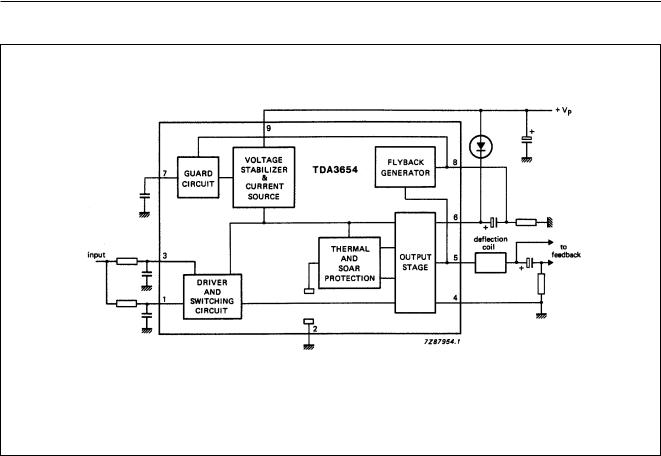

Fig.1 Block diagram.

March 1991 |

3 |

Philips Semiconductors |

Product specification |

|

|

Vertical deflection and guard circuit (110˚)

TDA3654

TDA3654Q

FUNCTIONAL DESCRIPTION

Output stage and protection circuits

The output stage consists of two Darlington configurations in class B arrangement. Each output transistor can deliver 1,5 A maximum and the VCEO is 60 V.

Protection of the output stage is such that the operation of the transistors remains well within the SOAR area in all circumstances at the output pin, (pin 5). This is obtained by the cooperation of the thermal protection circuit, the current-voltage detector and the short circuit protection.

Special measures in the internal circuit layout give the output transistors extra solidity, this is illustrated in Fig.5 where typical SOAR curves of the lower output transistor are given. The same curves also apply for the upper output device. The supply for the output stage is fed to pin 6 and the output stage ground is connected to pin 4.

Driver and switching circuit

Pin 1 is the input for the driver of the output stage. The signal at pin 1 is also applied to pin 3 which is the input of a switching circuit (pin 1 and 3 are connected via external resistors).

This switching circuit rapidly turns off the lower output stage when the flyback starts and it, therefore, allows a quick start of the flyback generator. The maximum required input signal for the maximum output current peak-to-peak value of 3 A is only 3 V, the sum of the currents in pins 1 and 3 is then maximum 1 mA.

Flyback generator

During scan, the capacitor between pins 6 and 8 is charged to a level which is dependent on the value of the resistor at pin 8 (see Fig.1).

When the flyback starts and the voltage at the output pin (pin 5) exceeds the supply voltage, the flyback generator is activated.

The supply voltage is then connected in series, via pin 8, with the voltage across the capacitor during the flyback period. This implies that during scan the supply voltage can be reduced to the required scan voltage plus saturation voltage of the output transistors.

The amplitude of the flyback voltage can be chosen by changing the value of the external resistor at pin 8.

It should be noted that the application is chosen such that the lowest voltage at pin 8 is > 1,5 V, during normal operation.

Guard circuit

When there is no deflection current, for any reason, the voltage at pin 8 becomes less than 1 V, the guard circuit will produce a d.c. voltage at pin 7. This voltage can be used to blank the picture tube, so that the screen will not burn in.

Voltage stabilizer

The internal voltage stabilizer provides a stabilized supply of 6 V to drive the output stage, so the drive current is not affected by supply voltage variations.

March 1991 |

4 |

Philips Semiconductors |

Product specification |

|

|

Vertical deflection and guard circuit (110˚)

TDA3654

TDA3654Q

RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134).

Pins 2 and 4 are externally connected to ground.

Voltages

Output voltage

Supply voltage

Supply voltage output stage

Input voltage

Input voltage switching circuit

External voltage at pin 7

Currents

Repetitive peak output current

Non-repetitive peak output current (note 1)

Repetitive peak output current of flyback generator

Non-repetitive peak output current of flyback generator (note 1)

Temperatures

Storage temperature range

Operating ambient temperature range (see Fig.3) Operating junction temperature range

(the output current at pin 5 should not exceed 2.5A)

V5-4 |

|

0 to 60 |

V |

V9-4 |

|

0 to 40 |

V |

V6-4 |

|

0 to 60 |

V |

V1-2 |

|

0 to V9-4 |

V |

V3-2 |

|

0 to V9-4 |

V |

V7-2 |

|

0 to 5,6 |

V |

± I5RM |

max. |

1,5 |

A |

± I5SM |

max. |

3 |

A |

I8RM |

max. |

+ 1,5 |

A |

|

|

− 1,6 |

A |

± I8SM |

max. |

3 |

A |

Tstg |

−65 to + 150 |

°C |

|

Tamb |

−25 to + 60 |

°C |

|

Tj |

−25 to + 150 |

°C |

|

March 1991 |

5 |

Loading...

Loading...