Philips TDA8002G-5-C2, TDA8002BT-3-C2, TDA8002AT-5-C2, TDA8002G-3-C2, TDA8002AT-3-C2 Datasheet

INTEGRATED CIRCUITS

DATA SHEET

TDA8002

IC card interface

Product specification |

1997 Nov 04 |

Supersedes data of 1997 Mar 13

File under Integrated Circuits, IC02

Philips Semiconductors |

Product specification |

|

|

IC card interface |

TDA8002 |

|

|

|

|

FEATURES

∙Single supply voltage interface (3.3 or 5 V environment)

∙Low-power sleep mode

∙Three specific protected half-duplex bidirectional buffered I/O lines

∙VCC regulation (5 V ±5%, ICC <65 mA at VDD = 5 V, with controlled rise and fall times

∙Thermal and short-circuit protections with current limitations

∙Automatic ISO 7816 activation and deactivation sequences

∙Enhanced ESD protections on card side (>6 kV)

∙Clock generation for the card up to 12 MHz with synchronous frequency changes

∙Clock generation up to 20 MHz (auxiliary clock)

∙Synchronous and asynchronous cards (memory and smart cards)

∙ISO 7816, GSM11.11 compatibility and EMV (Europay, Mastercard, Visa) compliant

∙Step-up converter for VCC generation

QUICK REFERENCE DATA

∙Supply supervisor for spikes elimination and emergency deactivation.

APPLICATIONS

∙IC card readers for:

–GSM applications

–banking

–electronic payment

–identification

–Pay TV

–road tolling.

GENERAL DESCRIPTION

The TDA8002 is a complete low-power, analog interface for asynchronous and synchronous cards. It can be placed between the card and the microcontroller. It performs all supply, protection and control functions. It is directly compatible with ISO 7816, GSM11.11 and EMV specifications.

SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

|

|

Supply |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDDA |

analog supply voltage |

|

3.0 |

5 |

6.5 |

V |

IDD |

supply current |

sleep mode |

− |

− |

150 |

μA |

|

|

idle mode; fCLK = 2.5 MHz; |

− |

− |

6 |

mA |

|

|

fCLKOUT = 10 MHz; VDD = 5 V |

|

|

|

|

|

|

active mode; fCLK = 2.5 MHz; |

− |

− |

9 |

mA |

|

|

fCLKOUT = 10 MHz; VDD = 5 V |

|

|

|

|

|

|

active mode; fCLK = 2.5 MHz; |

− |

− |

12 |

mA |

|

|

fCLKOUT = 10 MHz; VDD = 3 V |

|

|

|

|

Card supply |

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC(O) |

output voltage |

DC load <65 mA |

4.75 |

− |

5.25 |

V |

ICC(O) |

output current |

VCC short-circuited to GND |

− |

− |

100 |

mA |

General |

|

|

|

|

|

|

|

|

|

|

|

|

|

fCLK |

card clock frequency |

|

0 |

− |

12 |

MHz |

Tde |

deactivation cycle time |

|

60 |

80 |

100 |

μs |

Ptot |

continuous total power dissipation |

|

|

|

|

|

|

TDA8002AT; TDA8002BT |

Tamb = −25 to +85 °C |

− |

− |

0.56 |

W |

|

TDA8002G |

Tamb = −25 to +85 °C |

− |

− |

0.46 |

W |

Tamb |

operating ambient temperature |

|

−25 |

− |

+85 |

°C |

1997 Nov 04 |

2 |

Philips Semiconductors |

|

|

Product specification |

||

|

|

|

|

|

|

IC card interface |

|

|

|

TDA8002 |

|

|

|

|

|

|

|

ORDERING INFORMATION |

|

|

|

|

|

|

|

|

|

|

|

TYPE NUMBER(1) |

|

|

PACKAGE |

|

|

|

|

|

|

|

|

MARKING |

NAME |

DESCRIPTION |

|

VERSION |

|

|

|

||||

|

|

|

|

|

|

TDA8002AT/3/C2(2) |

TDA8002AT/3 |

SO28 |

plastic small outline package; 28 leads; |

|

SOT136-1 |

|

|

|

body width 7.5 mm |

|

|

TDA8002AT/5/C2(3) |

TDA8002AT/5 |

|

|

|

|

TDA8002BT/3/C2(2) |

TDA8002BT/3 |

|

|

|

|

TDA8002BT/5/C2(3) |

TDA8002BT/5 |

|

|

|

|

TDA8002G/3/C2(2) |

80023 |

LQFP32 |

plastic low profile quad flat package; 32 leads; |

|

SOT401-1 |

|

|

|

body 5 × 5 × 1.4 mm |

|

|

TDA8002G/5/C2(3) |

80025 |

|

|

|

|

Notes

1.The /3 or /5 suffix indicates the voltage supervisor option.

2.The /3 version can be used with a 3 or 5 V power supply environment (see Chapter “Functional description”).

3.The /5 version can be used with a 5 V power supply environment.

1997 Nov 04 |

3 |

Philips Semiconductors |

Product specification |

|

|

IC card interface |

TDA8002 |

|

|

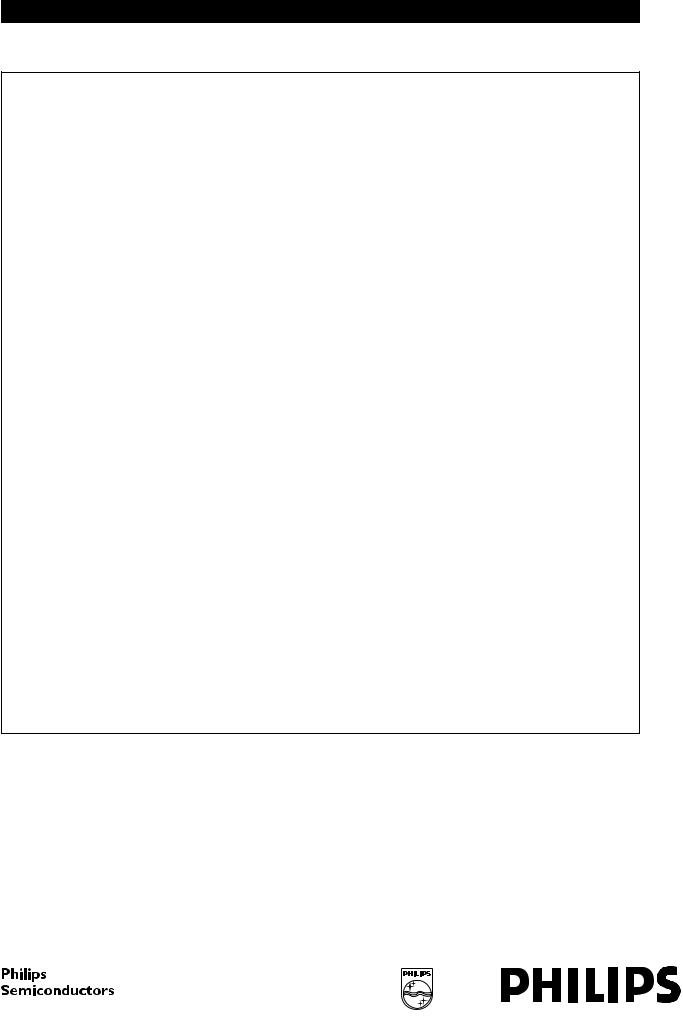

BLOCK DIAGRAM

VDDD |

|

|

|

|

VDDA |

|

|

|

|

|

|

100 nF |

|

|

|

100 nF |

100 nF |

|

|

||||

|

|

|

|

|

|

|

S1 |

S2 |

|

|

|

28 |

|

|

|

|

13 |

|

14 |

12 |

|

|

|

4 |

|

SUPPLY |

|

STEP-UP CONVERTER |

|

|

|||||

|

|

|

|

|

|

||||||

ALARM |

INTERNAL |

|

|

|

|

|

|

|

|||

3 |

VREF |

|

|

|

|

|

|

||||

REFERENCE |

INTERNAL OSCILLATOR |

15 |

VUP |

||||||||

ALARM |

|||||||||||

|

|

|

|

|

|

|

fINT |

|

100 nF |

||

|

VOLTAGE SENSE |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

ALARM |

EN1 |

CLKUP |

|

|

|

||

26 |

|

|

|

|

|

|

EN2 |

VCC |

|

|

|

|

|

|

|

|

|

|

23 |

|

|||

OFF |

|

|

|

|

|

|

PVCC |

VCC |

|||

25 |

|

|

|

|

|

|

GENERATOR |

|

|||

RSTIN |

|

|

|

|

|

|

|

|

|

100 |

|

24 |

|

|

|

|

|

|

|

|

|

nF |

|

CMDVCC |

|

|

|

|

|

|

|

|

|

|

|

27 |

|

|

|

|

|

|

EN5 |

RST |

22 |

|

|

MODE |

|

|

|

|

|

|

RST |

||||

|

|

|

|

|

|

|

|

BUFFER |

|

||

|

|

|

|

SEQUENCER |

|

|

|

||||

6 |

|

|

|

|

|

19 |

|

||||

|

|

|

|

|

|

|

|

PRES |

|||

|

|

|

|

|

|

|

|

|

|||

CLKDIV1 |

|

|

|

|

|

|

|

|

18 |

|

|

7 |

|

|

|

|

|

|

|

|

PRES |

||

CLKDIV2 |

|

|

|

|

|

|

|

|

|

||

5 |

|

|

HORSEQ |

|

|

|

|

|

|

||

CLKSEL |

CLOCK |

|

|

EN4 |

|

|

|

||||

|

|

|

|

|

|

|

|||||

|

CIRCUITRY |

|

|

|

|

CLOCK |

21 |

|

|||

8 |

|

|

|

|

|

CLK |

|||||

STROBE |

|

|

|

|

|

|

|

BUFFER |

|

||

|

|

|

|

|

|

|

|

|

|||

9 |

|

|

|

|

|

|

|

|

|

|

|

CLKOUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

|

||

30 |

|

|

|

EN3 |

|

THERMAL |

|

|

|

||

XTAL1 |

OSCILLATOR |

|

|

PROTECTION |

|

|

|

||||

31 |

|

|

|

|

|

|

|

|

|||

XTAL2 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

I/O |

20 |

AUX1 |

|

AUX1UC |

|

|

|

|

|

|

TRANSCEIVER |

|

|||

|

|

|

|

|

|

|

|

|

|||

|

TDA8002G |

|

|

|

|

|

|

|

|||

2 |

|

|

|

|

|

|

|

I/O |

17 |

AUX2 |

|

AUX2UC |

|

|

|

|

|

|

TRANSCEIVER |

|

|||

|

|

|

|

|

|

|

|

|

|||

32 |

|

|

|

|

|

|

|

I/O |

16 |

I/O |

|

I/OUC |

|

|

|

|

|

|

TRANSCEIVER |

|

|||

|

|

|

|

|

|

|

|

|

|||

|

10 |

|

29 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGE730 |

|

|

|

DGND1 |

DGND2 |

AGND |

|

|

|

|

|

|

||

All capacitors are mandatory. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Fig.1 Block diagram (TDA8002G). |

|

|

||||||

1997 Nov 04 |

|

|

|

|

4 |

|

|

|

|

|

|

Philips Semiconductors |

|

|

|

Product specification |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

IC card interface |

|

|

TDA8002 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

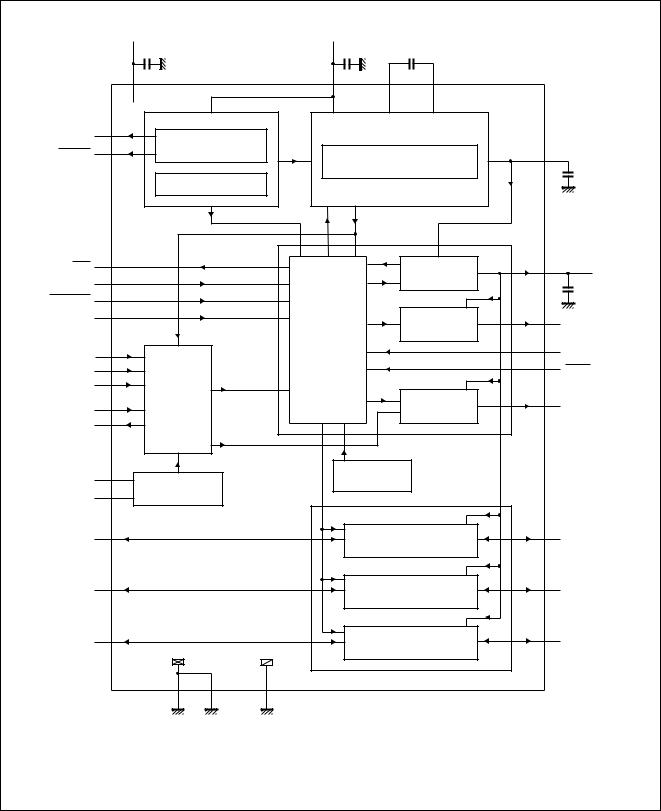

PINNING |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

SYMBOL |

|

|

PIN |

|

I/O |

DESCRIPTION |

||||

|

|

|

|

|

|||||||

|

TYPE A |

|

TYPE B |

TYPE G |

|||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||||

|

XTAL1 |

1 |

|

1 |

30 |

I/O |

crystal connection or input for external clock |

||||

|

|

|

|

|

|

|

|

||||

|

XTAL2 |

2 |

|

2 |

31 |

I/O |

crystal connection |

||||

|

|

|

|

|

|

|

|

||||

|

I/OUC |

3 |

|

3 |

32 |

I/O |

data I/O line to and from microcontroller |

||||

|

|

|

|

|

|

|

|

||||

|

AUX1UC |

4 |

|

4 |

1 |

I/O |

auxiliary line to and from microcontroller for synchronous |

||||

|

|

|

|

|

|

|

|

|

|

|

applications |

|

|

|

|

|

|

|

|

||||

|

AUX2UC |

5 |

|

− |

2 |

I/O |

auxiliary line to and from microcontroller for synchronous |

||||

|

|

|

|

|

|

|

|

|

|

|

applications |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

− |

|

5 |

3 |

O |

open drain NMOS reset output for microcontroller (active LOW) |

|

ALARM |

|

|

||||||||

|

|

|

|

|

|

|

|

||||

|

ALARM |

6 |

|

6 |

4 |

O |

open drain PMOS reset output for microcontroller (active |

||||

|

|

|

|

|

|

|

|

|

|

|

HIGH) |

|

|

|

|

|

|

|

|

||||

|

CLKSEL |

7 |

|

7 |

5 |

I |

control input signal for CLK (LOW = XTAL oscillator; |

||||

|

|

|

|

|

|

|

|

|

|

|

HIGH = STROBE input) |

|

|

|

|

|

|

|

|

||||

|

CLKDIV1 |

8 |

|

8 |

6 |

I |

control input with CLKDIV2 for choosing CLK frequency |

||||

|

|

|

|

|

|

|

|

||||

|

CLKDIV2 |

9 |

|

9 |

7 |

I |

control input with CLKDIV1 for choosing CLK frequency |

||||

|

|

|

|

|

|

|

|

||||

|

STROBE |

10 |

|

10 |

8 |

I |

external clock input for synchronous applications |

||||

|

|

|

|

|

|

|

|

||||

|

CLKOUT |

11 |

|

11 |

9 |

O |

clock output (see Table 1) |

||||

|

|

|

|

|

|

|

|

||||

|

DGND1 |

12 |

|

12 |

10 |

supply |

digital ground 1 |

||||

|

|

|

|

|

|

|

|

||||

|

AGND |

13 |

|

13 |

11 |

supply |

analog ground |

||||

|

|

|

|

|

|

|

|

||||

|

S2 |

14 |

|

14 |

12 |

I/O |

capacitance connection for voltage doubler |

||||

|

|

|

|

|

|

|

|

||||

|

VDDA |

15 |

|

15 |

13 |

supply |

analog supply voltage |

||||

S1 |

16 |

|

16 |

14 |

I/O |

capacitance connection for voltage doubler |

|||||

|

|

|

|

|

|

|

|||||

VUP |

17 |

|

17 |

15 |

I/O |

output of voltage doubler (connect to 100 nF) |

|||||

|

|

|

|

|

|

|

|||||

I/O |

18 |

|

18 |

16 |

I/O |

data I/O line to and from card |

|||||

|

|

|

|

|

|

|

|||||

AUX2 |

19 |

|

− |

17 |

I/O |

auxiliary I/O line to and from card |

|||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

20 |

|

19 |

18 |

I |

active LOW card input presence contact |

|

PRES |

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||

|

PRES |

− |

|

20 |

19 |

I |

active HIGH card input presence contact |

||||

|

|

|

|

|

|

|

|

||||

|

AUX1 |

21 |

|

21 |

20 |

I/O |

auxiliary I/O line to and from card |

||||

|

|

|

|

|

|

|

|

||||

|

CLK |

22 |

|

22 |

21 |

O |

clock to card output (C3) (see Table 1) |

||||

|

|

|

|

|

|

|

|

||||

|

RST |

23 |

|

23 |

22 |

O |

card reset output (C2) |

||||

|

|

|

|

|

|

|

|

||||

|

VCC |

24 |

|

24 |

23 |

O |

supply for card (C1) (decouple with 100 nF) |

||||

|

|

|

|

|

|

25 |

|

25 |

24 |

I |

active LOW start activation sequence input from |

|

CMDVCC |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

microcontroller |

|

|

|

|

|

|

|

|

||||

|

RSTIN |

26 |

|

26 |

25 |

I |

card reset input from microcontroller |

||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

27 |

|

27 |

26 |

O |

open drain NMOS interrupt output to microcontroller (active |

|

OFF |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

LOW) |

|

|

|

|

|

|

|

|

||||

|

MODE |

28 |

|

28 |

27 |

I |

operating mode selection input (HIGH = normal; LOW = sleep) |

||||

|

|

|

|

|

|

|

|

||||

|

VDDD |

− |

|

− |

28 |

supply |

digital supply voltage |

||||

DGND2 |

− |

|

− |

29 |

supply |

digital ground 2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

1997 Nov 04 |

5 |

Philips Semiconductors |

Product specification |

|

|

IC card interface |

TDA8002 |

|

|

handbook, halfpage |

|

|

|

|

|

|

|

|

|

handbook, halfpage |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

XTAL1 |

1 |

|

28 |

MODE |

|

|

XTAL1 |

1 |

|

28 |

MODE |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL2 |

2 |

|

27 |

OFF |

|

|

XTAL2 |

2 |

|

27 |

OFF |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

I/OUC |

3 |

|

|

RSTIN |

||||||

I/OUC |

3 |

|

26 |

RSTIN |

|

|

|

26 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AUX1UC |

4 |

|

25 |

CMDVCC |

|

AUX1UC |

4 |

|

25 |

CMDVCC |

|||||||||||

|

|

|

|

VCC |

|

|

|

|

|

|

|

VCC |

|||||||||

AUX2UC |

5 |

|

24 |

|

ALARM |

5 |

|

24 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ALARM |

6 |

|

23 |

RST |

|

ALARM |

6 |

|

23 |

RST |

|||||||||||

|

|

|

|

|

|

|

|

|

|

CLKSEL |

|

|

|

CLK |

|||||||

CLKSEL |

7 |

TDA8002A |

22 |

CLK |

|

7 |

TDA8002B |

22 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

||

CLKDIV1 |

8 |

|

21 |

AUX1 |

|

CLKDIV1 |

|

21 |

AUX1 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

CLKDIV2 |

9 |

|

|

PRES |

|||||||

CLKDIV2 |

9 |

|

20 |

PRES |

|

|

20 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

STROBE |

10 |

|

19 |

AUX2 |

|

STROBE |

10 |

|

19 |

PRES |

|||||||||||

|

|

|

|

|

|

|

|

|

|

CLKOUT |

11 |

|

|

I/O |

|||||||

CLKOUT |

11 |

|

18 |

I/O |

|

|

18 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

DGND1 |

12 |

|

|

VUP |

|||||||

DGND1 |

12 |

|

17 |

VUP |

|

|

17 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

AGND |

13 |

|

|

S1 |

||||||

AGND |

13 |

|

16 |

S1 |

|

|

|

16 |

|||||||||||||

|

|

|

|

VDDA |

|

|

|

|

|

|

|

VDDA |

|||||||||

S2 |

14 |

|

15 |

|

|

S2 |

14 |

|

15 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MGE731 |

|

|

|

|

|

|

|

|

|

|

MGE732 |

|

|

|

|

|

|

||

Fig.2 Pin configuration (TDA8002A). |

|

Fig.3 Pin configuration (TDA8002B). |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

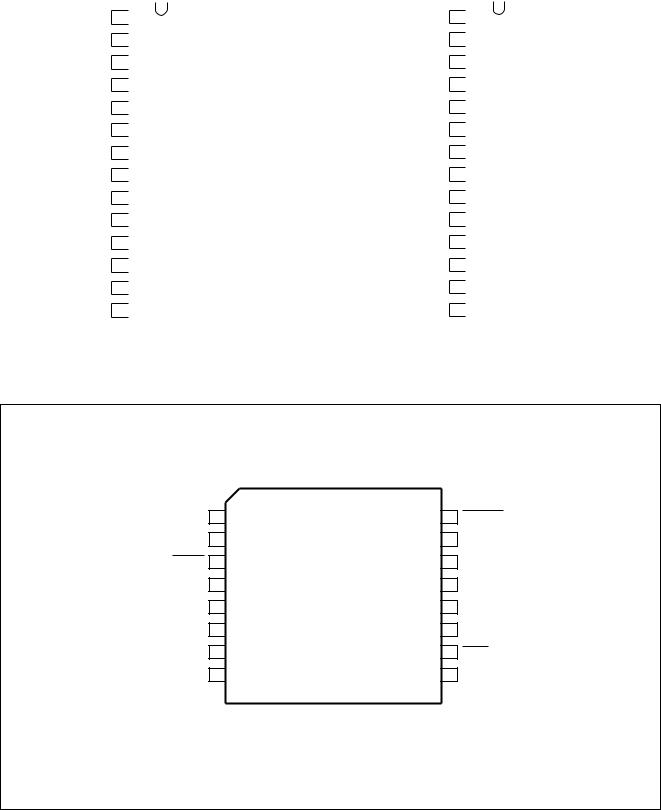

I/OUC |

|

XTAL2 |

|

XTAL1 |

|

DGND2 |

|

V |

|

MODE |

|

OFF |

|

RSTIN |

|

|

|

|

|

|

|

|

DDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

31 |

|

30 |

|

29 |

|

28 |

|

27 |

|

26 |

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AUX1UC 1

AUX2UC 2

ALARM 3

ALARM 4

TDA8002G

CLKSEL 5

CLKDIV1 6

CLKDIV2 7

STROBE 8

9 |

|

10 |

|

11 |

|

12 |

|

13 |

|

14 |

|

15 |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLKOUT |

|

DGND1 |

|

AGND |

|

S2 |

|

V |

|

S1 |

|

VUP |

|

I/O |

|

|

|

|

|

|

|

|

DDA |

|

|

|

|

|

|

24 CMDVCC

23 VCC

22 RST

21 CLK

20 AUX1

19 PRES

18 PRES

17 AUX2

MGE733

Fig.4 Pin configuration (TDA8002G).

1997 Nov 04 |

6 |

Philips Semiconductors |

Product specification |

|

|

IC card interface |

TDA8002 |

|

|

FUNCTIONAL DESCRIPTION

Power supply

The supply pins for the chip are VDDA, VDDD, AGND, DGND1 and DGND2. VDDA and VDDD (i.e. VDD) should be in the range of 3.0 to 6.5 V. All card contacts remain

inactive during power-up or power-down.

On power-up, the logic is reset by an internal signal. The sequencer is not activated until VDD reaches

Vth2 + Vhys2 (see Fig.5). When VDD falls below Vth2, an automatic deactivation sequence of the contacts is

performed.

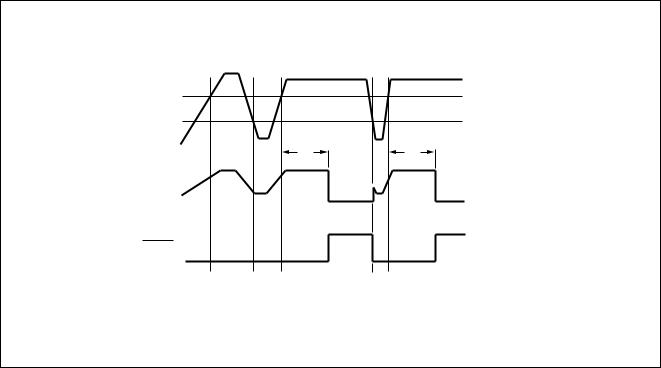

Supply voltage supervisor (VDD)

This block surveys the VDD supply. A defined reset pulse of 10 ms minimum (tW) can be retriggered and is delivered on the ALARM outputs during power-up or power-down of VDD (see Fig.5). This signal is also used for eliminating the spikes on card contacts during power-up or power-down.

When VDD reaches Vth2 + Vhys2, an internal delay is started. The ALARM outputs are active until this delay has

expired. When VDD falls below Vth2, ALARM is activated and a deactivation sequence of the contacts is performed.

For 3 V supply, the supervisor option must be chosen at 3 V. For 5 V supply, both options (3 or 5 V) may be chosen depending on the application.

Clock circuitry

The TDA8002 supports both synchronous and asynchronous cards (I2C-bus memories requiring an acknowledge signal from the master are not supported). There are three methods to clock the circuitry:

∙Apply a clock signal to pin STROBE

∙Use of an internal RC oscillator

∙Use of a quartz oscillator which should be connected between pins XTAL1 and XTAL2.

When CLKSEL is HIGH, the clock should be applied on the STROBE pin, and when CLKSEL is LOW, one of the internal oscillators is used.

When an internal clock is used, the clock output is available on pin CLKOUT. The RC oscillator is selected by making CLKDIV1 HIGH and CLKDIV2 LOW. The clock output to the card is available on pin CLK. The frequency of the card clock can be the input frequency divided by

2 or 4, STOP LOW or 1.25 MHz, depending on the states of CLKDIV1 or CLKDIV2 (see Table 1).

Do not change CLKSEL during activation. When in low-power (sleep) mode, the internal oscillator frequency which is available on pin CLKOUT is lowered to approximately 16 kHz for power-economy purposes.

handbook, full pagewidth

VDD

ALARM

ALARM

|

Vth2 + Vhys2 |

|

Vth2 |

tW |

tW |

|

MGE734 |

Fig.5 Alarm as a function of VDD (pulse width 10 ms).

1997 Nov 04 |

7 |

Philips Semiconductors |

|

|

|

|

Product specification |

||

|

|

|

|

|

|

|

|

IC card interface |

|

|

|

|

TDA8002 |

||

|

|

|

|

|

|

|

|

Table 1 Clock circuitry definition |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

MODE |

|

CLKSEL |

CLKDIV1 |

CLKDIV2 |

FREQUENCY |

|

FREQUENCY |

|

OF CLK |

|

OF CLKOUT |

||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

HIGH |

|

LOW |

HIGH |

LOW |

1¤2fint |

|

1¤2fint |

HIGH |

|

LOW |

LOW |

LOW |

1¤4fxtal |

|

fxtal |

HIGH |

|

LOW |

LOW |

HIGH |

1¤2fxtal |

|

fxtal |

HIGH |

|

LOW |

HIGH |

HIGH |

STOP LOW |

|

fxtal |

HIGH |

|

HIGH |

X(1) |

X(1) |

STROBE |

|

f |

|

|

|

|

|

|

|

xtal |

LOW(2) |

|

X(1) |

X(1) |

X(1) |

STOP LOW |

|

1¤2fint(3) |

Notes

1.X = don’t care.

2.In low-power mode.

3.fint = 32 kHz in low-power mode.

I/O circuitry

The three I/O transceivers are identical. The state is HIGH for all I/O pins (i.e. I/O, I/OUC, AUX1, AUX1UC, AUX2 and AUX2UC). Pin I/O is referenced to VCC and pin I/OUC to VDD, thus ensuring proper operation in case VCC ¹ VDD.

The first side on which a falling edge is detected becomes a master (input). An anti-latch circuitry first disables the detection of the falling edge on the other side, which becomes slave (output).

After a delay time td (about 50 ns), the logic 0 present on the master side is transferred on the slave side.

When the input is back to HIGH level, a current booster is turned on during the delay td on the output side and then both sides are back to their idle state, ready to detect the next logic 0 on any side.

In case of a conflict, both lines may remain LOW until the software enables the lines to be HIGH. The anti-latch circuitry ensures that the lines do not remain LOW if both sides return HIGH, regardless of the prior conditions. The maximum frequency on the lines is approximately

1 MHz.

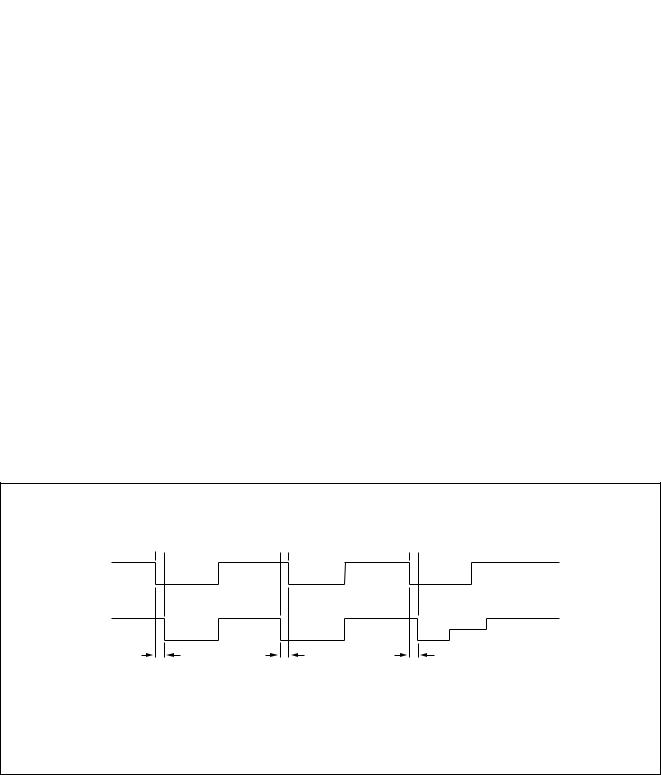

handbook, full pagewidthI/O

I/OUC

td |

td |

td |

conflict |

idle |

|

|

|

|

MGD703 |

Fig.6 Master and slave signals.

1997 Nov 04 |

8 |

Philips Semiconductors |

Product specification |

|

|

IC card interface |

TDA8002 |

|

|

Logic circuitry

After power-up, the circuit has six possible states of operation. Table 1 shows the sequence of these states.

IDLE MODE

After reset, the circuit enters the idle mode.

A minimum number of functions in the circuit are active while waiting for the microcontroller to start a session:

∙All card contacts are inactive

∙I/OUC, AUX1UC and AUX2UC are high-impedance

∙Oscillator XTAL runs, delivering CLKOUT

∙Voltage supervisor is active.

LOW-POWER (SLEEP) MODE

When pin MODE goes LOW, the circuit enters the low-power (sleep) mode. As long as pin MODE is LOW, no activation is possible.

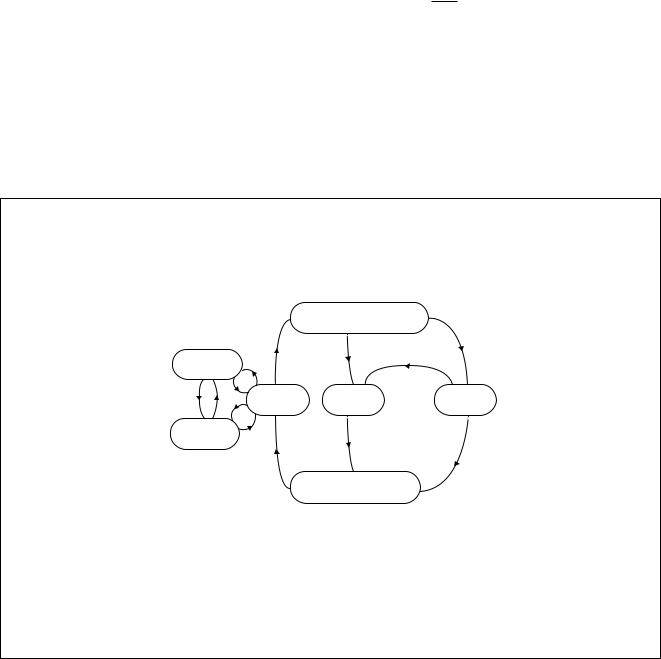

State diagram

If pin MODE goes LOW in the active mode, a normal deactivation sequence is performed before entering low-power mode. When pin MODE goes HIGH, the circuit enters normal operation after a delay of at least 6 ms (96 cycles of CLKOUT). During this time the CLKOUT remains at 16 kHz.

∙All card contacts are inactive

∙Oscillator XTAL does not run

∙The VDD supervisor, ALARM output, card presence detection and OFF output remain functional

∙Internal oscillator is slowed to 32 kHz, CLKOUT providing 16 kHz.

ACTIVE MODE

When the activation sequence is completed, the TDA8002 will be in the active mode. Data is exchanged between the card and the microcontroller via the I/O lines.

handbook, full pagewidth

ACTIVATION

POWER

OFF

IDLE |

FAULT |

ACTIVE |

|

MODE |

MODE |

||

|

LOW-POWER

MODE

DEACTIVATION

MGE735

Fig.7 State diagram.

1997 Nov 04 |

9 |

Loading...

Loading...