Philips TDA4665T-V5, TDA4665T-V4, TDA4665T-V3, TDA4665-V5, TDA4665-V4 Datasheet

...

INTEGRATED CIRCUITS

TDA4665

Baseband delay line

Product specification |

1996 Dec 17 |

Supersedes data of 1995 Oct 30

File under Integrated Circuits, IC02

Philips Semiconductors |

Product specification |

|

|

|

|

Baseband delay line |

TDA4665 |

|

|

|

|

FEATURES

∙Two comb filters, using the switched-capacitor technique, for one line delay time (64 μs)

∙Adjustment-free application

∙No crosstalk between SECAM colour carriers (diaphoty)

∙Handles negative or positive colour-difference input signals

∙Clamping of AC-coupled input signals (±(R−Y) and

±(B−Y))

∙VCO without external components

∙3 MHz internal clock signal derived from a 6 MHz CCO, line-locked by the sandcastle pulse (64 μs line)

∙Sample-and-hold circuits and low-pass filters to suppress the 3 MHz clock signal

∙Addition of delayed and non-delayed output signals

∙Output buffer amplifiers

∙Comb filtering functions for NTSC colour-difference signals to suppress cross-colour.

QUICK REFERENCE DATA

GENERAL DESCRIPTION

The TDA4665 is an integrated baseband delay line circuit with one line delay. It is suitable for decoders with colour-difference signal outputs ±(R−Y) and ±(B−Y).

SYMBOL |

|

|

PARAMETER |

MIN. |

TYP. |

MAX. |

UNIT |

|

|

|

|

|

|

|

|

VP1 |

analog supply voltage (pin 9) |

4.5 |

5 |

6 |

V |

||

VP2 |

digital supply voltage (pin 1) |

4.5 |

5 |

6 |

V |

||

IP(tot) |

total supply current |

− |

5.5 |

7.0 |

mA |

||

Vi(p-p) |

±(R−Y) input signal PAL/NTSC (peak-to-peak value; pin 16) |

− |

525 |

− |

mV |

||

|

±(B−Y) input signal PAL/NTSC (peak-to-peak value; pin 14) |

− |

665 |

− |

mV |

||

|

|

|

|

|

|

|

|

|

±(R−Y) input signal SECAM (peak-to-peak value; pin 16) |

− |

1.05 |

− |

V |

||

|

|

|

|

|

|

|

|

|

±(B−Y) input signal SECAM (peak-to-peak value; pin 14) |

− |

1.33 |

− |

V |

||

|

|

|

|

|

|

|

|

Gv |

gain Vo / Vi of colour-difference output signals |

|

|

|

|

||

|

V11 / V16 for PAL and NTSC |

5.3 |

5.8 |

6.3 |

dB |

||

|

V12 / V14 for PAL and NTSC |

5.3 |

5.8 |

6.3 |

dB |

||

|

V11 / V16 for SECAM |

−0.6 |

−0.1 |

+0.4 |

dB |

||

|

V12 / V14 for SECAM |

−0.6 |

−0.1 |

+0.4 |

dB |

||

ORDERING INFORMATION |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

TYPE |

|

|

PACKAGE |

|

|

|

|

|

|

|

|

|

|

|

|

NUMBER |

NAME |

|

DESCRIPTION |

|

|

VERSION |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

TDA4665 |

DIP16 |

|

plastic dual in-line package; 16 leads (300 mil) |

|

|

SOT38-4 |

|

|

|

|

|

|

|

||

TDA4665T |

SO16 |

|

plastic small outline package; 16 leads; body width 3.9 mm |

|

SOT109-1 |

||

|

|

|

|

|

|

|

|

1996 Dec 17 |

2 |

17 Dec1996 |

|

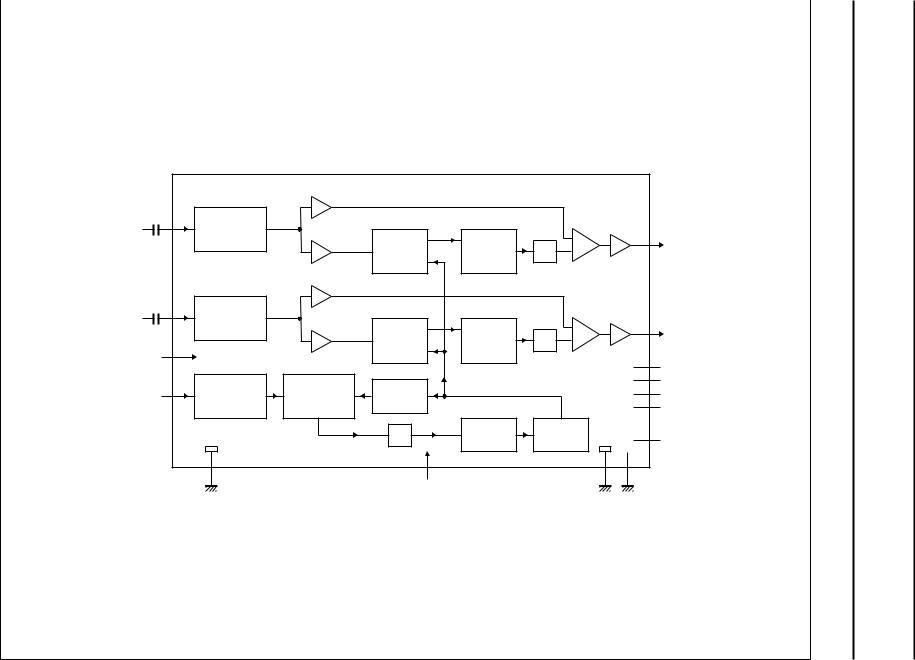

DIAGRAMBLOCK |

±(R−Y) |

16 |

SIGNAL |

|

|

|

|

|

|

|

|

|

CLAMPING |

|

|

|

|

|

11 |

|

||

|

|

|

|

|

|

|

±(R−Y) |

|||

|

|

|

|

LINE |

SAMPLE- |

|

|

|||

|

|

|

|

LP |

|

|

|

|||

|

|

|

|

MEMORY |

AND-HOLD |

|

|

|

|

|

colour-difference |

|

|

|

|

|

|

|

|

||

|

|

pre-amplifiers |

|

|

|

|

|

|

|

|

input signals |

|

|

|

|

addition |

output |

|

colour-difference |

||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

stages |

buffers |

|

output signals |

|

±(B−Y) |

14 |

SIGNAL |

|

|

|

|

|

|

|

|

|

CLAMPING |

|

|

|

|

|

12 |

|

||

3 |

|

|

|

|

|

|

±(B−Y) |

|||

|

|

|

LINE |

SAMPLE- |

|

|

||||

|

|

|

LP |

|

|

|

||||

|

|

|

|

|

|

|

||||

|

9 |

|

|

MEMORY |

AND-HOLD |

|

|

|

|

|

VP1 |

|

|

|

|

|

|

|

|||

analog supply |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

2 |

n.c. |

||

|

|

|

|

|

|

TDA4665 |

|

6 |

||

|

|

|

FREQUENCY |

|

3 MHz shifting clock |

|

n.c. |

|||

sandcastle |

5 |

SANDCASTLE |

DIVIDER |

|

|

13 |

||||

|

|

|

n.c. |

|||||||

pulse input |

|

DETECTOR |

PHASE |

BY 192 |

|

|

|

15 |

||

|

|

|

|

n.c. |

||||||

|

DETECTOR |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

LP |

6 MHz |

DIVIDER |

|

|

7 |

|

|

|

|

|

CCO |

BY 2 |

|

|

i.c. |

||

|

|

|

|

|

|

|

|

|||

|

|

10 |

|

digital supply |

1 |

|

3 |

4, 8 |

|

|

|

|

GND1 |

|

VP2 |

GND2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

MED848 |

||

Fig.1 Block diagram.

line delay Baseband

TDA4665

Semiconductors Philips

specification Product

Philips Semiconductors |

Product specification |

|

|

Baseband delay line |

TDA4665 |

|

|

PINNING

SYMBOL |

PIN |

DESCRIPTION |

|

|

|

VP2 |

1 |

+5 V supply voltage for digital part |

n.c. |

2 |

not connected |

|

|

|

GND2 |

3 |

ground for digital part (0 V) |

|

|

|

i.c. |

4 |

internally connected |

|

|

|

SAND |

5 |

sandcastle pulse input |

|

|

|

n.c. |

6 |

not connected |

|

|

|

i.c. |

7 |

internally connected |

|

|

|

i.c. |

8 |

internally connected |

|

|

|

VP1 |

9 |

+5 V supply voltage for analog part |

GND1 |

10 |

ground for analog part (0 V) |

|

|

|

Vo(R−Y) |

11 |

±(R−Y) output signal |

Vo(B−Y) |

12 |

±(B−Y) output signal |

n.c. |

13 |

not connected |

|

|

|

Vi(B−Y) |

14 |

±(B−Y) input signal |

n.c. |

15 |

not connected |

|

|

|

Vi(R−Y) |

16 |

±(R−Y) input signal |

LIMITING VALUES

handbook, halfpage

VP2 |

1 |

16 |

Vi(R−Y) |

||||

|

|

|

|

|

|

||

n.c. |

2 |

|

|

|

15 |

n.c. |

|

|

|

|

|

|

|

|

|

GND2 |

3 |

|

14 |

Vi(B−Y) |

|||

|

|

|

|

|

|

|

|

i.c. |

4 |

|

13 |

n.c. |

|||

|

|

|

TDA4665 |

|

|

||

SAND |

5 |

|

|

|

12 |

Vo(B−Y) |

|

|

|

|

|

|

|

|

|

n.c. |

6 |

|

|

|

11 |

Vo(R−Y) |

|

|

|

|

|

|

|

|

|

i.c. |

7 |

|

|

|

10 |

GND1 |

|

|

|

|

|

|

|

|

|

i.c. |

8 |

|

9 |

VP1 |

|||

|

|

|

|

|

|

|

|

|

|

|

MED849 |

|

|||

Fig.2 Pin configuration.

In accordance with the Absolute Maximum Rating System (IEC 134). Ground pins 3 and 10 connected together.

SYMBOL |

PARAMETER |

MIN. |

MAX. |

UNIT |

|

|

|

|

|

VP1 |

analog supply voltage (pin 9) |

−0.5 |

+7 |

V |

VP2 |

digital supply voltage (pin 1) |

−0.5 |

+7 |

V |

V5 |

voltage on pin 5 |

−0.5 |

VP + 1.0 |

V |

Vn |

voltage on pins 11, 12, 14 and 16 |

−0.5 |

VP |

V |

Tstg |

storage temperature |

−25 |

+150 |

°C |

Tamb |

operating ambient temperature |

0 |

70 |

°C |

VESD |

electrostatic handling for all pins; note 1 |

− |

±500 |

V |

Note

1. Equivalent to discharging a 200 pF capacitor through a 0 Ω series resistor.

THERMAL CHARACTERISTICS

SYMBOL |

PARAMETER |

VALUE |

UNIT |

|

|

|

|

Rth j-a |

thermal resistance from junction to ambient in free air |

|

|

|

SOT38-4 |

75 |

K/W |

|

SOT109-1 |

220 |

K/W |

|

|

|

|

1996 Dec 17 |

4 |

Loading...

Loading...