NSC DS90C032TM, DS90C032MDC, DS90C032E-MIL, DS90C032BW-QML, DS90C032TMX Datasheet

...

June 1998

DS90C032

LVDS Quad CMOS Differential Line Receiver

General Description

The DS90C032 is a quad CMOS differential line receiver designed for applications requiring ultra low power dissipation and high data rates. The device is designed to support data rates in excess of 155.5 Mbps (77.7 MHz) utilizing Low Voltage Differential Signaling (LVDS) technology.

The DS90C032 accepts low voltage (350 mV) differential input signals and translates them to CMOS (TTL compatible) output levels. The receiver supports a TRI-STATE® function that may be used to multiplex outputs. The receiver also supports OPEN, shorted and terminated (100Ω) input Fail-safe. Receiver output will be HIGH for all fail-safe conditions.

The DS90C032 and companion line driver (DS90C031) provide a new alternative to high power psuedo-ECL devices for high speed point-to-point interface applications.

Features

n>155.5 Mbps (77.7 MHz) switching rates

nAccepts small swing (350 mV) differential signal levels

nUltra low power dissipation

n600 ps maximum differential skew (5V, 25ÊC)

n6.0 ns maximum propagation delay

nIndustrial operating temperature range

nMilitary operating temperature range option

nAvailable in surface mount packaging (SOIC) and (LCC)

nPin compatible with DS26C32A, MB570 (PECL) and

41LF (PECL)

nSupports OPEN, short and terminated input fail-safe

nCompatible with IEEE 1596.3 SCI LVDS standard

nConforms to ANSI/TIA/EIA-644 LVDS standard

nAvailable to Standard Microcircuit Drawing (SMD) 5962-95834

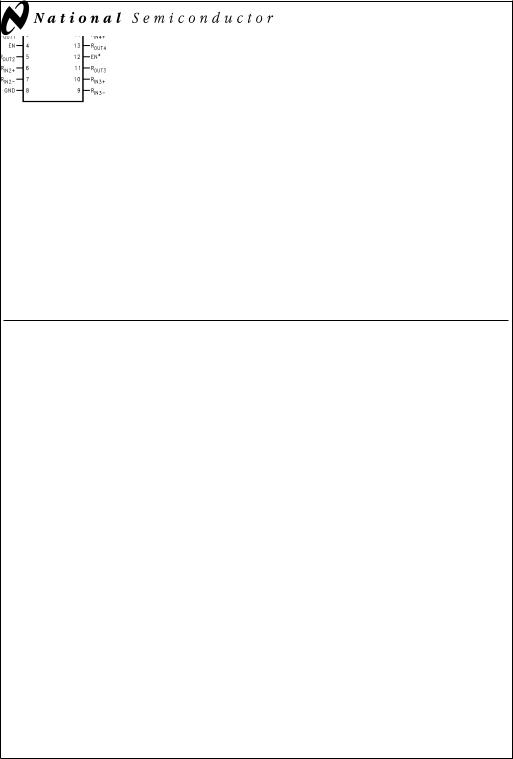

Connection Diagrams

Dual-In-Line |

LCC Package |

DS011945-1

Order Number

DS90C032TM

See NS Package Number M16A

DS011945-20

Order Number

DS90C032E-QML

See NS Package Number E20A For complete Military Specifications,

refer to appropriate SMD or MDS.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

Receiver Line Differential CMOS Quad LVDS DS90C032

© 1998 National Semiconductor Corporation |

DS011945 |

www.national.com |

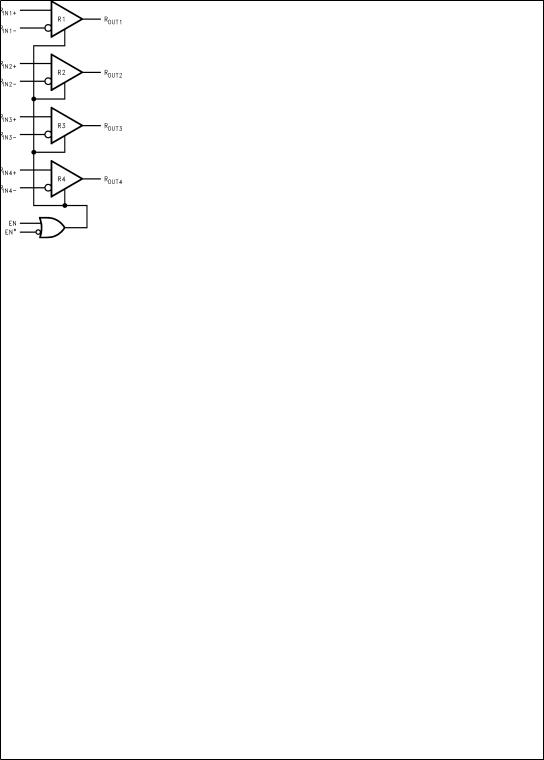

Functional Diagram and Truth Tables

|

|

|

|

DS011945-2 |

|

RECEIVER |

|

|

|

||

|

|

|

|

|

|

|

ENABLES |

|

INPUTS |

OUTPUT |

|

|

|

|

|

|

|

|

EN |

|

EN* |

RIN+ − R IN− |

ROUT |

|

L |

|

H |

X |

Z |

|

|

|

|

|

|

|

All other combinations |

VID ³ 0.1V |

H |

||

|

of ENABLE inputs |

|

VID £ −0.1V |

L |

|

|

|

|

|

Full Fail-safe |

H |

|

|

|

|

OPEN/SHORT |

|

|

|

|

|

|

|

|

|

|

|

or Terminated |

|

|

|

|

|

|

|

www.national.com |

2 |

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (VCC) |

−0.3V to +6V |

Input Voltage (RIN+, RIN− ) |

−0.3V to (V CC +0.3V) |

Enable Input Voltage |

|

(EN, EN*) |

−0.3V to (V CC +0.3V) |

Output Voltage (ROUT) |

−0.3V to (V CC +0.3V) |

Maximum Package Power Dissipation @ +25ÊC |

|

M Package |

1025 mW |

E Package |

1830 mW |

Derate M Package |

8.2 mW/ÊC above +25ÊC |

Derate E Package |

12.2 mW/ÊC above +25ÊC |

Storage Temperature Range |

−65ÊC to +150ÊC |

Lead Temperature Range |

|

Soldering (4 sec.) |

+260ÊC |

Maximum Junction |

|

Temperature (DS90C032T) |

+150ÊC |

Maximum Junction |

|

Temperature (DS90C032E) |

+175ÊC |

ESD Rating (Note 7) |

|

(HBM, 1.5 kW, 100 pF) |

³ 3,500V |

(EIAJ, 0 W, 200 pF) |

³ 250V |

Recommended Operating

Conditions

|

Min |

Typ |

Max |

Units |

Supply Voltage (VCC) |

+4.5 |

+5.0 |

+5.5 |

V |

Receiver Input Voltage |

GND |

|

2.4 |

V |

Operating Free Air Temperature (TA) |

|

|

||

DS90C032T |

−40 |

+25 |

+85 |

ÊC |

DS90C032E |

−55 |

+25 |

+125 |

ÊC |

Electrical Characteristics

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified. (Note 2)

Symbol |

Parameter |

Conditions |

|

Pin |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

|

|

VTH |

Differential Input High Threshold |

VCM = +1.2V |

|

RIN+, |

|

|

+100 |

mV |

VTL |

Differential Input Low Threshold |

|

|

RIN− |

−100 |

|

|

mV |

IIN |

Input Current |

VIN = +2.4V |

VCC = 5.5V |

|

−10 |

±1 |

+10 |

µA |

|

|

VIN = 0V |

|

|

−10 |

±1 |

+10 |

µA |

VOH |

Output High Voltage |

IOH = −0.4 mA, V ID = +200 mV |

ROUT |

3.8 |

4.9 |

|

V |

|

|

|

IOH = −0.4 mA, |

DS90C032T |

|

3.8 |

4.9 |

|

V |

|

|

Input terminated |

|

|

|

|

|

|

VOL |

Output Low Voltage |

IOL = 2 mA, VID = −200 mV |

|

|

|

0.07 |

0.3 |

V |

IOS |

Output Short Circuit Current |

Enabled, VOUT = 0V (Note 8) |

|

−15 |

−60 |

−100 |

mA |

|

IOZ |

Output TRI-STATE Current |

Disabled, VOUT = 0V or VCC |

|

|

−10 |

±1 |

+10 |

µA |

VIH |

Input High Voltage |

|

|

EN, |

2.0 |

|

|

V |

VIL |

Input Low Voltage |

|

|

EN* |

|

|

0.8 |

V |

II |

Input Current |

|

|

|

−10 |

±1 |

+10 |

µA |

VCL |

Input Clamp Voltage |

ICL = −18 mA |

|

|

−1.5 |

−0.8 |

|

V |

ICC |

No Load Supply Current |

EN, EN* = VCC or GND, |

DS90C032T |

VCC |

|

3.5 |

10 |

mA |

|

Receivers Enabled |

Inputs Open |

DS90C032E |

|

|

3.5 |

11 |

mA |

|

|

|

|

|

|

|

|

|

|

|

EN, EN* = 2.4 or 0.5, Inputs Open |

|

|

3.7 |

11 |

mA |

|

|

|

|

|

|

|

|

|

|

ICCZ |

No Load Supply Current |

EN = GND, EN* = VCC |

DS90C032T |

|

|

3.5 |

10 |

mA |

|

Receivers Disabled |

Inputs Open |

DS90C032E |

|

|

3.5 |

11 |

mA |

|

|

|

|

|

|

|

|

|

3 |

www.national.com |

Switching Characteristics

VCC = +5.0V, TA = +25ÊC DS90C032T (Notes 3, 4, 5, 9)

Symbol |

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

tPHLD |

Differential Propagation Delay High to Low |

CL = 5 pF |

1.5 |

3.40 |

5.0 |

ns |

tPLHD |

Differential Propagation Delay Low to High |

VID = 200 mV |

1.5 |

3.48 |

5.0 |

ns |

tSKD |

Differential Skew |tPHLD − t PLHD| |

(Figure 1 and Figure 2) |

0 |

80 |

600 |

ps |

tSK1 |

Channel-to-Channel Skew (Note 5) |

|

0 |

0.6 |

1.0 |

ns |

tTLH |

Rise Time |

|

|

0.5 |

2.0 |

ns |

tTHL |

Fall Time |

|

|

0.5 |

2.0 |

ns |

tPHZ |

Disable Time High to Z |

RL = 2 kΩ |

|

10 |

15 |

ns |

tPLZ |

Disable Time Low to Z |

CL = 10 pF |

|

10 |

15 |

ns |

tPZH |

Enable Time Z to High |

(Figure 3 and Figure 4) |

|

4 |

10 |

ns |

tPZL |

Enable Time Z to Low |

|

|

4 |

10 |

ns |

Switching Characteristics

VCC = +5.0V ± 10%, TA = −40ÊC to +85ÊC DS90C032T (Notes 3, 4, 5, 6, 9)

Symbol |

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

tPHLD |

Differential Propagation Delay High to Low |

CL = 5 pF |

1.0 |

3.40 |

6.0 |

ns |

tPLHD |

Differential Propagation Delay Low to High |

VID = 200 mV |

1.0 |

3.48 |

6.0 |

ns |

tSKD |

Differential Skew |tPHLD − t PLHD| |

(Figure 1 and Figure 2) |

0 |

0.08 |

1.2 |

ns |

tSK1 |

Channel-to-Channel Skew (Note 5) |

|

0 |

0.6 |

1.5 |

ns |

tSK2 |

Chip to Chip Skew (Note 6) |

|

|

|

5.0 |

ns |

tTLH |

Rise Time |

|

|

0.5 |

2.5 |

ns |

tTHL |

Fall Time |

|

|

0.5 |

2.5 |

ns |

tPHZ |

Disable Time High to Z |

RL = 2 kΩ |

|

10 |

20 |

ns |

tPLZ |

Disable Time Low to Z |

CL = 10 pF |

|

10 |

20 |

ns |

tPZH |

Enable Time Z to High |

(Figure 3 and Figure 4) |

|

4 |

15 |

ns |

tPZL |

Enable Time Z to Low |

|

|

4 |

15 |

ns |

Switching Characteristics

VCC = +5.0V ± 10%, TA = −55ÊC to +125ÊC DS90C032E (Notes 3, 4, 5, 6, 9, 10)

Symbol |

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

tPHLD |

Differential Propagation Delay High to Low |

CL = 20 pF |

1.0 |

3.40 |

8.0 |

ns |

tPLHD |

Differential Propagation Delay Low to High |

VID = 200 mV |

1.0 |

3.48 |

8.0 |

ns |

tSKD |

Differential Skew |tPHLD − t PLHD| |

(Figure 1 and Figure 2) |

0 |

0.08 |

3.0 |

ns |

tSK1 |

Channel-to-Channel Skew (Note 5) |

|

0 |

0.6 |

3.0 |

ns |

tSK2 |

Chip to Chip Skew (Note 6) |

|

|

|

7.0 |

ns |

tPHZ |

Disable Time High to Z |

RL = 2 kΩ |

|

10 |

20 |

ns |

tPLZ |

Disable Time Low to Z |

CL = 10 pF |

|

10 |

20 |

ns |

tPZH |

Enable Time Z to High |

(Figure 3 and Figure 4) |

|

4 |

20 |

ns |

tPZL |

Enable Time Z to Low |

|

|

4 |

20 |

ns |

www.national.com |

4 |

Loading...

Loading...